Design of a Simple Customizable Microprocessor

60 likes | 176 Views

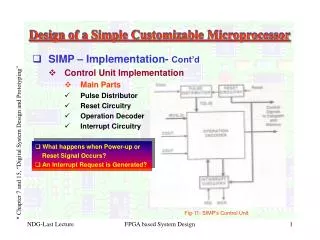

This document details the design and implementation of a simple, customizable microprocessor known as the SIMP. It covers the critical components, including the control unit, pulse distributor, reset circuitry, operation decoder, and interrupt circuitry. The implementation is based on FPGA technology and references foundational concepts from "Digital System Design and Prototyping" (Chapters 7 and 15). Key insights are provided regarding power-up/reset signals and interrupt requests, illustrated through various figures. The guide aims to assist in achieving success in the ASIC/FPGA design field.

Design of a Simple Customizable Microprocessor

E N D

Presentation Transcript

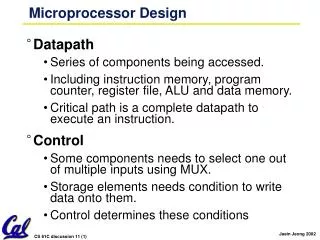

Design of a Simple Customizable Microprocessor • SIMP – Implementation- Cont’d • Control Unit Implementation • Main Parts • Pulse Distributor • Reset Circuitry • Operation Decoder • Interrupt Circuitry * Chapter 7 and 15, “Digital System Design and Prototyping” • What happens when Power-up or Reset Signal Occurs? • An Interrupt Request is Generated? Fig-11: SIMP’s Control Unit FPGA based System Design

Design of a Simple Customizable Microprocessor • SIMP – Implementation- Cont’d • Control Unit Implementation – Cont’d • Pulse Distributor always @(ff) begin case (ff) 2'b00: T = 4'h1; 2'b01: T = 4'h2; 2'b10: T = 4'h4; 2'b11: T = 4'h8; default: T = 4'h1; endcase end endmodule module pulsdist(T, clk, clr, ena); output [3:0] T; input clk, clr, ena; reg [1:0] ff; reg [3:0] T; always @(posedge clk) begin if (clr) ff <= 2'd0; else if (ena) ff <= ff + 1; end * Chapter 7 and 15, “Digital System Design and Prototyping” Fig-12: Pulse Distributor FPGA based System Design

Design of a Simple Customizable Microprocessor • SIMP – Implementation- Cont’d • Control Unit Implementation – Cont’d • Operation Decoder * Chapter 7 and 15, “Digital System Design and Prototyping” Fig-14: Operation Decoder FPGA based System Design

Design of a Simple Customizable Microprocessor • SIMP – Implementation- Cont’d • Control Unit Implementation – Cont’d • Reset Circuitry • Interrupt Circuitry * Chapter 7 and 15, “Digital System Design and Prototyping” Fig-15: Reset Circuit FPGA based System Design

Design of a Simple Customizable Microprocessor • SIMP – Implementation- Cont’d • Control Unit Implementation – Cont’d • Control Unit - Overall * Chapter 7 and 15, “Digital System Design and Prototyping” Fig-16: Control Unit FPGA based System Design

I WishYouAll VerySuccessful Carrierin ASIC/FPGADesignField! FPGA based System Design