第四节 模型机设计

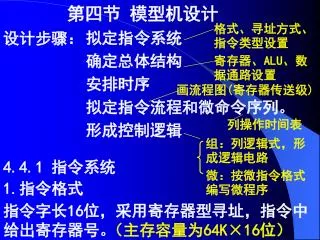

第四节 模型机设计. 格式、寻址方式、指令类型设置. 设计步骤:. 拟定指令系统 确定总体结构 安排时序 拟定指令流程和微命令序列。 形成控制逻辑. 寄存器、 ALU 、数据通路设置. 画流程图 ( 寄存器传送级 ). 列操作时间表. 组:列逻辑式,形成逻辑电路. 4.4.1 指令系统. 微:按微指令格式编写微程序. 1. 指令格式. 指令字长 16 位,采用寄存器型寻址,指令中给出寄存器号。. (主存容量为 64K×16 位). 双操作数指令格式:. 操作码 寄存器号 寻址方式 寄存器号 寻址方式.

第四节 模型机设计

E N D

Presentation Transcript

第四节 模型机设计 格式、寻址方式、指令类型设置 设计步骤: 拟定指令系统 确定总体结构 安排时序 拟定指令流程和微命令序列。 形成控制逻辑 寄存器、ALU、数据通路设置 画流程图(寄存器传送级) 列操作时间表 组:列逻辑式,形成逻辑电路 4.4.1 指令系统 微:按微指令格式编写微程序 1.指令格式 指令字长16位,采用寄存器型寻址,指令中给出寄存器号。 (主存容量为64K×16位)

双操作数指令格式: 操作码寄存器号寻址方式寄存器号寻址方式 操作码 (可扩展) 寄存器号 寻址方式 操作码 寄存器号 寻址方式 方式N′Z′V′C′ 4 3 3 3 3 目的地址 源地址 单操作数指令格式: 4 6 3 3 目的地址 转移指令格式: 15 12 11 9 8 6 5 4 3 2 1 0 转移地址 转移条件

2.寻址方式 CPU可编程访问的寄存器: 通用寄存器R、指令计数器PC、堆栈指针SP、程序状态字PSW 寻址方式 编码 助记符 定义 寄存器寻址 000 R (R)为操作数 寄存器间址 001 (R) (R)为操作数地址 自减型寄存器间址 010 -(R) (R)-1为操作数地址 -(SP) (SP)-1为栈顶地址

寻址方式 编码 助记符 定义 (R)为操作数地址, 立即/自增型寄存器间址 011 (R)+ 访问后(R)+1 (SP)+ (SP)为栈顶地址, 出栈后(SP)+1 (PC)+ (PC)为立即数地址, 取数后(PC)+1 变址 101 X(R) (R)+d为有效地址 X(PC) (PC)+d为有效地址 跳步 110 SKP 跳过下条指令执行

3.指令类型 操作码 助记符 含义 用于数传、堆栈、I/O操作 0000 MOV 传送 0001 ADD 加 双操作数指令 0101 EOR 异或 0110 COM 求反 单操作数指令 1011 SR 右移 1100 JMP 转移 1100 RST 返回 1101 JSR 转子

5 4 3 2 1 0 JMP 寄 寻 方式N′Z′V′C′ 0 0 0 0 0 无条件转 转移地址 0 0 0 0 1 无进位转 (C=0) 0 0 0 1 0 无溢出转 (V=0) 0 0 1 0 0 数非零转 (Z=0) 01 0 0 0 数为正转 (N=0) 有进位转 (C=1) 1 0 0 0 1 1 0 0 10 有溢出转 (V=1) 1 0 10 0 数为零转 (Z=1) 110 0 0 数为负转 (N=1) 条件满足,转转移地址;条件不满足,顺序执行。

15 12 11 9 8 6 5 0 RSTSP(SP)+ JSR 寄 寻 方式N′Z′V′C′ 5 4 3 2 1 0 子程序入口 隐含约定:转子时返回地址压栈保存。 4.4.2 CPU总体结构 1.寄存器设置 (1)可编程寄存器(16位) 通用寄存器: R0(000)、R1(001) R2(010)、R3(011)

堆栈指针: SP(100) 指令计数器: PC(111) (可扩展) I N Z V C 程序状态字: PSW(101) 4 3 2 1 0 允许中断(开中断) (2)非编程寄存器(16位) 暂存器C :暂存来自主存的源地址或源数据。 暂存器D :暂存来自主存的目的地址或目的数。 指令寄存器IR :存放现行指令。 地址寄存器MAR 实现CPU与主存的接口 数据寄存器MDR

2.算逻部件设置 (16位) SN74181 4片 SN74182 1片 选择器A 选择器B ALU 选择数据来源 移位器 :实现直送、左移、右移、字节交换 3.数据通路结构 为了使数据传送控制简单、集中,采用以 ALU为中心的总线结构。 (1)组成 包括四个部分: ALU部件、寄存器组、内总线、CPU与系统总 线的连接

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW (2)特点 ALU为内部数据传送通路的中心; 寄存器采用 分立结构; 内总线采用单向数据总线(16位);

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW 从内总线输入 (打入) 与系统总线 的连接通过 MAR、MDR实现。 输入 从DB输入 (置入) MDR 输出至DB 输出 输出至ALU的B门

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW 4.各类信息传送途径 置入 (1)指令信息 M DB IR (2)地址信息

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW 打入 1)指令地址 PC A ALU 内 MAR 移 2)指令地址加1 PC A ALU 内 PC 移 打入 C0

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW 3)转移地址 打入 PC R0 B ALU 内 移 寄存器寻址: 打入 MAR 寄存器间址: R0 B ALU 内 移 置入 AB M DB MDR B ALU PC 移、 内

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW 4)操作数地址 打入 MAR R0 寄存器间址: B ALU 内 移

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW 变址: PC A ALU 内 MAR AB M 移 M DB MDR B ALU C 内 移 A R0 ALU MAR 移 内 C B

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW R: R: M: 2)R 1)R 3)M (3)数据信息 打入 R1 R0 B ALU 内 移 打入 R0 B ALU MDR DB M 内 M DB MDR B ALU R2 移、 内

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW M: 4)M I/O: 5)R 打入 M(源) DB MDR ALU 内 C C ALU MDR DB M 内 (计算目的地址) (目的) R0 ALU MDR DB I/O 内

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW 6)I/O R 7)I/O M 打入 I/O DB MDR ALU 内 R0 DMA方式: I/O DB M

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW R0 R0 A、 B、 5.微命令设置 ALU输入选择: ALU功能选择: S3S2S1S0、M、C0 (1)数据通路 操作: 输出移位选择: 不移、左移、 结果分配: CPR0、CPC、CPMAR、

AB 内总线 DB CB 移位器 R0 MAR M I/O ALU R1 MDR R2 IR A B 控制逻辑 R3 PC R0~R3 R0~R3 C D C D SP PC PSW MDR C SP D PSW 1 MAR向AB送地址 地址使能 EMAR 0 MAR与AB断开 读 R (2)访M、I/O 操作: 00 MDR与DB断开, R=1读W=1写 写 W 置入MDR SMDR, 置入IR SIR

4.4.3 组合逻辑控制器设计 1.时序系统 (1)工作周期 取指周期FT 源周期ST 用于指令正常执行 目的周期DT 执行周期ET 中断周期IT 用于I/O传送控制 DMA周期DMAT 1工作周期开始 设置6个触发器分别 作为各周期状态标志 0工作周期结束 在整个指令周期中,任何时候必须、且只能有一 个工作周期状态标志为“1”。

1)取指周期FT 从M取出指令并译码; 修改PC。 公操作 取指结束时,按操作码和寻址方式(R/非R寻址) 转相应工作周期。 2)源周期ST 按寻址方式(非R寻址)形成源地址,从M取出源操 作数,暂存于C。 3)目的周期DT 按寻址方式(非R寻址)形成目的地址,或从M取出 目的操作数,暂存于D。 4)执行周期ET 按操作码完成相应操作(传送、运算、取转移地址 送入PC、返回地址压栈保存); 后续指令地址送入MAR。

5)中断周期IT IT指CPU响应中断请求后,到执行中断服务程序前。 关中断、保存断点和PSW、转服务程序入口。 由硬件完成 6)DMA周期DMAT DMAT指CPU响应DMA请求后,到传送完一次数据。 DMA控制器接管总线权,控制直传。 由硬件完成 (2)时钟周期(节拍)T 1)时钟周期时间: 1微秒 完成一步操作: 一次从M读出,并经数据通路传送的操作;或 一次数据通路传送操作;或 一次向M写入的操作 模型机以访存时间作为一步操作时间。 一个总线 周期等于一个时钟周期,可根据需要扩展。

2)时钟周期数: 一个工作周期中的时钟数可变。 每个工作周期第一拍T=0, 每开始一个新节拍T计数, 工作周期结束时T清0。 用计数器T控制节拍数 将计数值译码,可产生节拍电位。 (3)工作脉冲P 每个时钟结束时设置一个脉冲。 1µS T P 打入寄存器 进行时序转换 (周期状态设置/清除 时钟T计数/清除)

2.控制流程(工作周期转换) SR DR DMA请求? 中断请求? FT 单 SR 双 转 ST DR DT ET N N Y Y DMAT IT

3.指令流程图与操作时间表 Q Q S R FT D C 总清 1 FT 拟定指令流程: 确定各工作周期中每拍完成的具体 操作(寄存器传送级)。 列操作时间表: 列出每一步操作所需的微命令及产 生条件。 (1)取指周期FT 1 1)进入FT的方式 初始化时置入FT, 程序正常运行时同步打入FT。 CPFT

2)流程图 M IR M IR PC+1 PC PC+1 PC CPT ( P) CPET( P) CPDT( P) CPST( P) CPFT( P) PC A, 1 ST 1 DT 1 ET FT0: 3)操作时间表 FT0: 电位型微命令 脉冲型微命令 EMAR, R, SIR A+1, DM CPPC 或 或 转换 工作周期中,每拍结束时发CPT;工作周期结束时, 5个时序打入命令都发。

(2)传送指令 M IR M IR, M IR, PC+1 PC PC+1 PC PC+1 PC R1 MAR R0 MAR R1 R0 PC MAR PC MAR M MDR C C MDR MDR M 1)流程图 例1: MOV R0,R1; FT0: ET0: ET1: 例2: MOV(R0),(R1); FT0: ST0: 源数 ST1: 目的地址 DT0: ET0: ET1: ET2: 例3: MOV X(R0),X(R1); FT0:

M IR PC+1 PC PC+1 PC PC+1 PC D+R0 MAR C+R1 MAR PC MAR PC MAR PC MAR C MDR M MDR C M MDR D M MDR C MDR M 例3: MOV X(R0),X(R1); FT0: 形地 ST0: ST1: 取源操作数, 暂存于C, 需5步。 ST2: 源数 ST3: ST4: 形地 DT0: 取目的地址, 暂存于MAR, 需4步。 DT1: 目的地址 DT2: DT3: ET0: 源数送存储器, 需3步。 ET1: ET2:

2)操作时间表 M IR SP+1 SP PC+1 PC SP A SP A PC A CPET(P) CPFT(P) CPFT(P) CPET(P) CPT(P) CPT(P) CPT(P) CPT(P) SP MAR MDR B M MDR C 1 ST 1 DT 例: MOV (R1),(SP)+; FT0: EMAR R SIR A+1 DM CPPC ST0: 输出A DM CPMAR T+1 ST1: EMAR R SMDR 输出B DM CPC T+1 ST2: A+1 DM CPSP

MDR M C MDR R1 A PC A CPET(P) CPFT(P) CPET(P) CPFT(P) CPT(P) CPT(P) CPT(P) CPT(P) R1 MAR PC MAR 1 FT 1 ET C B DT0: 输出A DM CPMAR ET0: 输出B DM CPMDR T+1 ET1: EMAR W T+1 ET2: 输出A DM CPMAR

M IR, PC+1 PC PC MAR PC MAR 例: ADD X(R1),(PC)+ ; M MDR D M MDR C M MDR D MDR M C+D MDR D+R1 MAR PC+1 PC PC+1 PC PC MAR (3)双操作数指令 取目的数,暂存于D。 FT0: 立即数 DT3: ST0: ST1: DT4: 目的数 ST2: ET0: DT0: 形式地址 ET1: DT1: ET2: DT2:

(4)单操作数指令 M IR, PC+1 PC R0-1 R0 PC MAR M MDR D D MDR MDR M 例: COM -(R0); FT0: DT0: 、MAR DT1: ET0: ET1: ET2: (5)转移-返回指令 SKP 执行再下条指令。 R 从R取转移地址。 无条件转移 (R) 按R指示从M取转移地址。 (R)+ 按R指示从M取转移地址,修改R。 (SP)+ 从堆栈取返回地址,修改SP。 (RST) X(PC) 以PC內容为基准转移。

例1: JMP R0; FT0: M IR, M IR, M IR, PC+1 PC PC+1 PC PC+1 PC PC+C PC SP+1 SP PC MAR SP MAR R0 PC M MDR C M MDR PC ET0: 、MAR 例2: RST (SP)+; FT0: ET0: ET1: ET2: 、MAR 例3: JMP X(PC); FT0: ET0: 位移量 ET1: ET2: 、MAR (5)转子指令 无条件转子: R (R) (R)+ (PC)+ (SP)+ 入口在R中 入口在M中 入口在堆栈中

M IR, PC+1 PC SP-1 SP PC MDR R2 MAR MDR M C PC +MOV(ST2+DT2) X P M MDR C 在ST形成子程序入口;在ET保存返回地址,并转 子程序入口。 例: JSR(R2); FT0: ST0: 子程序入口 ST1: ET0: 、MAR 返回地址压栈 ET1: ET2: ET3: 、MAR 4.控制逻辑 归纳微命令,综合化简条件,用组合逻辑电路实现。 例: 读令R= FT0 +MOV(ST1+ST4+……) +…… CPPC = FT0 P +……

4.4.4 微程序控制器设计 1.时序系统 二级时序: 微指令周期 P 微指令 打入 µIR 结果打 入目的 地, 读取后续 微指令 控制数 据通路 操作 后续微 地址打 入 µAR

2.微指令格式 AI BI SM C0 S ZO EMAR R W ST SC PC A Ri A D A C A 按数据通路各段操作划分字段,同类操作中互斥 的微命令放同一字段。 (1)格式 3 3 5 2 2 3 1 1 1 2 4 数据通路操作 访存操作 顺序控制 辅助操作 (2)各字段功能 R0~R3、SP、PC 1)数据通路操作 AI: A输入选择 000无输入 011 001 100 010

MDR B 3 3 5 2 2 3 1 1 1 2 4 AI BI SM C0 S ZO EMAR R W ST SC Ri B D B C B BI: B输入选择 000无输入 011 001 100 010 R0~R3、PSW SM: ALU功能选择 S3S2S1S0M C0: 初始进位选择 S: 移位选择 R0~R3、SP、PC、PSW CPRi ZO: 结果分配 001 2)访存操作 EMAR、R、W 3)辅助操作 00 无操作 10关中断 01开中断 11 SIR

3 3 5 2 2 3 1 1 1 2 4 AI BI SM C0 S ZO EMAR R W ST SC 4)顺序控制 增量 断定 9种 指明微地址形成方式 SC: 0000顺序执行 增量 0001无条件转移 0010按操作码分支 断定 0111转微子程序 增量 1000返回微主程序 3.微程序的编制 (1)编写顺序

按指令执行顺序编写: 取机器指令 功能转移 执行 按操作码编码顺序,逐级分类编写: MOV指令、 双操作数指令、 单操作数指令、 转移指令 (2)实现分支 将同类断定依据所对应的微地址放在相应的微地址 形成表中,用SC字段选取。(见教材P161~P163) SC=0000 顺序执行 现行微地址+1 SC=0001 无条件转 现行微指令给出转移微地址 SC=0111 转微子程序 现行微指令给出微子程序 入口 返回微主程序 从寄存器取返回微地址 SC=1000

按操作码 DR分支(24路)进入执行 MOV DR MOV DR 微地址形成表: 按操作码分支(4路) SC=0010 表内单元地址 (断定依据): 单元内容 (微地址) MOV 03H 取源数、目的地 双 0CH 取源数、目的数 单 24H 取目的数 JMP/JSR 3FH 按J、PC分支 SC=0011 06H 0AH 执行规定操作 后转取指入口 双 单 3DH

M IR: 40H 46H 顺序/转移地址 PC 4DH 5EH 3 3 5 2 2 3 1 1 1 2 4 AI BI SM C0 S ZO EMAR R W ST SC SC=0100 按J、PC分支(4路) SC=0101 按源寻址方式分支(7路) SC=0110 按目的寻址方式分支 从60H开始 (3)微指令实例 1)取指微指令代真 微地址00 000 000 00000 00 00 000 1 1 0 11 0000

PC+1 PC: 3 3 5 2 2 3 1 1 1 2 4 AI BI SM C0 S ZO EMAR R W ST SC 02 00 09 01 4C 4E 03 04 60 05 0A 0B 08 4F 微地址01 100 00010010 01 00 111 0 0 0 00 0000 微地址02 按操作码分支: 000 00000000 00 00 000 0 0 0 00 0010 2)机器指令的微程序实现 例:MOV R1,(R0);按流程写出微地址 00

本章小结 逻辑组成 1、建立CPU整机概念 工作机制 (1)逻辑组成 寄存器、ALU设置,数据通路结构 (旧5.4.2,新3.4.3 ) 寄存器传送级: 各类指令的流程 指令的执行过程 (2)工作机制 微操作控制级: 微命令序列 拟定流程的关键:清楚了解数据通路结构 (旧5.5.2,新3.5.2 ) 熟练掌握基本寻址方式

基本寻址方式(模型机): 寄存器寻址 : R 寄存器间址 :(R) 自减型寄存器间址 :–(R) –(SP)(用于入栈操作) 自增型寄存器间址 :(R)+ (SP)+(用于出栈操作) 立即寻址 : (PC)+ 变址: X(R) 相对寻址 : X(PC) (旧5.4.1,新3.4.2 )

2、有关的基本概念 (1) 微命令的产生方式 组合逻辑控制方式: 基本思想 、优缺点、应用场合 (旧5.5.4,新3.1.3、 3.5.3 ) 微程序控制方式: 基本思想 、优缺点、应用场合 (旧5.6.1、 5.8.1 ,新3.1.3、 3.6.4 )

(2) 时序控制方式 同步控制方式 : 定义、特点、应用场合 异步控制方式: 定义、特点、应用场合 主设备、从设备 (旧5.3.1,新3.1.2 ) (3) 主机与外设的信息传送控制方式 中断方式: 定义 、流程、应用场合 DMA方式: 定义 、流程、应用场合 (旧5.2.2,新3.1.4 )

第四章复习提纲 1.四种运算方法(原码一位乘、补码一位乘、原码 加减交替除法、补码加减交替除法)的算法、规则。 2.浮点加减运算流程。 3.CPU组成(重在数据通路结构)。 4.指令流程(寄存器传送级),操作时间表(微命令序列)。 5.微指令设计方法(分段原则、各段功能、编码方法)。 6.基本概念:溢出及判断方法,数的补码表示及变补, 对阶,规格化,同步控制与异步控制(含义、应用场合), 组合逻辑控制与微程序控制(基本思想、优缺点、应用场 合),I/O传送控制方式(定义、应用场合),控制字,状态 字,程序状态字,主设备,从设备……等。

第四章作业(二) 1、分别写出下述指令流程: (1) MOV R2,(SP)+ ; (2)ADD X(PC),R1 ; (3)JMP (R0); 2、列出指令JMP (R0);的取指周期和 执行周期的操作时间表。假定执行周期 结束后将进入新的取指周期。