ALICE

ALICE. Status of the Readout Electronics for the HMPID ALICE Jose C. DA SILVA. Introduction. RCB controller and DDL (SIU-DDU-PRORC) Column Controller updates (Pedestals Readback, Trigger Inhibit, etc) Busy Signal, (NIM Logic). HMPID overview. fbD[27..0]. fbD[31..0]. VME to

ALICE

E N D

Presentation Transcript

ALICE • Status of the Readout Electronics for the HMPID ALICE Jose C. DA SILVA

Introduction • RCB controller and DDL (SIU-DDU-PRORC) • Column Controller updates (Pedestals Readback, Trigger Inhibit, etc) • Busy Signal, (NIM Logic)

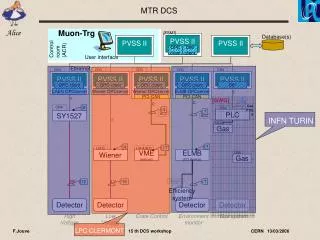

HMPID overview fbD[27..0] fbD[31..0] VME to Local Bus Interface LOC_ADD[11..0] LOC_ADD[3..0] DILO 5 Boards (ADC and DILOGIC) Column Controller (1 to 8) Segment Controller LOC_CS LOC_CS LOC_R/Wn LOC_R/Wn FE Boards (gassiplex) RCB BOARD SEGMENT

HMPID overview fbD[27..0] fbD[31..0] fbD[31..0] DDL SIU LINK SIU Control LOC_ADD[11..0] LOC_ADD[3..0] DILO 5 Boards (ADC and DILOGIC) Column Controller (1 to 8) Segment Controller HMPID DDL Controller LOC_CS LOC_CS TTC Bus LOC_R/Wn LOC_R/Wn TTC_RX L2 BUSY FE Boards (gassiplex) RCB BOARD SEGMENT

Readout and Control Board • Embedded Controller that interfaces the DAQ link and the Segment Controllers. • >Modify all the interface method with the Segments and Columns • Monitors the Segment and Link Status, stores the L1A informations, decodes the L2A via the TTC-Rx Broadcast bus and builds the event for the data selected at each L2A. • L0, L1 and L2 NIM inputs (while no TTC system) • Busy signal out (NIM logic, LVDS) . • The RCB Interface houses a TTC_rx and a SUI Link board, and logic level converters (NIM-TTL-NIM). • >TTC emulation while no TTC system

RCB Controller • Main components of the RCB controller embedded on the ALTERA: • Controller, basically a set of 2 synchronous state machines • one SM running at 40MHz for SIU interface • one SM running at 10MHz for Segment Interface • TTC_Rx emulator (Event Number and Bx Number) • LHC structured counters • Data FIFO , Controlled by both SM. • HEADER builder • Busy signal.

Segment Controller • This controller interfaces with the RCB controller via a specific “local interface”, fully synchronous. • Allows a perfect modularity and repeatability of the design of the segment PCB’s. • Controls the bus access for the selected Column on each Segment. • Global signals fanout (Reset, Clock, Busy)

Column Controller • Self clock generator, Column setup functions (read, write and bypass selection) Gassiplex and Dilogic setup (track and hold, dilo and gassiplex phased clocks,), read and write of the Dilogics Data trough bi-directional FIFO’s, and interface with the Segment Controller. • Programmable features: • Number of Clocks (16, 32, 48, 64) • Clock Frequency (10, 8, 5, 1.25 MHz) • Dilogic Channel Bypass

Test Beam 2003 • DDL Link (hardware and software) • Full Equipped Segment Board • 8 columns and 16 MCM Cards • Full Control and Readout of all modules