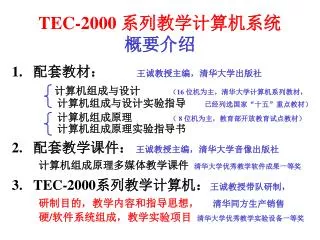

TEC-2000 系列教学计算机系统 概要介绍

1k likes | 1.16k Views

TEC-2000 系列教学计算机系统 概要介绍. 配套教材: 王诚教授主编,清华大学出版社 计算机组成与设计 ( 16 位机为主,清华大学计算机系列教材, 计算机组成与设计实验指导 已经列选国家“十五”重点教材) 计算机组成原理 ( 8 位机为主,教育部开放教育试点教材) 计算机组成原理实验指导书 配套教学课件: 王诚教授主编,清华大学音像出版社

TEC-2000 系列教学计算机系统 概要介绍

E N D

Presentation Transcript

TEC-2000 系列教学计算机系统概要介绍 配套教材: 王诚教授主编,清华大学出版社 计算机组成与设计 (16 位机为主,清华大学计算机系列教材, 计算机组成与设计实验指导 已经列选国家“十五”重点教材) 计算机组成原理 ( 8 位机为主,教育部开放教育试点教材) 计算机组成原理实验指导书 配套教学课件:王诚教授主编,清华大学音像出版社 计算机组成原理多媒体教学课件 清华大学优秀教学软件成果一等奖 TEC-2000系列教学计算机:王诚教授带队研制, 研制目的,教学内容和指导思想, 清华同方生产销售 硬/软件系统组成,教学实验项目 清华大学优秀教学实验设备一等奖

计算机的系统结构、组成与实现 计算机系统结构,程序设计者所看到的计算机系统的属性,是计算机的外特性,概念性结构和功能特性,研究计算机系统的硬、软件的功能划分和接口关系。 计算机组成,计算机各功能部件的内部构造和相互之间的联系(部件配置、相互连接和作用),强调各功能部件的性能参数相匹配;实现机器指令级的各种功能和特性,是计算机系统结构的逻辑实现。 计算机实现,计算机组成的物理实现,即把一台完成逻辑设计的计算机真正地制作出来,解决各部件的物理结构,器件选择,电源供电、通风与冷却、装配与制造工艺等各个方面的问题。 三者各自包括不同内容,彼此又有密切的联系。

一. 教学计算机系统的研制目的(1) 为了更好地贯彻理论联系实际要求,也为了更好地培养学生的实验动手能力和创新意识,我们专门研制出 8 位和 16 位两种字长, 硬、软件配置比较合理的教学计算机系统,既为计算机组成原理课讲课提供了实例内容,又为教学实验解决了实验设备, 这是课程教学改革的重要举措。 几年来我们总结自己的教学实践经验和该教学计算机在全国推广应用的效果已充分证明,学好用好这台计算机的组成与设计知识,对提高课程教学水平很重要。

教学计算机系统的研制目的 (2) 在教学过程中,要讲解计算机组成的基本原理和总体概念,又用教学计算机的组成、设计与实现的具体实例,来深化所学知识。 此外,希望在整个教学过程中,同学对理论联系实际,增强工程观点,培养动手能力和增强创新意识等这样一些问题,有更深切的体会,更加有意识地加强在这样一些方面的锻炼与提高。

二. 教学内容 (1) 教学大纲规定: 讲解单台计算机的完 整硬件系统 的基本组成原理与内部运行机制 单台:非多机系统, 亦非多处理机结构 基本:不一定是最高性能、最合理的组成, 而是最基础的必要的组成部分 完整:计算机整机、全部的硬件功能部件

教学内容 (2) 再详细分一点说,可以分成 3 个层次给出课程的有关知识和技术内容: (1)重点讲解 简单、完整、单台计算机的基本组成原理和内部运行机制, (2)适当说明 当前最流行的一些新计算机中广泛采用的新技术、新工艺, (3)顺便了解 当前国内外计算机组成领域最新研究成果和发展应用趋势。 第一个层次的教学内容属于原理性的基础知识,是重点部分,其特点是内容相对稳定,同学可以动手实践。同学在学习过这些原理知识的基础上,可以通过教学实践环节,完成指定的教学实验题目,或者完成带有一定研究型的工程设计项目来加深对教学内容的理解程度,增长研究、开创性工作、通过实践获取知识的能力,从知识和能力两个方面全面提高学生的素质。 第二个层次体现的是教学内容的先进性,其特点是技术性较强,内容变化相对较快,由于设备条件的限制,同学难以动手实践,更多的是通过课堂教学来学习,并适当布置一些作业,重点锻炼学生的逻辑思维和创新能力。 第三个层次体现的是教学内容的前沿性,其特点是技术性上明显的不成熟性,有些甚至处于原理方案或者还只是一种思路,主要目的在于扩展学生的眼界和思考问题所站的高度。这部分内容不作为评定成绩的必要要求。

计算机硬件系统组成 (1) 包括: 运算器控制器 高速缓存 主存储器 外存设备 输入设备输出设备等几个主要组成部分。 这些设备和部件通过总线和接口连结在一起, • 构成一台完整的计算机,如下图所示:

计算机硬件系统组成 (2) 控 制 器 运 算 器 入出接口和总线 高速缓存 输入设备 主存储器 输出设备 外存设备

计算机硬件系统组成 (3) 运 算 器 运算器部件是计算机中进行数据加工的部件,其主要功能包括: 1. 执行数值数据的算术加、减、乘、除等运算, 执行逻辑数据的与、或、非等逻辑运算, 由一个被称为 ALU 的线路和乘商寄存器完成。 2. 暂时存放参加运算的数据和中间结果, 由多个通用寄存器来承担。 3. 运算器通常也是数据传输的通路 。

计算机硬件系统组成 (4) 控 制 器 运 算 器 控制器是计算机中控制执行指令的部件: 一. 正确执行每条指令 1. 首先是取来一条指令, 2. 接着分析这条指令, 3. 再按指令格式和功能执行这条指令 二. 保证指令按程序中规定的序列自动连续地执行。 三. 对各种异常情况和请求及时响应和处理。 说到底,控制器要向计算机各功能部件提供 每一时刻协同运行所需要的控制信号

计算机硬件系统组成 (5) 控 制 器 运 算 器 由高速缓冲存储器、主存储器、外 存储器所组成的多级(层)存储器系统, 是计算机中用于存储程序和数据的系统。 这三级存储器各自的功能分工、所用的 存储介质的工作原理和特性各不相同。 将作为三个部分分别讲解。 高速缓存 主存储器 外存设备

计算机硬件系统组成 (6) 控 制 器 运 算 器 高速缓存 输入设备 主存储器 输入设备是向计算机中送入程序和数据的、有一定独立功能的设备。 通过 接口 和 总线与计算机主机连通,用于人—机交互联系,如计算机键盘和鼠标等。 外存设备

计算机硬件系统组成 (7) 控 制 器 运 算 器 高速缓存 输入设备 主存储器 输出设备 外存设备 输出设备是计算机中用于送出计算机内部信息的设备,例如打印机、 显示器等。

计算机硬件系统组成 (8) 控 制 器 运 算 器 高速缓存 输入设备 主存储器 输出设备 外存设备 这些部件和设备通过总线和接口连接在一起, 构成计算机整机系统,协同运行。

计算机硬件系统组成 控 制 器 运 算 器 第二单元(18学时) 第一单元(18学时) 入出接口和总线 高速缓存 输入设备 主存储器 输出设备 外存设备 第四单元(12学时) 第三单元(12学时)

三. 教学指导思想 (1) 教学内容强调以计算机硬件部件和整机系统知识为主的同时,还必须适当兼顾与硬件关系最密切的基础软件知识学习。 那种把计算机组成原理完全作为纯硬件课来处理,是陈旧的认识和过时的做法,不符合当今计算机科学研究和教育发展的潮流。 处理好硬、软件相关知识的结合,将有助于提高课程学习的质量和水平。

教学指导思想 (2) 为了更好地做到理论联系实际,更好地培养学生的实验动手能力和创新意识, 我们专门研制出 8 和 16 位的硬、软件配置比较合理,资料相对齐全的教学计算机系统,为讲课提供实例内容, 为教学实验提供实验设备, 有利于更深入地学习计算机各功能部件和整机系统。引入“计算机整机系统的设计与实现工程研究项目”是课程教学改革的重要举措。

四. TEC-2000 教学机系统的组成 电 源 +5V 运算器 (8 / 16 位) 计算机 终端 微程序 控制器 接口实验 中断实验 内存扩展实验 串行接口 主存储器 (8 / 16位) 硬布线 控制器 PC机 按键 开关 指示灯

TEC-2000 机系统概述 TEC-2000 教学计算机系统,在借鉴TEC-2 机已有应用经验的基础上完全重新设计,2000年初完成。 教学机的主要逻辑线路(含扩展实验部分)在一块印制电路板上给出,不再使用外接的 PC 机电源,不必再外接支持扩展实验的几块电路板。成本降低,使用和携带也更方便,TEC-2000 教学计算机的实验性能有很大提高: 可构成 8 位或者 16 位 两种不同字长的机型; 可支持 组合逻辑 和 微程序两种控制器方案; 可选用多种存储器芯片实现内存及容量扩展; 教学实验内容有所增加,实验性能也更强。

运算器 微程序控制器 主振 脉冲 C Z V S 微程序定序器 ALU 程序计数器 控制 存储器 PC R0 操作数 地址 R1 映射 乘商寄存器 寄存器组 指令寄存器 地址寄存器 微指令寄存器 Rn 操作码 IR AR . 下地址字段内容 用于运算器 数据总线 控制总线 地址总线 0 单元 接口 1单元 主存储器 输入设备 输出设备 n单元

运算器 硬布线控制器 主振 脉冲 C Z V S 节拍发生器 ALU 程序计数器 PC R0 控制信号 译码器 操作数 地址 R1 乘商寄存器 产生部件 寄存器组 指令寄存器 地址寄存器 Rn 操作码 AR …. IR 用于运算器 数据总线 控制总线 地址总线 0 单元 接口 1单元 主存储器 输入设备 输出设备 n单元

1. TEC-2000 机的硬件组成 计算机终端 和 PC机 是计算机标准设备,可通过串行接口与 TEC-2000 机接通,作为输入 / 输出设备使用,在监控程序的支持下,可大大提高实验效率和水平。 TEC-2000 机上的 串行接口是该机用于连接输入/输出设备的线路。 CPU实验之外的其他各种扩展操作的实验,如内存容量扩展实验,多级中断实验,并行接口实验,以及其他 I/O 接口实验等,都可以直接在 TEC-2000 机大板右侧的扩展实验区域完成。

2. TEC-2000 机的硬件组成 TEC-2000 机上的按键、开关、指示灯是作为最底层的输入/输出手段使用的部件。 按键 用于启动计算机,执行RESET操作, 控制打入开关拨入的数据或地址, 作为中断源以产生中断请求信号。 开关 用于选择TEC-2000 机的运行方式, 可向机内拨入数据 和 地址等信息, 微型开关用于给出实验控制信号。 指示灯有 超百个,同时显示实验机内的 各种数据、地址和控制信号的状态。

3. TEC-2000 机的硬件组成 TEC-2000 机上的运算器,可选 8 或 16 位字长,分别由 2 或 4 片 4 位的位片结构的器件组成,作为讲解运算器的实例和教学实验的对象,有很强的典型性。它可脱离 TEC-2000 主机,单独地进行运算器部件实验,也可在主机控制下完成运算器部件实验、其它功能部件实验或整机实验。 位片结构是说,每个器件本身就是一个完整的运算器,只是位数较少,要组成更多位数的实用运算器要用多片共同实现,这里选用的是美国AMD公司的 Am2901芯片。

输出Y Am2901内部组成 (无动画) 二选一 /OE F F3 F=0000 OVR Cn+4 A L U S R 组成 算逻运算部件 16 个 累加器 乘商寄存器 Q 功能 8种运算功能 8种数据组合 8种结果处理 Cn 三选一 二选一 输入D B锁存器 A锁存器 乘商寄存器Q A口地址 Q3 Q0 B 16个 A 通用寄存器 三选一 B口地址 三选一 RAM3 RAM0

Am2901芯片是一个 4位的位片结构的运算器器件,其内部组成讲解如下: F 符号位 结果为零 结果溢出 进位输出 F3 F=0000 OVR Cn+4 A L U S R Cn 第一个组成部分是算逻运算部件ALU,完成 3 种算术运算 和 5 种逻辑运算, 共计 8 种功能。 3位功能选择码 8种运算功能 000 001 010 011 100 101 110 111 R+S SR RS R∨S RS RS RS RS 其输出为 F,两路输入为 S、R, 最低位进位Cn,四个状态输出信号如图所示。

第二个组成部分 是通用寄存器组, 由16个寄存器构 成,并通过B口 与A口地址选择 被读的寄存器, B口地址还用于 指定写入寄存器。 F F3 F=0000 OVR Cn+4 A L U S R Cn B锁存器 A锁存器 通过B口地址、 A口地址读出的 数据将送到B、 A锁存器,要写 入寄存器的数据 由一个多路选择 器送来。 A口地址 B 16个 A 通用寄存器 B口地址 (写入)

第三个组成部分 是乘商寄存器Q, 它能对自己的内 容完成左右移位 功能,其输出可 以送往ALU,并 可接收ALU的输 出结果。 F F3 F=0000 OVR Cn+4 A L U S R Cn B锁存器 A锁存器 Q寄存器 A口地址 B 16个 A 通用寄存器 B口地址

一组三选一门和 另一组二选一门 用来选择送向 ALU的 R、S输 入端的数据来源 ,包括Q寄存器、 A口、 B口、外 部输入D数据的 8 种不同组合。 F F3 F=0000 OVR Cn+4 A L U S R Cn 三选一 二选一 输入D B锁存器 A锁存器 Q寄存器 A口地址 该芯片的第四个 组成部分是 5 组 多路选通门,包括 B 16个 A 通用寄存器 8种数据组合(R,S) AQ AB 0Q 0B 0A DA DQ D0 B口地址 3位数据选择码 000 001 010 011 100 101 110 111

一组三选一门 完成把ALU的 输出、或左移 一位、或右移 一位的值送往 通用寄存器组 ,最高、最低 位移位信号有 双向入/出问题 F F3 F=0000 OVR Cn+4 A L U S R Cn 三选一 二选一 输入D 一组三选一门 完成Q寄存器 的左移一位、 或右移一位、 或接收ALU输 出值的功能, 最高、最低位 移位信号有双 向入/出问题。 B锁存器 A锁存器 Q寄存器 A口地址 Q3 Q0 B 16个 A 通用寄存器 三选一 B口地址 三选一 RAM3 RAM0

输出Y 一组二选一门, 选择把A口数据 或ALU结果送出芯片,以给出输出Y的数据,Y输出的有无还受输出使能 /OE信号的控制,仅当 /OE为低是才有Y输出 ,/OE为高,Y输出为高阻态。 二选一 /OE F F3 F=0000 OVR Cn+4 A L U S R Cn 三选一 二选一 输入D B锁存器 A锁存器 Q寄存器 A口地址 Q3 Q0 B 16个 A 通用寄存器 三选一 B口地址 三选一 RAM3 RAM0

8 种结果处理 • 3位控制码 通用寄存器 Q寄存器 Y输出 • 000 QF F • 001 F • 010 BF A • 011 BF F • 100 BF/2 QF/2 F • 101 BF/2 F • 110 B2F Q2F F • 111 B2F F

F=0 F7 Y7~4 OVER Cy 高位 Am2901 Am2901 RAM7 Q7 CP A口 B口 I8~6 I5~3 I2~0 D7~4 8 位教学计算机系统 2 片Am2901之间的连接 Vcc R Y3~0 Cin RAM0 Q0 D3~0

F=0 F15 Y15~12 OVER Cy 高位 Am2901 Am2901 Am2901 Am2901 RAM15 Q15 CP A口 B口 I8~6 I5~3 I2~0 D15~12 16 位教学计算机系统 4 片Am2901之间的连接 Vcc R Y11~8 Y3~0 Y7~4 Cin RAM0 Q0 D3~0 D11~8 D7~4

Am2902 Cn+z Cn+y Cn+x +5V 片间高速进位用 Am2902 Cin F=0 /G /P OVER Y15~12 Y11~8 Y7~4 Y3~0 F15 Cy 高位 Am2901 Am2901 Am2901 低位 Am2901 RAM15 RAM0 Q15 Q0 CP A口 B口 I8~6 I5~3 I2~0 D3~0 D15~12 D11~8 D7~4

TEC-2000的运算器 8 位机,只用 8 位数据线, 只用 2 片Am2901 芯片实现, 写 16 位的地址寄存器操作, 8 位的 ALU 要送2 次数据; 8 位ALU输出经 8 位开关门 → 8 位的内部线 IB, 经 8 位双向三态门→外部总线 ALU接收 8 位开关送数据, 16 位机,使用16 位数据线, 共用 4 片Am2901 芯片实现, 写 16 位的地址寄存器操作, 16 位 ALU 一次送 16 位数据。 16 位ALU 输出经 16 位开关门 →16 位的内部线 IB。 经16 位双向三态门→外部总线 ALU 接收 16 位开关送数据。 2 种机器使用大体相同的 状态寄存器 (FLAG GAL)、 最低位进位信号、高低位移 位信号线路 (SHIFT GAL)。 状态位 C Z V S 和中断优先级 P1、P0 经开关门→内部线IB。

4. TEC-2000 机的硬件组成 TEC-2000 机上的控制器,可用选用组合逻辑或微程序方案实现,非常好地支持动态的指令集合,选用了 美国AMD 公司的 Am2910 芯片作为微程序的下地址形成部件,用来讲解微程序下地址逻辑和教学实验的对象,有很高实用性和典型性。组合逻辑和微程序控制器方案之间可用手拨开关完成切换。 动态的指令集合,是指可以通过修改和增加微程序的内容,或变化可编程器件的内容,来改变计算机已有的指令系统,例如,增加新的指令,变更原有指令等;这对于教学与教学实验的计算机有特别重要的意义。TEC-2000 机在这一方面性能超群。

控制器的功能 计算机的功能是执行程序 程序是依次排列起来的指令代码 控制器的基本功能就在于 正确且自动地连续执行指令 正确地分步完成每一条指令规定的功能 再进一步说, 就是向计算机各功能部件提供 协调运行每一步所需要的控制信号 (还要能及时处理异常情况和紧急请求)

控制器的组成 (1) 程序计数器 PC:存放指令地址,有+1或接收新值功能 (2) 指令寄存器 IR :存放指令内容:操作码与操作数地址 • 主脉冲源与启停控制线路:按需要给出主脉冲信号 (3) 指令执行步骤标记线路: 指明每条指令的执行步骤 (4) 控制信号记忆或产生线路: • 给出计算机各功能部件协同运行所需要的控制信号。 各部件包括 运算器部件 主存储器部件 总线及输入/输出接口(输入/输出设备) 也包括 控制器部件 设计中的难点,在于解决对运算器、控制器的控制

每条指令的执行步骤 一次 读内存 操作 —读取指令 指令地址送入主存地址寄存器 读主存,读出内容送入指定的寄存器 —分析指令 —按指令规定内容执行指令 不同指令的操作步骤数, 和具体操作内容差异很大 —检查有无中断请求 若有,则转中断处理 若无,则 转入下一条指令的执行过程 形成下条指令地址 R—R型指令 读写内存型指令 输入输出型指令 其他类型指令 可能一次 / 多次地 进行操作

控制条件 微程序 方案的 控制器 主振 下地址 部件 控制 存储器 PC 映射 …. 启停 微指令寄存器 IR 下地址 数据总线 控制总线 地址寄存器 地址总线 主 存 储 器 接口 输出 设备 接口 输入 设备 运算器 部件

一个微周期 接收微指令 执行第 i条微指令 形成第 i+1条微指令地址 读出第 i+1条微指令 微程序控制器的运行原理 指令每一个执行步骤用到的全体控制信号组成一微指令 每条指令可以包括一到多个微操作 用多条微指令(一个微程序段)解释每条指令的执行过程 解释全部指令的微程序段的集合构成控制器的微程序 执行一条微指令所用的时间被称为一个微周期。 微指令的格式和内容: 下地址字段 控制命令字段 读与执行微指令的 并行流水技术

下地址字段的内容 在微指令下地址字段中表示清楚: 使用哪种方法, 哪个(些)判断条件, 要用的有关地址等, 并用专门电路完成必要支持和处理, 微指令的下地址是微程序设计中要重点解决的问题之一, 技术、技巧性强, 应学得好些。 得到下地址的方法: 由指令操作码得到 微指令顺序执行 微指令必转或条件转移 多路微地址转移 微子程序调用和返回 按次数循环一段微程序 其他:如特定入口微地址 在教学计算机中,解决下地址使用了 Am2910 器件

微程序控制器部件 56位的微指令字长, 微下地址字段16位, 控制命令字段40位, 7 片 28C64 组成控存。 1 片 28C65,从指令操 作码产生微地址, 1 片 374 存 8 位下地址, 1 片 273 存 8 位条件码, 1 片377存8位现微地址。 1 片Am2910给出下一条 微指令地址, 1 片GAL 按判断条件产 生微指令转移信号/CC; 5 片GAL用作为 5 片 8位 的 D 触发器的寄存器, 2 片GAL 实现两个4 位的 2 选 1 芯片功能。 8 或 16位的指令寄存器。

TEC-2000 16位机基本指令系统 指令格式 汇编语句 操作数个数 CZVS 指令分组 功能说明 00000000 DRSR ADD DR,SR 2 ***** A DR←DR+SR 00000001 DRSR SUB DR,SR 2 ***** A DR←DR-SR 00000010 DRSR AND DR,SR 2 ***** A DR←DR and SR 00000011 DRSR CMP DR,SR 2 ***** A DR-SR 00000100 DRSR XOR DR,SR 2 ***** A DR←DR xor SR 00000101 DRSR TEST DR,SR 2 ***** A DR and SR 00000110 DRSR OR DR,SR 2 ***** A DR←DR or SR 00000111 DRSR MVRR DR, SR 2 • • • • A DR←SR 00001000 DR0000 DEC DR 1 ***** A DR←DR-1 00001001 DR0000 INC DR 1 ***** A DR←DR+1 00001010 DR0000 SHL DR 1 * • • • A DR,C←DR*2 00001011 DR0000 SHR DR 1 * • • • A DR,C←DR /2 01000001 OFFSET JR ADR 1 • • • • A 无条件跳转 01000100 OFFSET JRC ADR 1 • • • • A C=1 时跳转 01000101 OFFSET JRNC ADR 1 • • • • A C=0 时跳转 01000110 OFFSET JRZ ADR 1 • • • • A Z=1 时跳转 01000111 OFFSET JRNZ ADR 1 • • • • A Z=0 时跳转

TEC-2000 16位机基本指令系统 指令格式 汇编语句 操作数个数 CZVS 指令分组 功能说明 10000000 0000000 JMPA ADR 1 • • • • B 无条件跳到ADR ADR(16位) 10000001 DRSR LDRR DR,[SR] 2 • • • • B DR←[SR] 10000010 I/O PORT IN I/O PORT 1 • • • • B R0←[I/O PORT] 10000011 DRSR STRR [DR],SR 2 • • • • B [DR]←SR 10000100 00000000 PSHF 0 • • • • B FLAG 入栈 10000101 0000SR PUSH SR 1 • • • • B SR 入栈 10000110 I/O PORT OUT I/O PORT 1 • • • • B [I/O PORT]←R0 10000111 DR POP DR 1 • • • • B 出栈到 DR 00001000 DR0000 MVRD DR, DATA 2 • • • • B DR←DATA DATA(16位) 10001100 00000000 POPF 1 • • • • B FLAG←出栈 10001111 00000000 RET 1 • • • • B 子程序返回 11001110 00000000 CALA ADR 1 • • • • D 调用子程序 ADR(16位)

/Reset PC 0 AR PC PCPC+1 寄存器之间 运算与传送 A组 B组 IR(AR) AR地址 读、写内存 或 I/O 接口 /MAP B、C、D组 C组 D组 读、写内存 AR地址 读、写内存 PC地址 16 位机的基本指令、扩展指令执行流程图

加电启动时, 执行 0PC 接下来的两步, 完成取指操作 按指令操作码, 读出相应微指令 按指令具体功能, 再分别用 1、2、 3、4 步完成不同 指令组的中各条 指令的执行过程 最后检查中断请 求信号,有请求 时则响应中断, 否则开始下一条 指令的执行过程