Comprehensive Overview of SDRAM Interface and Control in VHDL Modules for Leon Architecture

This document provides a detailed look at the SDRAM interface and control module within the Leon architecture, including various VHDL record definitions for memory input and output types, AHB and APB slave/in master configurations, and debugging signals. It outlines key address and data configurations while highlighting essential components like memory types, control signals, and their respective functionalities. This resource serves as a vital reference for developers engaging with Leon's SDRAM implementation in VHDL, ensuring a deeper understanding of module interconnections and signal management.

Comprehensive Overview of SDRAM Interface and Control in VHDL Modules for Leon Architecture

E N D

Presentation Transcript

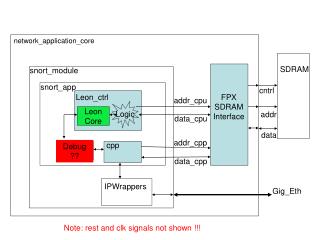

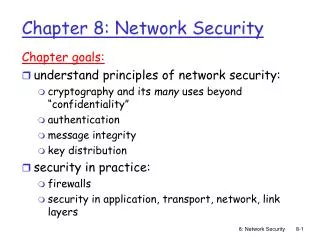

network_application_core SDRAM snort_module snort_app cntrl Leon_ctrl FPX SDRAM Interface addr_cpu Logic Leon Core addr data_cpu data addr_cpp cpp Debug ?? data_cpp IPWrappers Gig_Eth Note: rest and clk signals not shown !!!

Vhdl record definitions memo : memory_out_type { address(28) : data(32) : ramsn(3) : ramoen(3) : iosn(1) : romsn(2) : oen(1) : writen(1) : wrn(4) : bdrive(1) : read(1) : } memi : memory_in_type { data(32) : brdyn(1) : bexcn(1) : writen(1) : wrn(4) : }

Vhdl record definitions mctrlo : mctrl_out_type { } sdo : sdram_out_type { } sdi : sdram_in_type { }

Vhdl record definitions (cont) ahbsi : ahb_slv_in_type { } ahbso : ahb_slv_out_type { } aphi : apb_slv_in_type { } apho : apb_slv_out_type { }

Vhdl record definitions (cont) pioo : pio_out_type { } wpo : wprot_out_type { } ahbmi : ahb_mst_in_vector { } ahbmo : ahb_mst_out_vector { }

Vhdl record definitions (debug signal) dmo : dsumem_out_type { } dmi : dsumem_int_type { } dsi : dsuif_in_type { } dsuo : dsu_out_type { }