Monitoring and Debugging of Optical Link Synchronization in L0 Trigger Systems at CERN

130 likes | 238 Views

This document discusses the synchronization, monitoring, and debugging processes of the optical links in the selection crate used for the L0 trigger at CERN. It outlines the strategy for maintaining optical link synchronization through the GOL's idle patterns and the implementation of 16-bit registers accessible via ECS for configuring parameters during transmission. It emphasizes the role of validation cards in ensuring link reliability and the monitoring frameworks for FPGA conditions, error management, and data recording efficiencies, essential for seamless operation of the L0DU and TELL1 interfaces.

Monitoring and Debugging of Optical Link Synchronization in L0 Trigger Systems at CERN

E N D

Presentation Transcript

Monitoring and Debuggingthe Selection Crate U. Marconi INFN Bologna L0 Trigger Workshop, CERN, 27/10/04

Outline • Synchronization of the optical links • Monitoring • Setting • Debugging the Selection Boards

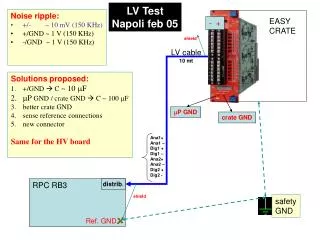

Synchronization of theOptical Links • The GOL transmits idle patterns while the tx_en is asserted. These patterns are used by the TLK2501, at the receiver side (Selection Crate) to synchronize. • The proposal(*) is to put two 16-bits registers on the transmitter boards, accessible by the ECS, to set the BX number and set the number of machine cycles while keeping the tx_en asserted. • Validation Cards Selection Boards links synchronization • The VC’s have to provide the functionality described above • Do the VC generate test patterns? • How do we manage the connections which are used to send data to L0DU and to the TELL1? (*) E. Aslanides et al. LHCb Technical Note 2004-012

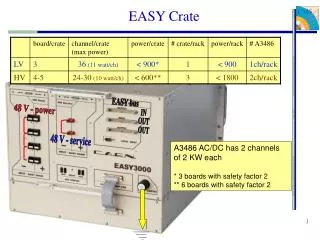

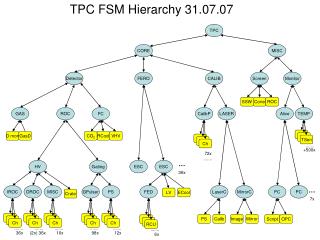

Selection BoardBlock Scheme 12 channel optical transducer Fast Control Highest and transverse energy sum TTCrq Deserialization Demu 2:1 Synchronization L0 10-ch To the L0DU 1-ch Tx Processing Unit Deserialization Demu 2:1 Synchronization 8-ch 1-ch Tx ECS Deserialization Demu 2:1 Synchronization CCPC Glue Card 10-ch L0 buffer 1-ch Tx L1 5 + 1 FPGA’s 28 clusters of 32 bits to L1 in case of L0 accept

FPGA FPGA controller controller FPGA control via “local bus” • Each FPGA will be interfaced for monitoring purposes to the local bus, provided by the PLX PCI 9030 of the Glue Card Local bus Glue Card CCPC PLX PCI9030

Testing the local bus Old Selection Board Genoa’s Test Board CCPC FPGA Registers Local Bus Connectors Glue Card Access to the FPGA via local bus is presently under test: we are testing the PLX 32 bits bus using the software by N. Neufeld

TLK 2501 TLK 2501 TLK 2501 TLK 2501 TLK 2501 TLK 2501 Monitoring the FPGA’s Out FIFO: 1 FIFO to record the output 16-bits @ 80MHz From each TLK FPGA FIFO Processing write FIFO FIFO FIFO FIFO Local bus 6TLK/FPGA Glue Card write full In FIFO 6 FIFO’s (1 per channel) to store the 32 bits data patterns (max depth: 512 cycles) full ECS starts the data recording start

TLK 2501 TLK 2501 TLK 2501 TLK 2501 TLK 2501 TLK 2501 Phasing the input channels The delays are regulated to align all the channels to the last (slowest) one FPGA delay delay delay delay delay delay FIFO Local bus Glue Card 6TLK/FPGA write full 16-bits @ 80MHz From each TLK ECS start the data recording start Data at this stage have been already synchronized to the LHC clock

Monitoring the Optical Links Local bus FPGA 16-bits @ 80MHz Glue Card TLK 2501 Control Logic RX_DV/LOS RX_ER Interrupt CCPC Control Signals Error Counter Set the bit pattern to 0 Reset the TLK Arm the interrupt to the CCPC

Buffer depth ECS Register R/W LUT ECS Ghost Enable ECS Register Ch Delay ECS Register Ch Enable ECS Register Settings and Monitoring(FPGA functional blocks) ECS control ECS control Count Errors In FIFO Acquire Out FIFO Acquire SUM DV and ER Data clock recovered 80MHz Ch Syncro DeMux & Control Word Bit 0=0 Bit 16=1 MAX Address Decode LUT Ch Delay Bx align. Ghost EEPROM LUT L0 Buffer clock LHC x 2 80MHz

Test of the Selection Board Mezzanine Test Board Pattern Generator Selection Board Multi-channel mezzanine optical transmitter 12x32 bits @ 40 MHz

Selection BoardBlock Scheme 12 channel optical transducer Fast Control Highest and transverse energy sum TTCrq Deserialization Demu 2:1 Synchronization L0 10-ch To the L0DU 1-ch Tx Processing Unit Deserialization Demu 2:1 Synchronization 8-ch 1-ch Tx ECS Deserialization Demu 2:1 Synchronization CCPC Glue Card 10-ch L0 buffer 1-ch Tx L1 Renaud’s proposal: add to L0 buffer the output of the selection board

Summary • The optical inputs will be kept monitored by the control logics integrated in the processing FPGA’s. • The FPGA’s operating conditions can be monitored by acquiring the content of the input/output control FIFO’s, via ECS . • Setting of relevant delays is performed by configuring the board registers via ECS. • Synchronization of the optical links should be performed asserting the GOL tx_en at the Validation Card.