Boost Power Supply Capacitor Placement

230 likes | 411 Views

Boost Power Supply Capacitor Placement. Michael Day 2011 FAE Disty Training. Customer Field Failures. Customer has field failures FA report states the ubiquitous “EOS” What’s the root cause of the failure? How do you eliminate it? The #1 problem is usually poor customer PWB layout.

Boost Power Supply Capacitor Placement

E N D

Presentation Transcript

Boost Power Supply Capacitor Placement Michael Day 2011 FAE Disty Training

Customer Field Failures • Customer has field failures • FA report states the ubiquitous “EOS” • What’s the root cause of the failure? • How do you eliminate it? • The #1 problem is usually poor customer PWB layout.

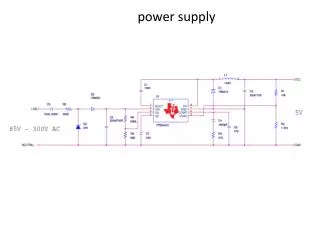

Boost converter current loops Power FET on Power FET off Which is most important loop for layout? Power FET turn-off loop is most important

Power FET Turn-off Parasitic inductance creates ringing on SW node

Power FET Turn-off With power FET on No di/dt, so no voltage across inductance

Power FET Turn-off Current through parasistic L ramps from 0A to a maximum value in short time. This creates a voltage drop across the inductance that adds to Vout + V_paraL2 - + V_paraL1 - - V_paraL3 +

TPS61240 ExampleHow output capacitor placement affect voltage ringing Output Capacitor

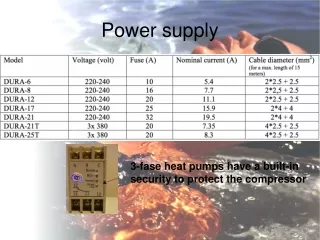

Change Output Capacitor Location Measure Voltage at Inductor connection to power FETs (SW node) • Case 1) Co at IC • Case 2) Co under IC (through vias) • Case 3) Co near IC • Case 4) Co away from IC • Co = 4.7uFCeramic6.3VX5R, 20%0402 - + Probe Output Capacitor Locations

Side By Side Comparison Under IC (vias) Away from IC Near IC At IC Away from IC (9V) Near IC (8.5V) Under IC (8V) At IC (7V) 2V/div 5ns/div

Co near IC ~8.4 V

Co away from IC ~9 V

Appendix BCapacitance of Common PCB Structures (pF/m) (pF/m) Dimensions can be any units but must be the same. For example, if w is in mils then h must also be in mils.

Appendix CInductance of Common PCB Structures In H/m, h and w can be any units as long as they are the same. In H/m, d and w can be any units as long as they are the same.

Inductance of Common PCB Structures Answer in nH, h and d are in inches Answer in nH, t,l and w are in inches