DPU PRESENTATION

DPU PRESENTATION. R.Orfei & S. Pezzuto CNR- IFSI. FUNDING AND DELIVERY CRITICALITY. FACT: IFSI has got no funds from ASI after 2001, that has prevented attendance at meetings, reviews, support during integrations…… FACT: the ASI-Carlo Gavazzi Space contract has been extended up to 31/01/2004

DPU PRESENTATION

E N D

Presentation Transcript

DPU PRESENTATION R.Orfei & S. Pezzuto CNR- IFSI Digital Processing Unit

FUNDING AND DELIVERY CRITICALITY • FACT: IFSI has got no funds from ASI after 2001, that has prevented attendance at meetings, reviews, support during integrations…… • FACT: the ASI-Carlo Gavazzi Space contract has been extended up to 31/01/2004 • PREDICTION: from now up to 31/01/2004 a new contract/addendum will be issued taking into account the PD#4 items (e.g. the SW reset of the IEEE-1355 chip); the new contract/addendum will expire at the end of 2004 • FACT: the lack of funds, the stop of CGS activities (waiting for the PD#4 ASI approval) and the present HW problems have driven a very critical DPU/ICU Herschel schedule Digital Processing Unit

Design status (1/2) • During the AVM tests a random loss of the 1355 links has been detected and investigations are in progress to identify the source of the problem • At present the IFSI unit is at CGS to carry out the investigation • The analysis (thanks also to CSL, IAC and MPE for their help!) has shown that consecutive addressing of the STD-1553 Dual Port RAM and of the IEEE-1355 Dual Port RAM causes the loss of the 1355 links. The HW is now suspect. • The design of the HW boards (contracted to Carlo Gavazzi Space) will be corrected in EQM and FM to include the necessary modifications resulting from the fixing of the above problem Digital Processing Unit

DESIGN STATUS (2/2) AVM SW nearly completed; missing items: • new OBCP and autonomy function (to be implemented when available) • patching • uploading of OBCP implemented but not tested • other types of patching not addressed • Burst mode implemented but not thoroughly tested • upgrading of the VIRTUOSO O.S.: waiting for an offer from WIND RIVER • New OBS image uploadable with the BOOT SW Digital Processing Unit

SW DOCUMENTATION • SSD: is in progress, issue 1 should be available by the end of November (SW requirements inserted, logical model and architecture design revised) • DDD: a new issue will be ready after the SW is stabilized • SVVP: a new issue was circulated according to S. Thurey’s comments. Some comments require a new document layout and a new release will be issued asap in line with IFSI manpower Digital Processing Unit

BUDGETS FOR FM (1/2)(ACTUAL MASS INFERRED FROM AVM BOARDS) • Box weight (mechanics): 3037 g CPU Boards (2 of): 960 g I/F Boards (2 of): 640 g DC/DC Boards (2 of) (E): 1000 g Motherboard: 520 g Screws etc.: 100 g Cabling (E): 300 g Conformal coating (E): 420 g TOTAL (E) 6977 g (+-200 g) Digital Processing Unit

BOX INTERFACE CONTROL DRAWING Digital Processing Unit

BUDGETS FOR FM (2/2) TOTAL ESTIMATED POWER (DC/DC CONVERTER EFFICIENCY = 70%): 14.6 W Digital Processing Unit

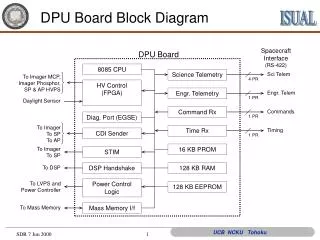

JTAG DSP 21020 RAM IEEE-1355 MEZZANINE FPGA EPROM 20 MHz CPU BOARD Digital Processing Unit

NOT FOR PACS FIFOS FIFOS S/S I/Fs A/D Conv. 16 MHz 1553B (S/C I/F) Long Stub Trafos “A” and “B” FPGA I/F BOARD Digital Processing Unit

DPU Digital Processing Unit

AIV FLOW Digital Processing Unit

EQM SCHEDULE (TENTATIVE) Digital Processing Unit

FM SCHEDULE (TENTATIVE) Digital Processing Unit

PA/QA ACTIVITIES • ALL COMPONENTS ARE BOUGHT THROUGH THE CO-ORDINATED PARTS PROCUREMENT AGENCY • FOR INDUCTORS AND TRANSFORMERS RELEVANT RFAs AND PADs ISSUED • NO RE-FLOW SOLDERING IS FORESEEN: ALL HAND MADE SOLDERS (INCLUDING SMD) BY ESA QUALIFIED PERSONNEL • ENVIRONMENTAL QUALIFICATION TESTS ARE SCHEDULED FOR QM UNITS (A REDUCTION SET OF TESTS, ON THE GROUNDS OF SIMILARITY, IS UNDER EVALUATION) • ENVIRONMENTAL ACCEPTANCE TESTS ARE SCHEDULED FOR FM UNITS (A REDUCTION SET OF TESTS, ON THE GROUNDS OF SIMILARITY, IS UNDER EVALUATION) Digital Processing Unit