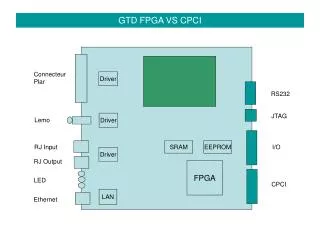

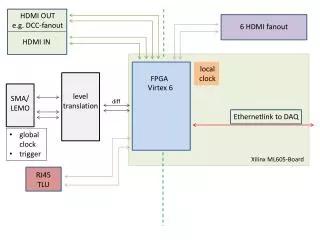

EMP2CYC FPGA moule

E N D

Presentation Transcript

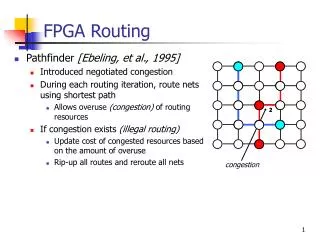

FPGA란? • FPGA(field programmable gate array, 현장 프로그래머블 게이트 어레이)은 프로그래머블 논리 요소와 프로그래밍가능 내부선이 포함된 반도체 소자이다. 프로그래머블 논리 요소는 AND, OR, XOR, NOT, 더 복잡한 디코더나 계산기능의 조합 기능같은 기본적인 논리 게이트의 기능을 복제하여 프로그래밍할 수 있다. 대부분의 FPGA는 프로그래밍가능 논리 요소 (FPGA 식으로는 논리 블록이라고도 함)에 간단한 플립플롭이나 더 완벽한 메모리 블록으로 된 메모리 요소도 포함하고 있다. • 프로그램이 가능한 내부선 계층구조는 FPGA의 논리블록을 시스템 설계자가 요구하는 대로 단일칩 프로그래밍가능 빵판처럼 내부연결을 할 수 있다. 이 논리블록과 내부선은 제조공정 이후에 소비자/설계자가 프로그램할 수 있으므로 요구되는 어떠한 논리기능도 수행할 수 있다.(그러한 이유로 "현장 프로그래머블") • FPGA는 일반적으로 주문형 반도체(ASIC) 대용품보다 느리고, 복잡한 설계에 적용할 수 없으며, 소비전력이 크다. 그러나 개발시간이 짧고, 오류를 현장에서 재수정할 수 있고, 초기 개발비가 저렴하다는 장점이 있다.

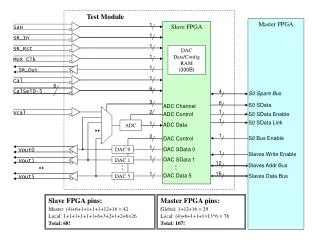

EMP2CYC 보드의특징 • EMPOS II 에 연결하여 사용 할 수있는 다양한 기능의 주변장치와 FPGA 로 구성 • EMPOS II 와 분리하여 독립적으로 FPGA 실험 (+5VDC 아답터 사용) • ALTERA FPGA Cyclone 120,000 게이트 장착 • 다양한 VHDL 실습코드 제공 • LED Dot Matrix 10*7 • I/O 실습용 LED 8 개 • Stepping Motor 1 개 • 16 키패드 (4x4) • CMOS Image Sensor 카메라 응용 • USB 1.1 Host Controller 내장 • C8051 의 12비트 ADC/DAC ( ADC 8채널, DAC 2채널) • SRAM (256 x 16Bit) 기본장착 ( 512Kbyte ) • 50 핀의 확장 포트 지원 • 16*2 의 문자형 LCD 내장 • ALTERA Quartus II 의 Software 설계환경 실습

EMP2CYC • 본 장비에서 사용하는 Cyclone Device는 Quartus II 소프트웨어에서 로직을 설계하고 설계 • 한 로직을 프로그래밍 할 수 있는데, ALTERA에서 무료로 제공한다 • www.altera.com접속 우측상단 다운로드센터 ->쿼터스2웹에디션9.0 다운로드

4bit up/down counter 설계 • 회로 정의 • 본 장에서 설계하고자 하는 것은 Quartus II를 이용하여 간단한 4bit up/Down counter를 • 설계하는 것이다. • 이 4bit up/down 카운터는 클럭과 up/down 키의 입력을 받아 그 결과를 LED에 출력 하 • 도록 구성된다. • 프로젝트 선언 • 제어 로직을 설계하기 위해서는 아래와 같이 먼저 프로젝트를 선언해야 한다.

회로 설계 • 아래는 디바이스에서 동작하기 위한 로직을 설계하는 방법이다. • 로직을 설계하는 방법은 크게 VHDL등과 같은 language로의 방법과 Schematic에 의한 설계 방법이 있다. • 아래는 이 중 처음 접근하여 사용하기가 그리 어렵지 않은 schematic에 의한 설계방법에 대한 설명이다.

아래의 그림과 같이 File 메뉴의 New 항목을 선택해서, 나타난 New 창에 Design SetupFiles의 “Block Diagram/Schematic File” 항목을 선택한다.

아래 그림과 같이 생성된 설계 도면을 마우스로 두 번 클릭하여 Symbol 창을 나타낸 후,“4count”라는 심볼 명을 Name 창에 입력하여 4count 심볼을 불러와 도면에 삽입한다.

같은 방법으로 Symbol 창에서 input과 output 포트를 불러와 아래 그림과 같이 정렬시키고 각 심볼의 끝을 마우스의 Drag & Drop을 통한 선(Wire)으로 연결하여 회로를 완성한다. “Pin Name” 부분을 마우스로 더블 클릭하여, 아래 그림과 같이 각각을 DNUP, CLK, Q1,Q2, Q3, Q4로 설정한다.

일반적인 설계는 이렇게 하면 되지만, EMPOS II CYCLONE 모듈에서 버튼 스위치를 사용하기 위해서는 아래 그림과 같이 GND에 연결된 SW_SCAN 버튼을 추가 해주어야 한다. 그리고, DNUP와 CLK의 앞에 각각 NOT을 추가 해 준다. 그 이유는 앞의 PUSH_SW 블록설명에서 버튼 스위치가 스캐닝 방식으로 동작하도록 설계되었기 때문이다

File 메뉴의 Save항목을 선택하여 gs_4cnt.bdf 라는 파일명으로 저장한다. Processing 메뉴의 Start Compilation 항목을 선택하여, 컴파일을 진행한다. 이 때의 컴파일은 문법 오류 검사의 목적으로 사용된다.

핀/디바이스 설정 및 컴파일 • Assignments 메뉴의 Device 항목을 선택하여 나타난 Setting 창에서 • Device의 Family가 “Cyclone”으로 설정되어 있는지, 디바이스는 “EP1C6Q208C8”으로 설 • 정되어 있는지를 확인한 후, 아래 그림과 같이 “Device & Pin Option” 버튼을 선택한다

아래 그림과 같이 설정한 후에 확인 버튼을 눌러 현재 설정한 내용을 저장한다

Assignments 메뉴의 Assignment Editor 항목을 선택하여 아래의 순서로 Pin 설정을 진행한다

Assignment Editor 창의 아래항목에서 Name의 <<new>>부분을 마우스로 더블 클릭하면Node Name이 나타난다 CLK를 선택한다

Node Name 옆의Location 부분을 마우스로 더블 클릭하면 오른쪽 아래의 그림과 같이 설정할 수 있는 핀번호가 나타나는데, 이곳에서해당하는 핀 번호를 설정한다.clk의 경우 장비의 SW1의 핀번호인 “166”로 설정

같은 방법으로 gs_4cnt.bdf에서 사용한 Node Name을 설정한다.아래와 같이 설정후 Processing메뉴의 Start Compilation 항목을 선택하여 컴파일을 진행

시뮬레이션 • 설계한 로직에 대하여 이런 입력 조건을 설정하였을 때, 어떤 결과가 나타나는지를 확인하 • 는 부분이다. 다시 말해 설계자의 의도대로 설계되었는지를 디바이스에 프로그래밍하여 하 • 드웨어에 대한 확인 전에 소프트웨어로 먼저 확인해 보는 단계라 할 수 있다. High-Speed • 로 동작되는 회로의 경우 하드웨어로의 확인이 어렵기 때문에 출력되는 데이터의 결과를 • 이런 시뮬레이션을 통해 확인해 봐야 하는 경우도 있다.

File 메뉴의 New 항목을 선택하고, 아래 그림과 같이 Other Files의 Vector Waveform File을 선택하여 Waveform Editor 창을 불러온다.

Waveform Editor 창을 불러온 상태에서 Edit 메뉴의 “Insert Node or Bus..” 항목을 선택하고, Insert Node or Bus 창에서 Node Finder 버튼을 눌러 시뮬레이션에 필요한 입 출력 노드를 불러온다.

Name의 부분을 “*”으로 type하고, Filter의 항목을 “Pins : all”로 설정한 후 List버튼을 누르면 아래의 왼쪽 그림과 같이 로직에서 사용된 노드들이 나타나는데, Node Finder 창 중앙의 “>>”버튼을 눌러 전체를 오른쪽으로 이동시킨 후 OK 버튼을 누른다.

위와 같이 설정을 하면 아래의 왼쪽 그림과 같이 Insert Node or Bus의 창이 설정되는데,OK 버튼을 누르면 아래의 오른쪽 그림과 같이 Waveform Editor창에 각각의 입 출력 노드가 나타나는 것을 볼 수 있다.

입출력 조건을 표현하는 단위라 할 수 있는 Grid Size는 아래 그림과 같이 Edit 메뉴의Grid Size에서 변경할 수 있다. Time Period를 50ns로 설정한다. 시뮬레이션이 끝나는 시간인 End Time도 아래 그림과 같이 Edit 메뉴의 End Time 항목을선택하여 변경할 수 있다. Time을 5 us로 설정한다.

CLK 입력에 대한 데이터 설정에서, clk는 클럭(‘0’과 ‘1’의 반복)을 나타내는 부분이므로, 아래 그림과 같이 Waveform Editor창의 clk 입력에 대한 Value 부분을 마우스로 클릭하여 clk입력에 대한 전체를 선택한 후 오른쪽 데이터 입력 icon의 을 선택하여 클럭을 설정한다. 클럭 설정은 아래의 오른쪽 그림과 같이 Time Period의 Period를 50.0 ns, dutycycle을 50으로 설정한다.

DNUP의 입력 노드에서 값의 중앙 부분을 마우스로 drag하여 선택 한 후, 아래의 오른쪽그림과 같이 왼쪽에 있는 데이터 입력 icon에서 을 선택하여 ‘1’의 상태로 설정한다.

File 메뉴의 Save를 통해 gs_4cnt.vwf 파일로 저장한 후, Processing 메뉴의 StartSimulation 항목을 선택하여 시뮬레이션을 진행한다

아래 그림은 시뮬레이션이 끝난 후 나타나는 Simulation Report창이다. 여기에서 시뮬레이션이 되는 결과를 확인해 볼 수 있다.아래의 결과를 살펴보면 DNUP의 값이 ‘0’일 때 클럭이 ‘0’에서 ‘1’로 변하는 rising edge의순간에 값이 업 카운트되며, DNUP의 값이 ‘1’일 때 클럭의 rising edge에서는 다운 카운트되는 것을 확인해 볼 수 있다.아래의 결과에서 클럭의 rising edge의 순간보다 약간 늦게 데이터가 출력이 되는 것을 볼수 있는데, 이것은 디바이스와 핀 설정 등에 대한 하드웨어적인 delay time을 적용하였기때문이다.

프로그래밍 • 장비를 EMPOS II 장비에 장착시키거나 5V 아답터를 연결한다. • EMPOS II CYCLONE 모듈의 JTAG Port에 ByteBlasterMV를 연결한다. • DIP S/W 2의 스위치를 모두 OFF한다. 이 이유는 DIP S/W 2의 핀과 LED의 핀이 공통으로 • 사용되기 때문이다. • 보드의 전원을 ON 한다

시뮬레이션을 통해 설계한 로직에 대한 검증이 끝난 후, 이 Program과정에서 디바이스에프로그램하여 하드웨어적인 검증 과정을 진행하는데 아래는 이 부분에 대한 설명이다. Tools 메뉴의 Programmer항목을 선택하여 Programmer 창을 불러온다.

처음 Programmer를 불러왔다면, 아래 그림과 같이 Programming Hardware가 “No Hardware”의 상태로 나타난다. “Hardware” 버튼을 눌러 Programming Hardware를 설정한다. 아래와 같이 설정한다

디바이스에 프로그래밍 하기 위해서 아래 그림과 같이 Mode를 JTAG으로 설정하고, 왼쪽의 icon을 선택합니다. 이것은 Auto Detection으로 JTAG Chain으로 연결되어 있는디바이스를 자동으로 검색해 주는 기능이다.Auto Detection icon을 누르면 아래의 오른쪽 그림과 같이 디바이스 항목에 EPC2과EP1C6 항목이 나타나는데, EP1C6 항목의 File의 <none>부분을 마우스로 더블 클릭.

마우스로 더블 클릭하면 아래 그림과 같이 Select New Programming File 창이 나타나는데,앞서 컴파일할 때 생성되었던 gs_4cnt.sof 파일을 선택하면 아래의 오른쪽 그림과 같이 프로그래밍 파일이 추가되는 것을 확인해 볼 수 있다.

아래의 그림과 같이 EP1C6Q240 항목 오른쪽의 Program/Configure 부분을 체크하고 왼쪽의 (Start Programming)icon을 선택하여 장비에 프로그래밍을 한다.

프로그래밍이 끝난 후 EMPOS II CYCLONE 모듈의 Switch인 SW1과 SW4의 버튼을 눌렀을 때, 즉 입력 노드에 값이 들어왔을 때의 결과를 LED를 통하여 확인해 볼 수 있다.이 때, 시뮬레이션 결과와 일치 하는지에 대한 확인 한다 4bit up/down counter 끝