Overview of DSM Output Configuration and Energy Processing in BEMC and EEMC Systems

E N D

Presentation Transcript

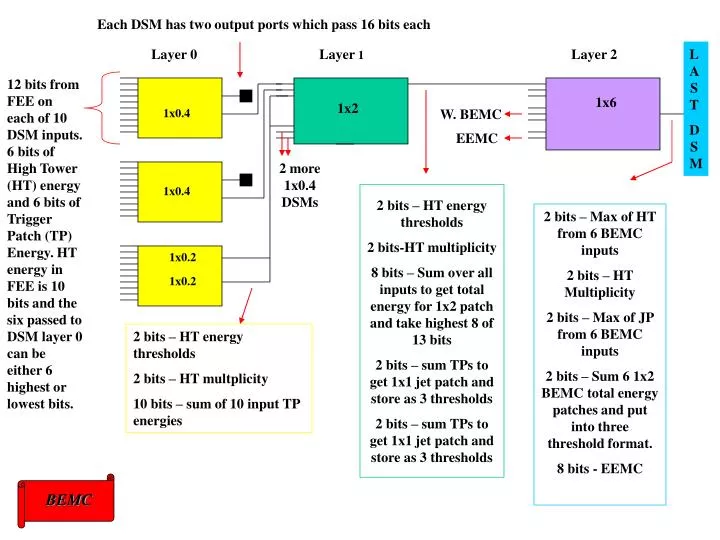

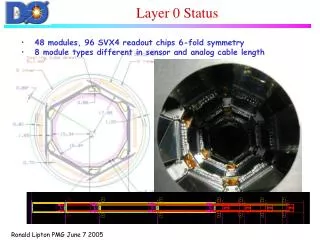

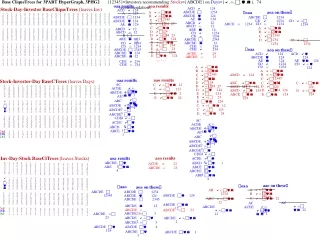

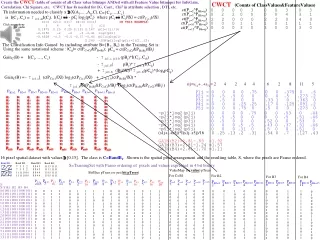

Each DSM has two output ports which pass 16 bits each Layer 0 Layer 1 Layer 2 LAST DSM 12 bits from FEE on each of 10 DSM inputs. 6 bits of High Tower (HT) energy and 6 bits of Trigger Patch (TP) Energy. HT energy in FEE is 10 bits and the six passed to DSM layer 0 can be either 6 highest or lowest bits. 1x6 1x2 1x0.4 W. BEMC EEMC 2 more 1x0.4 DSMs 1x0.4 2 bits – HT energy thresholds 2 bits-HT multiplicity 8 bits – Sum over all inputs to get total energy for 1x2 patch and take highest 8 of 13 bits 2 bits – sum TPs to get 1x1 jet patch and store as 3 thresholds 2 bits – sum TPs to get 1x1 jet patch and store as 3 thresholds 2 bits – Max of HT from 6 BEMC inputs 2 bits – HT Multiplicity 2 bits – Max of JP from 6 BEMC inputs 2 bits – Sum 6 1x2 BEMC total energy patches and put into three threshold format. 8 bits - EEMC 1x0.2 1x0.2 2 bits – HT energy thresholds 2 bits – HT multplicity 10 bits – sum of 10 input TP energies BEMC

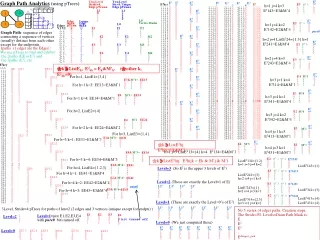

2 bit – Max of BEMC and EEMC JP in 2 thresholds bit=11 if EEMC & BEMC adjacent JP bit is true 2 bit – Max of BEMC and EEMC HT in 2 thresh . Bit=11 if HT >=2 mult for low thresh. 1 bit – Etot > threshold for BEMC Each DSM has two output ports which pass 16 bits each LAST DSM Layer 0 Layer 1 Layer 2 12 bits from FEE on each of 10 DSM inputs. 6 bits of High Tower (HT) energy and 6 bits of Trigger Patch (TP) Energy. Top bit OR’d with higher bits. 1x3 1x6 1x0.6 W. BEMC E. BEMC 1x0.6 + 1x0.6 + 1x0.3 DSM 1x0.3 1x0.3 2 bits – HT Max from all EEMC 2 bits – TP energy for above HT 2 bits – EEMC JP 00 – 0 > 1st thr. 01 – 1 > 1st thr. 10 – 1 > 2nd thr. 11 – 1 > 3rd thr. Or 2 adj>2nd 1 bit –adjacent BEMC and EEMC JPs > 2nd threshold 8 bits – see BEMC 2 bits – max HT energy 2 bits –TP energy which contains above HT 2 bits – HT multiplicity 7 bits – Etot sum for 1x3 patch. Take bits 2-8 out of 13 total (2-128 GeV) 3 bits – Jet Patch (JP) sum TPs to get 3 1x1 jet patches (A,B,C). 2 bits – HT energy 2 bits –TP energy which contains above HT 2 bits – HT multiplicity 10 bits – sum of 10 input TP energies 000 – (A & B & C) < 1st thr 111 – (A+B) or (B+C) > 3rd 101 – (A or B or C) > 1st 001 – A > 2nd thr 010 – B > 2nd thr 100 – C > 2nd thr EEMC (EEMC HT multiplicity is or’d with BEMC at this level )