Operating System Development for Reconfigurable Computers: Enhancing Performance with BORPH

100 likes | 212 Views

This project focuses on the design and implementation of an operating system specifically tailored for reconfigurable computers. The system, based on the BORPH architecture, optimizes the flexibility of hardware with software interaction, allowing for efficient computation across various applications. It leverages FPGA technology to enhance performance while improving area, speed, and power efficiency. The work involves generating BOF files, configuring FPGAs, and refining hardware/software interfaces, ultimately contributing to advancements in high-performance computing.

Operating System Development for Reconfigurable Computers: Enhancing Performance with BORPH

E N D

Presentation Transcript

An Operating System for Reconfigurable Computers Brandon Hamilton MSc – University of Cape Town Supervisor – Prof. Michael Inggs (UCT) Co-supervisors – Dr. Alan Langman (SKA) Dr. Hayden So (HKU)

Reconfigurable Computers ASIC Specific Parallel High performance CPU General Sequential Lower performance FPGA Programmable logic devices in a system design Hardware-based logic can be changed to perform various tasks Reconfigurable devices can be configured to provide the best match for the computational requirements at that specific time, giving much better area – speed – power performance.

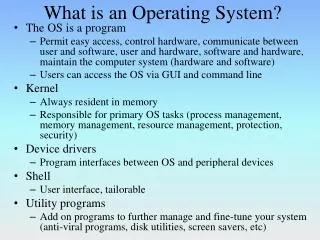

Benefits of an Operating System • Operating System support • File system • Network • Familiar to both Software and Hardware engineers • Design language independent

BORPH • Berkeley Operating System for ReProgrammableHardware • Treats reconfigurable hardware as computational resources • UNIX interface to hardware designs • Hardware processes

Using BORPH • Generate BOF file (Simulinktoolchain) • Bitstream • User defined hardware constructs • Execute BOF process • Configures FPGA • IOREG virtual files • Read/Write to user defined hardware constructs

Porting BORPH • Port and install bootloader • Das U-Boot • Device Specific code • Configuration of FPGA • Interface to FPGA and other hardware • IOREG interface to READ/WRITE • Update to latest mainstream kernel • Adapt Simulinktoolchain and system generator

Further Research • Hardware Accelerator model • Hardware/Software interface • Shared Memory • Memory Access patterns • Cache coherency

Thank you References • H. K.-H. So and R. Brodersen, "A Unified Hardware/Software Runtime Environment for FPGA-Based Reconfigurable Computers using BORPH," ACM Transactions on Embedded Computing Systems (TECS), Volume 7, Issue 2, Feb, 2008, New York, NY, USA. • H. K.-H. So, "Runtime Filesystem Support for Reconfigurable FPGA Hardware Processes in BORPH," In Proceedings of the Sixteenth Annual IEEE Symposium on Field-Programmable Custom Computing Machine, Apr. 2008.