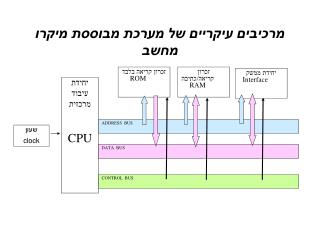

מרכיבים עיקריים של מערכת מבוססת מיקרו מחשב

מרכיבים עיקריים של מערכת מבוססת מיקרו מחשב. זכרון קריאה בלבד ROM. זכרון קריאה/כתיבה RAM. יחידת ממשק Interface. יחידת עיבוד מרכזית CPU. ADDRESS BUS. שעון clock. DATA BUS.

מרכיבים עיקריים של מערכת מבוססת מיקרו מחשב

E N D

Presentation Transcript

מרכיבים עיקריים של מערכת מבוססת מיקרו מחשב זכרון קריאה בלבדROM זכרון קריאה/כתיבהRAM יחידת ממשקInterface יחידת עיבוד מרכזית CPU ADDRESS BUS שעון clock DATA BUS CONTROL BUS

עיקרון עבודת המערכת מבוססת מיקרו מחשב מערכת מבוססת מיקרו מחשב כוללת את שלושת המרכיבים הבאים: • CPU- Central Processing Unit (Microprocessor) - יחידת עיבוד מרכזית (מעבד ) • Main Memory - זיכרון ראשי בו מאוחסנים פקודותונתונים של התוכניתבזמן ביצוע • Input/Output Devices – התקנים ליצירת קשר בין המעבד לבין המשתמש • Memory and I/O Subsystem – פסים להעברת מידע בין המעבד לבין הזיכרון ובין המעבד לבין התקני קלט/פלט • Address Bus- מעביר כתובת גישה ממעבד לתאי זיכרון או להתקני קלט/פלט • Data Bus- מעביר נתונים • Control Bus - מעביר אותות בקרה לניהול גישה לזיכרון ו להתקני קלט/פלט • כל מסלול הוא למעשה אוסף של קווים המקשרים את ה- CPU אל מרכיבי המערכת. כל מרכיבי המערכת מחוברים אל ה- CPU במקביל . • כל משימה שהמערכת צריכה לבצע , כתובה כתוכנית בשפת תכנות כלשהי, מתורגמת לשפת מכונה ע"י קומפיילר ומאוחסנת בזיכרון כאוסף נתונים בינאריים בסדר מסוים ( Set of Operation Codes - OpCodes). • אלמנת לבצע המשימה ה-CPU פונה לאזור בזיכרון הראשי איפה נמצאת התוכנית המקודדת, מביא את ה- Opcode של הפקודה הנוכחית מזיכרון אל ה-CPU, מפענח את ה- Opcode ומבצע את הפקודה, שוב פעם פונה לזיכרון להבאת פקודה הבאה וכך עד סוף התוכנית.

Program counter Address Bus Address=N Opcode Data Bus Instruction Register Control Bus N Opcode Clk Rd CPU Main Memory הבאת פקודה לביצוע מהזיכרון אל ה- CPUOpcode Fetch Cycle • ה-CPU פונה לאזור בזיכרון הראשי עליו מצביע ה- counterProgram, מביא את ה- Opcode של הפקודה הנוכחית מזיכרון אל ה-CPU, מפענח אותה ומבצע את הפקודה. שוב פונה לזיכרון להבאת הפקודה הבאה מפענח ומבצע וכך עד סוף התוכנית.

מבחינה אחת לפחות, המיקרופרוססור הוא מכונה פשוטה מאוד. הוא חוזר כל הזמן על הרצף: • הבא את ההוראה הבאה מהזיכרון- Fetch • בצע את ההוראה - Execution • לך לשלב 1. ארבע שלבי ביצוע הפקודה • Instruction Fetchהבאת Opcode של הפקודה לביצוע מזיכרון ראשי אל ה- CPU . • Instruction decode פענוח הפקודה( Opcode)שנמצאת באוגר IP ע"י החומרה • Execution ביצוע הפקודה (עיבוד אריתמטי , אחסון זמני ) • Write back כתיבת התוצאות העיבוד חזרה לזיכרון הראשי בסך-הכל קיימות חמש פעולות שונות או חמישה מחזורי פס אפשריים: • קריאה מהזיכרון. • כתיבה לזיכרון. • קריאה מקלט/פלט. • כתיבה לקלט/פלט. • סרק (פעולה פנימית שאינה דורשת גישה לזיכרון או למיפתח קלט/פלט).

תכונות של המעבד 8086 המעבד 8086 יוצר ע"י חברת INTEL בשנת 1978. המעבד 8086 בעל תכונות הבאות: • רוחב פס נתונים- 16 סיביות • רוחב אוגרים פנימיים - 16 סיביות , זאת אומרת שהוא יכול לעבד נתונים בעלי 16 סיביות בפעולות אריתמטיות - לוגיות • רוחב פס כתובותכלפי זיכרון - 20 סיביות , זאת אומרת שהוא יכול לגשת לזיכרון ראשי בגודל 220 = 1,048,576 = 1 Mbyte • רוחב פס כתובות כלפי התקני קלט/פלט - 16 סיביות , זאת אומרת שהוא יכול להתחבר למספר התקנים: 216 = 64535 Devices • המעבד 8086 יכול לגשת לזיכרון להבאת נתונים בגודל 1 byteאו 1 word=2 byte בגישה אחד, תלוי בפקודה. • המעבד 8088 דומה מאוד למעבד 8086 חוץ מרוחב פס נתונים חיצוני שהוא בעל 8 סיביות - להבאת נתון בגודל 1 word=2 byte המעבד 8088 פעמיים ניגש לזיכרון .

8088 • 20 קווי כתובת • 8 קווי נתונים

הצגת נתון במיקרו מחשב • נתונים לא מסומנים MSB LSB 1 byte – 8 bit MSB LSB 1 word – 16 bit • נתונים מסומנים Sign MSB LSB 1 byte Sign MSB LSB 1 word

BUSיחידת הקשר ל--BIU - BUS INTERFACE UNIT–EU - EXECUTION UNIT - יחידות הביצוע-

מיבנה פנימי של המעבד 8086 • המעבד 8086 נקרא גם כן CPUמורכב בתוכו משתי יחידות פונקציונאליות יקאריות: • יחידה להבאת נתון מזיכרון –BIU – Bus Interface Unit יחידה זאת בונה את כתובת גישה לזיכרון , פונה לזיכרון , קוראת את הפקודה הבאה מהזיכרון לפס נתונים , מעבירה אותה ל-CPU ומאחסנת אותה לחוצץ של 6בתים - תור פקודות( QUEUE). יחידת BIU כוללת 4 אוגרי סגמנט -Code Segment,Data Segment Stack Segment,Extra Segment - ואוגר Instruction Pointer (כולם – 16 סיביות) • יחידת ביצוע – EU – Execution Unit0 יחידה זאת לוקחת פקודות מהחוצץ ומבצעת אותן ללא תלות ביחידת BIU. החוצץ ( QUEUE) עובד בעיקרון של FIFO – הפקודה שהוכנסה ראשונה לתור הפקודות ע"י יחידת BIU יוצת ראשונה לביצוע ע"י יחידת EU. • שתי היחידות האלו מפצלות את עומס עבודת ה-CPU כדי לעלות את מהירותו ואת יעילותו של המעבד.

ES 16 bit CS 16 bit SS 16 bit DS 16 bit IP 16 bit אוסף אוגרים של המעבד 8086 Extra Segment BIU registers (for 20 bit address generation) Code Segment Stack Segment Data Segment Instruction Pointer AX 16 bit AH 8 bit AL 8 bit Accumulator BX 16 bit BH 8 bit BL 8 bit Base Register CX 16 bit CH 8 bit CL 8 bit Count Register DX 16 bit DH 8 bit DL 8 bit Data Register SP 16 bit Stack Pointer BP 16 bit Base Pointer EU registers 16 bit arithmetic SI 16 bit Source Index Register DI 16 bit Destination Index Register FLAGS 16 bit

MEMORY Address DI 64K Extra Seg EXTRA FFFFFH Segment Registers ES:0 DATA SI, BX 64K Data Segment STACK DS:0 SP 64K Stack Segment CODE SS:0 64K Code Segment IP (PC) CS:0 00000H חלוקת זיכרון למקטעים

אופן גישה לזיכרון ראשי של המעבד 8086 • כל תוכנית באופן קבוע מאוחסנת בזיכרון משני (דיסקט, דיסק קשיח, CD-ROM ). • בהזמנת תוכנית לביצוע מערכת הפעלה מעתיקה את התוכנית ,שהוזמנה בשמה , מזיכרון משני לזיכרון ראשי ומשם התוכנית ניתנת לגישה מצד המעבד. • זיכרון ראשי של המעבד 8086 ניתן לגישה ע"י פס כתובות בעל 20 סיביות וכולל 2^20 = 1 Mbyte תאים ברוחב 8 סיביות כל תא אחד. • האוגרים הפנימיים של המעבד 8086 בעלי רוחב 16 סיביות ובעזרת אוגר אחד אי-אפשר לבנות כתובת גישה לזיכרון בעלת 20 סיביות רוחב. • בגלל זה הזיכרון הראשי מחולק למקטעים כך שכל תוכנית ,שרצה במעבד , מקבלת מספר מוגבל של המקטעים (עד 4 מקטעים) בהם מאוחסנים: תוכנה – ב- Code Segment, נתונים-ב-Data Segment or Extra Segment , מחסנית – ב-Stack Segment . • מערכת הפעלה מנהלת את הזיכרון וממקמת את כל התוכניות שעולות לביצוע בסגמנטים משלהם וטוענת את אוגרי המקטעים ( CS, DS, SS, ES ) בהתאם. • כל תוכנית שרצה יכולה להשתמש אך ורק בתאי הזיכרון שבתוך המקטעים ולגשת אליהם ע"י אוגרי הצבעה פנימיים של המעבד ( בעלי 16 סיביות בלבד) • הגודל המכסימלי של המקטע – 2^16 = 64 KBytes

אופן גישה לזיכרון ע"י שילוב אוגר מקטע ואוגר הצבעה • כתובת מלאה של התא בזיכרון הראשי נקראת כתובת פיזית וכוללת 20 סיביות • הכתובת הזאת נבנה ע"י זוג אוגרים : אוגר מקטע ואוגר הצבעה ,שכל אחד מהם בעל 16 סיביות • 16 סיביות עליונות של כתובת התחלתית של המקטע נטענת לאוגר מקטע ע"י מערכת הפעלה ונקראת כתובת התחלתית של המקטע • CPU מצביע לתוך המקטעים ע"י אוגרי הצבעה וכתובת זאת (בתוך המקטע) בעלת 16 סיביות נקראת כתובת יחסית ( Offset ) או כתובת אפקטיבית ( Effective Address ) • כדי לבנות כתובת פיזית בעלת 20 סיביות משני האוגרים, ה-CPU טוען תוכן של אוגר המקטע לאוגר הזזה, מזיז אותה בארבע סיביות כלפי שמאל, מחבר אליו תוכן של אוגר ההצבעה ומפיק את תוצאת החיבור לפס כתובות של המערכת • ה- CPU ,באופן ברירת מחדל , משייך את אוגרי ההצבעה למקטעים באופן הבא: • אוגר IP (Instruction Pointer ) or PC ( Program Counter) מצביע לתוך Code Segment : CS:IP • אוגרים SI,DI,BX מצביעים לתוך Data Segment : DS:SI, DS:DI, DS:BX • אוגרים SP,BP מצביעים לתוך Stack Segment : SS:SP, SS:BP • אין ברירת מחדל ל- Extra Segment - משתמשים במקטע זה רק לפעולות עם מחרוזות – String Operations • אפשר לשנות את ברירת המחדל ע"י כתיבת זוג אוגרים בפקודה: DS:BP

דוגמה לחישוב כתובת פיזית 0H 40000H CS: 04000H 40056H IP 0056H CS:IP = 4000:56 Logical Address Memory 0 04000 Segment Register Offset Physical or Absolute Address + 0056 0FFFFFH 040056H .

אופן שימוש באוגרים כלליים הארכיטקטורה של המעבד 8086 כוללת 8 אוגרים בעלי רוחב 16 סיביות למתרות כלליות של אחסון נתונים ולמתרות מיוחדותהבאות: • AX (accumulator) -- צובר תוצאות של פקודות אריתמטיות • BX (base register) – אוגר הצבעה למקטע הנתונים בזיכרון ראשי – מחזיק כתובת יחסית של הנתונים • CX (counter) -- משמש כמונה לולאות בפקודה LOOP • DX (data) : • משמש כאוגר הרחבה (בנוסף לאוגר AX ) לפעולות אריתמטיות לשמירת החלק העליון של התוצאה. • משמש כאוגר אצבעה להתקני קלט/פלט – מחזיק כתובת גישה להתקני קלט/פלט • SI & DI (Source Index & Destination Index) : • אוגר הצבעה למקטע הנתונים בזיכרון ראשי • אוגרי הצבעה למחרוזות • SP (stack pointer) -- אוגר הצבעה לראש המחסנית, משתנה אוטומטית עקב פקודות גישה למחסנית ( לא מומלץ לטעון או לשנות אותו ידנית) • BP (base pointer) -- אוגר הצבעה לתוך המחסנית – מותר לשימוש חופשי

דירוג של שפות תכנות שפות תכנות מדורגות בשלוש רמות: • High level language – שפת C# , Visual C ,Visual Basic השפות האלו לא מתייחסות למבנה פנימי של המעבד אלא להיגיון של המשימה בגדול. • Low level language - Assembly Language השפה זו מתייחסתלמבנה פנימי של המעבד ומפרטת למעבד את כל שלבי ביצוע של המשימה בהתאם לאוסף פקודות של שפת אסמבלי שמוכר למעבד הזה. • Machine language – שפת מכונה בשפה זאת התוכנית מקודדת למספרים בקוד בינארי וישר מוכנה לביצוע ע"י המעבד. כל פקודה של שפת אסמבלי מתורגמת ע"י קומפיילר לפקודה בשפת מכובה וכוללת שדות הבאות: קידוד של פקודה עצמה שניקרא Operation Code – OPCODE ומשתנים ( OPERANDS ) כלפיהם מתבצעת את הפקודה • כל תוכנית שכתובה בשפה עלית או בשפת אסמבלי חייבת לעבור תרגום לשפת מכונה.

High-level language program Assembly language program Machine language program Compiler Assembler תרגום לשפת מכונה של המעבד 8086 • תרגום משפת אסמבלי ASM86 לשפת מכונה של המעבד 8086 מתבצעת בשני שלבים : • תרגום עצמו ע"י TASM Compiler עם יצירת קובץ Listing לזיהוי טעויות • וקישור בין חלקי התוכנית ע"י - TLINKTASM Linker • TASM/l My_Prog.ASM My_Prog.OBJ , My_Prog.LST • TLINK My_Prog.OBJ My_Prog.EXE My_Prog.EXE – Executable File

שיטות מיעון • Register-אוגר-MOV DX,AX • Immediate - - מיידיMOV DX,20 ; אופרנט המקור הוא מספר • Direct–ישיר- TWENTY DW 20h; גישה לנתון לפי כתובתו MOV DX,TWENTY; DX 0020h • Register Indirect- עקיף -MOV DX,[SI] ; גישה לנתון בעזרת אוגר הצבעה • ערך באוגרהצבעה זהוהכתובת יחסית של התא במקטע בזיכרון הראשי • סוגריים מרובעות [ ] מסמנות מעון עקיף • בברירת מחדל האוגרים BX, DI, SI מצביעים לתוך ה-Data Segment בזוג עם האוגר DS • בברירת מחדל האוגר BP מצביע לתוך ה-Stack Segment בזוג עם האוגר SS • אפשר לשנות את ברירת המחדל ע"י כתיבת זוג בפקודה ES:BX; SS:SI MOV DX,[SS: SI] • Based Indexed - MOV AX, [BX+DI]גישה לנתון בעזרת זוג אוגרי הצבעה ; Pair of registers for use: BX+DI; BX+SI; BP+DI; BP+SI • Based Indexed Plus Displacement - MOV AL, [BP+SI+DISP] גישה לנתון בעזרת זוג אוגרי הצבעה ועוד היסט מספרי

Data Transfer Instructions • MOV target, source • reg, reg • mem, reg • reg, mem • mem, immed • reg, immed • שני אופרנטים חייבים להיות באותו גודל • אופרנט המקור יכול להיות :אוגר, תא בזיכרון או קבוע (מספר) • אופרנט המקור יכול להיות :אוגר או תא בזיכרון • אי-אפשר להעביר נתון מתא בזיכרון לתא בזיכרון באופן ישיר

Data Transfer Instructions – Examples • MOV Data,67h • MOV AX, [BX] • MOV BX,CS:Data+4 • MOV AX,[SS:SI] • MOV AX, [BX+SI+7] • MOV AX,[BP+SI+2] • MOV AX,BL – Impossible • MOV Data1, Data2 – Impossible

פקודות קפיצה עם תנאי • JE / JZ Jump equal or jump zero Z=1 • JNE / JNZ Jump not equal or jump not zero Z=0 Jump Based on Unsigned Data • JA / JNBE Jump above or jump not below/ equal C=0 & Z=0 • JAE / JNB Jump above/ equal or jump not below C=0 • JB / JNAE Jump below or jump not above/ equal C=1 • JBE / JNA Jump below/ equal or jump not above C=1 or Z=1 Jump Based on Signed Data • JG / JNLE Jump greater or jump not less/ equal S=0 & Z=0 • JGE / JNL Jump greater/ equal or jump not less S=0 • JL / JNGE Jump less or jump not greater/ equal S=1 • JLE / JNG Jump less/ equal or jump not greater S=1 or Z=1

דוגמה של תוכנית פשוטה בשפת אסמבלי : מילוי זיכרון בנתון “A” SSeg SEGMENT STACK ; Open the Stack Segment DW 50 DUP (?) ; The Stack Size Is 50 Words SSeg ENDS ; Close the Stack Segment DSeg SEGMENT ; Open the Data Segment block DB 100 DUP (0) ; Block for Filling bl_length DW 50 ; Number of Data for Filling DSeg ENDS ; Close the Data Segment CSeg SEGMENT ; Open the Code Segment ASSUME CS: CSeg, DS: DSeg,SS:SSeg main: MOV AX, DSeg MOV DS,AX MOV DI, OFFSET block MOV AL,’A’ MOV CX, bl_length next: MOV [DI],AL INC DI LOOP next INT 3 CSeg ENDS ; Close the Code Segment END main ; End the Program Code

Code segment (CS), which defines the main program or instructions. Data segment (DS), which defines the data you used. Stack segment (SS), which defines the stack. Address CS 3230:0000 DS 1750:0000 SS 0100:0000 הייצוג תוכנית בזיכרון ראשי

הנחיות של שפת אסמבלי - Directives הנחיות הן לא פקודות לביצוע ע"י המעבד אלא קובעות לקומפיילר איך לתרגם את התוכנית ואיך לארגן את הזיכרון • SEGMENT -- פותח את המקטע ומגדיר את סוגו • ENDS – סגירת המקטע • ORG – קובע מיקום יחסי של נתון או פקודה בתוך המקטע • ASSUME – משייך את שמו המקטע לאוגר המקטע המתאים • DB - Define byte - הגדרת נתון בגודל byte • DW - Define word - הגדרת נתון בגודלword • DD – Define double word - הגדרת נתון בגודלword כפול • EQU - הגדרת קבוע (Constant ) • $ - מסמן את המקום הנוכחי (כתובת ) בשלב הקומפילציה

15 0 x x x x OF DF IF TF SF ZF x AF x PF x CF אוגר דגלים של המעבד 8086 יחידת ביצוע EU כולל אוגר דגלים ( Flag Register ) שהוא אוסף של דגלי מצב וסיביות בקרה. • דגלי מצב מושפעים מפקודות אריתמטיות או פקודות השווה ומזהים את מצבו הנוכחי של המעבד • סיביות בקרה קובעות למעבד את אופן עבודתו • - CF Carry Flag- Bit 0עולה ל-1 אם יש גלישה מגודל האוגר • - PF Parity Flag- Bit 2 עולה ל-1 אם תוכן של האוגר AL - זוגי • - AF Auxiliary Carry Flag- Bit 4 עולה ל-1 אם יש גלישה מ-formatBCD • - ZF Zero Flag- Bit 6 עולה ל-1 אם תוצאת הפעולה האריתמטית או הלוגית האחרונה היא 0 . • - SF Sign Flag- Bit 7 מזהה סימן – ערכו כערכה של הסיבית השמאלית (MSB) של התוצאה בפעולות חיבור/חיסור ובפעולות לוגיות. • - TF Single Step Trap Flag- Bit 8 סיבית בקרה – מאפשר ביצוע תוכנית בשלבים • - IF Interrupt Enable Flag- Bit 9 סיבית בקרה – מאפשר קבלת בקשות פסיקה מהחומרה החיצונית • - DF String Instruction Direction Flag- Bit 10 סיבית בקרה – קובעת כיוון סריקת הזיכרון בפעולות עם מחרוזות • - OF Overflow Flag- Bit 11 עולה ל-1 אם יש גלישה בפעולות אריתמטיות עם מספרים מסומנים • Bits 1, 3, 5, 12-15 – לא מוגדרות

ZERO FLAG- דגל האפס דוגמאות לפעולות שאחריהן דגל האפס יקבל את נערך "1": כאשר אנו כותבים את הפקודות: DEC CX JZ FINISH אנו למעשה נעזרים בדגל האפס,הפקודה JZ בודקת את מצב הדגל, ועפ"י מצבו מחליטה אם לקפוץ . דוגמא נוספת: CMP DL,4 JE GOOD

באלו מהמקרים הבאים דגל הסימן יעלה ל-"1"? • MOV DL,0 • MOV AL,5SUB AL,5 • MOV AL,0FFHADD AL,1 • MOV CX,36HCMP CX,’6’ • MOV AH,-2CMP AH,0FEH

CARRY FLAGדגל הנשא – + דוגמאות לפעולות שאחריהן דגל הנשא יקבל את נערך "1": 1111 1111 0001 0000דגל הנשא 1 0000 0000 OVERFLOW FLAGדגל הגלישה –

AND - Logical And • Usage: AND dest,src dest=dest(and)src • Modifies flags: CF OF PF SF ZF (AF undefined) • Operands • reg,reg • mem,reg • reg,mem • reg,immed • mem,immed • accum,immed • OR - Inclusive Logical OR • Usage: OR dest,src dest=dest(or)src • Modifies flags: CF OF PF SF ZF (AF undefined) • Operands • reg,reg • mem,reg • reg,mem • reg,immed • mem8,immed8 • mem16,immed16 • accum,immed

XOR - Exclusive OR • Usage: XOR dest,src dest=dest(xor)src • Modifies flags: CF OF PF SF ZF (AF undefined) • Operands • reg,reg • mem,reg • reg,mem • reg,immed • mem,immed • accum,immed • NOT - One's Compliment Negation (Logical NOT) • Usage: NOT dest • Modifies flags: None • Inverts the bits of the "dest" operand forming the 1s complement. • Operands • reg • mem

NEG - Two's Complement Negation • Usage: NEG dest • Modifies flags: AF CF OF PF SF ZF • מבצע משלים ל- 2 • Operands • reg • mem • TEST - Test For Bit Pattern • Usage: TEST dest,src • Modifies flags: CF OF PF SF ZF (AF undefined) • פקודה זו מבצעת את פעולת ה- AND אך לא שומרת את הפתרון אלא מעדכנת דגלים בלבד. נעדיף להשתמש בפקודה זו לבדיקה של סיבית מסוימת. • Operands • reg,reg • reg,mem • mem,reg • reg,immed • mem,immed • accum,immed 4F0Hקטע תוכנית הבודקת את הנתון בכתובת בכתובת. אם המספר שלילי יוצב 1 באוגר CX . אם המספר חיובי יוצב 0 באוגר CX. • MOV CX,0 • TEST BYTE PTR DS:[4F0H],80H • JZ POSITIVE • MOV CX,1 • POSITIVE: NOP

נתונים של תוכנית שמורים ברוב המקרים באזור של Data Segment ומוגדרים בצורה הבאה: <variable name> DB | DW | DD <value> V1 DB 25h V2 DW 28A5h V3 DB 11001010b מערך נתונים מוגדר בצורה הבאה: <arrayname> DB | DW <size>dup (<element>) Array DB 10 dup(?) <arrayname> DB | DW value1, value2, value3 Integers DB 0, 1, 2, 3, 4 מחרוזת נתונים בקוד ASCII מוגדר בצורה הבאה <stringname> DB ‘<string>$’ String DB “HELLO$” הנחית של שפת אסמבלי להגדרת נתונים

Bytes in Storage FFFFFh 01h 23h 45h 67h Data3 01h 00 Data2 35h DAh Data1 00000 אופן שמירת נתונים בזיכרון ראשי • Word, Double word- שמורים בזיכרון בסדר הפוך Directive Data1 DW 35DAh Data2 DW 256 Data3 DD 1234567H

הגדרת קבועים - Constants • name EQU expression הגדרת קבוע ללא שינוי בהמשך התוכנית sample EQU 7Fh ערך מספרי ; message EQU <This is a message> ; מחרוזת • Name = expression הגדרת קבוע עם שינוי בהמשך התוכנית – ערך מספרי בלבד max_int = 7FFFh count = 1 count = count * 2

Basic structure of Code Segment • Code Segment- מקטע שכולל תוכנית מקודדת לביצוע המשימה ע"י המעבד • תוכנית בשפת אסמבלי ASM86 זוהי אוסף פקודות שמוכרות למעבד 8086 • כל פקודה בנויה לפי תבנית הבאה: <Label>:<Mnemonic> <Destination_Operand,Source_Operand> ; <Comment> • <label name> - תווית - שם סימבולי קטן מ-31 תווים , לא מתחיל מספרה , לא מילה שמורה • <Mnemonic> - שם הפקודה מאוסף , מוכר למעבד 8086 • <Destination_Operand,Source_Operand> - שני אופרנטים שמשתתפים בפקודה • העברת הנתון תמיד מתבצעת מאופרנט המקורלאופרנט היעד • בפעולות אריתמטיות/לוגיות תוצאה תמיד נכנסת לאופרנט היעד • <Comment> - טקסט שמלווה את הפקודה אלמנת להסביר תוכנית • L1: MOV Data_Addr ,86h;Load number 86h to Data_Addr in Main Memory

Main Program Proc1 Proc2 Proc3 הגדרת תת-שיגרה <procedure name> PROC {FAR | NEAR} : : ;***your (main/ sub) program here*** <procedure name> ENDP • <procedure name> - חייב להיות מיוחד • PROC - הנחיה לקומפיילר להתחיל תת-שיגרה • ENDP - הנחיה לקומפיילר לסיים תת-שיגרה • Far – תת-שיגרה נקראת מחוץ ל-Code Segment הנוכחי • Near - תת-שיגרה נקראת אותו Code Segment הנוכחי

Segmentation Example: MOV AX,[BX] MOV Instruction ⇒ DS Effective Address = BX Logical Address = DS:BX = 2100:0123

Change data size operator - ptr <type> PTR <expression> Operator ptr for change data size definition (from double word to byte or to word for example) Data DW 1234H MOV byte ptr Data,55h ; [Data] 1255h MOV AL, byte ptr Data+1 ; AL12h

פקודת החלפה • XCHG target, source • reg, reg • reg, mem • mem, reg For example: DATA DW 20 • XCHG BL, AH • XCHG DATA, AX • בפקודות MOV ו- XCHG אי-אפשר לבצע את העברת הנתונים בין שני תאי זיכרון

Address Loading Instructions • LEA <reg16>, <EA>; טעינת כתובת יחסית של הנתון במקטע נתונים לאוגר הצבעה • MOV <reg16>, offset<data> ; טעינת כתובת יחסית של הנתון במקטע נתונים לאוגר הצבעה • LDS < reg16>,<Mem32>; טעינת אוגר הצבעה בעל 16 סיביות ובנוסף אוגר מקטע DS בנתון ששמור בזיכרון כדי להכין כתובת חדשה מלאה LES < reg16>,<Mem32> ;טעינת אוגר הצבעה בעל 16 סיביות ובנוסף אוגר מקטע ES בנתון ששמור בזיכרון כדי להכין כתובת חדשה מלאה DSEG SEGMENT ORG 10H Data DD 12345670H ------ • LDS SI, Data ;SI <=5670H, DS <=1234H • LEA DI,Data ;DI <=10Hoffset of Data from Data Segment Beginning • MOVDI, offset Data ; the same operation

אופן הגדרת המחסנית בתוכנית • מחסנית היא חלק מזיכרון ראשי שמיועדת לשמירת נתונים באופן זמני בשלושה מקרים: • ביצוע פקודות שמירה - PUSH • קריאה לתת-שגרות - procedure call • ביצוע פסיקות - interrupt execution • הגדרת גודל המחסנית מתבצעת בהנחיה הבאה: DW <size of stack> dup(<initial value>) לדוגמה: Stack_Seg SEGMENT STACK DW 100h dup(0) Stack_Seg ENDS • המחסנית נוצרת בזמן שהתוכנית עולה לביצוע לזיכרון הראשי • Stack segment register (SS) - מקבל ערך התחלתי ממערכת הפעלה • Stack pointer (SP) - קובע את ראש המחסנית בהתאם להגדרת המחסנית (SP200h ) • רוחב המחסנית במעבד 8086 מוגדר כ- word , אי-אפשר לשמור נתונים בגודלbyte • שני אוגרים מצבעים באופן ברירת מחדל לתוך המחסנית :SP,BP • אוגר SP מושפע מכל פעולת גישה למחסנית באופן אוטומטי • אוגר BP ניתן להצבעה חופשית בתוך המחסנית

Pop Direction Push Direction FFFFEh FFFFFh top of stack SP=200h SS 16 bit 00001 00000 Main Memory אופן גישה למחסנית עם פקודותPush,Pop • פקודה Push מאחסנת נתון במחסנית • הפקודה מתבצעת בשני שלבים: א. SP SP - 2 ב. [SS:SP] data • פקודה Pop הוצא נתון במחסנית • הפקודה מתבצעת בשני שלבים: • א. [SS:SP] data • ב. SP SP + 2

פקודות קלט/פלט • כל התקן קלט/פלט מחובר למערכת המיקרופרוססור דרך פורטים בעלי כתובת גישה מסוים. סך הכול מרחב כתובות הוא 0000 FFFFh אבל מנוצלים הרבה פחות כתובות - תלוי במבנה המערכת • IN AL, IN_PORT ;קליטת נתון בעל 8 סיביות מפורט כניסה בכתובת בעלת 8 סיביות • IN AX, IN_PORT ;קליטת נתון בעל 16 סיביות מפורט כניסה בכתובת בעלת 8 סיביות • MOV DX, IN_PORT ;בכתובת גישה לפורט אם הכתובת בעלת 16 סיביותDX טעינת אוגר • IN AL, DX ; קליטת נתון בעל 8 סיביות מפורט כניסה בכתובת בעלת 16 סיביות • IN AX, DX; קליטת נתון בעל 16 סיביות מפורט כניסה בכתובת בעלת 16 סיביות • OUT IN_PORT, AL ; פליטת נתון בעל 8 סיביות מפורט כניסה בכתובת בעלת 8 סיביות • OUT IN_PORT, AX ; פליטת נתון בעל 16 סיביות מפורט כניסה בכתובת בעלת 8 סיביות • MOV DX,OUT_PORT ; בכתובת גישה לפורט אם הכתובת בעלת 16 סיביותDX טעינת אוגר • OUT DX, AL ; פליטת נתון בעל 8 סיביות מפורט כניסה בכתובת בעלת 16 סיביות • OUT DX, AX ; פליטת נתון בעל 16 סיביות מפורט כניסה בכתובת בעלת 16 סיביות

פקודות אריתמטיות – חיבור( Addition) ADD dest, source ; חיבור בין שני נתונים ADC dest, source ;ועוד סיבית הנשאחיבור בין שני נתונים INC dest ;הוספת 1 לתוכן האוגר או תא בזיכרון DAA ;Decimal adjust for addition (הפקודה מתקנת את תוצאת החיבור בין שני מספרים בצופן Package BCD לצופן Package BCD.) הפקודה מתבצעת כלפי אוגר AL בלבד AAA ;ASCII adjust for addition (הפקודה מתקנת את תוצאת החיבור בין שני מספרים בצופן ASCII לצופן Un-package BCD) הפקודה מתלעת כלפי אוגר AL בלבד