Re-synthesis for Reliability Design

550 likes | 732 Views

Re-synthesis for Reliability Design. Shih-Chieh Chang. Department of Computer Science National Tsing Hua University. Reliability Design. Logic Re-synthesis for delay variation tolerance (DAC 04) A Vectorless Estimation of Maximum Instantaneous Current for Sequential Circuits (ICCAD 04).

Re-synthesis for Reliability Design

E N D

Presentation Transcript

Re-synthesis for Reliability Design Shih-Chieh Chang Department of Computer Science National Tsing Hua University 1

Reliability Design • Logic Re-synthesis for delay variation tolerance (DAC 04) • A Vectorless Estimation of Maximum Instantaneous Current for Sequential Circuits (ICCAD 04) 2

Reliability Design • Logic Re-synthesis for delay variation tolerance (DAC 04) • A Vectorless Estimation of Maximum Instantaneous Current for Sequential Circuits (ICCAD 04) 3

Delay Variation Problem • Circuit delay is increasingly sensitive to • process variation • delay defects • IR drop, cross talk • Timing violation due to delay variation. 4

Pessimistic Delay Analysis • Traditional solutions: Delay variation problem is alleviated by adding timing margin. • Unnecessary pessimism: a fabricated ASIC may run up to 40% faster [Chinnery and Keutzer]. • Adding timing margin may not be possible. • Our solutions: Add redundancy (area penalty) for delay variation tolerance. 5

2 Gate delay = 1 7 Circuit delay = 6 Delay Variation on a Gate • Gates along critical paths are vulnerable to delay variation. • Vulnerable gates have small slacks. 6

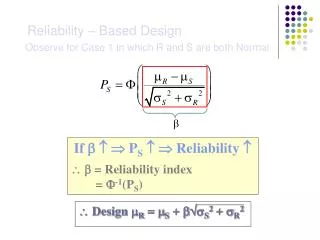

Delay Tolerance and Slack • A gate’s slack: the delay increase without violating circuit’s delay. • Slack has correlation with delay tolerance • Smaller slack more vulnerable. • Increase slacks of gates increase delay variation tolerance. 7

gate delay = 1 • timing requirement = 7 Delay Tolerance on a Circuit • Definition: A circuit has dt delay tolerance if the smallest slack is dt. 8

Delay Tolerance on a Circuit • Definition: A circuit has dt delay tolerance if the smallest slack is dt. The smallest slack is 1 The circuit has 1 delay tolerance 1 1 1 1 1 1 1 9

Problem Formulation • Inputs: • a circuit and, • a delay tolerance requirement dt, • Outputs: • a re-synthesized circuitwithdt delay tolerance. 10

V 1 1 1 1 1 1 1 voting machine Our Basic Idea • Add redundant gates so that the smallest slack is increased. Now: 1 delay tolerance Goal: 2 delay tolerance 11

V 2 2 2 2 2 voting machine Our Basic Idea • Function does not change, but the smallest slack is increased to 2. The circuit has 2 delay tolerance 12

V Voting machine Steps of our approach • Start with Triple modular redundancy: three copies and a voting machine. 13

0 1 1 1 V Voting machine 1 Property of TMR (1) • Any two copies correct output correct • Each wire/gate is redundant. 1 14

V The latest signal Property of TMR (2) • The delay is NOT decided by the latest signal. The second arriving signal 15

V Delay = infinite Property of TMR (2) • If a node’s delay becomes infinity, it will not affect the final delay. • Each wire/gate has infinite slack in a TMR. 16

TMR v.s. Delay Tolerance • TMR can tolerate delay variation due to infinite slack. • Process variation or noises may cause circuit delay to increase by 10% - 20%. Infinite slack is over-protective. • 200% area penalty in a TMR is impractical. 17

Slack Changes After Wire Removal Gate slack = infinite 0 V 18

Removing Redundant Wires • After removing a redundant wire/gate, • circuit function does not change, • some slacks may be decreased. • Objective: remove redundant wires/gates while maintaining the smallest slack dt. 19

Removing Wires V 20

Removing Wires The smallest slack is 2 Satisfy dt=2 V 21

V Signal Sharing • Share the functions of side-input wires. 22

Signal Sharing • Share the functions of side-input wires. V 23

V Resulting Circuit The smallest slack is 2 Satisfy dt=2 24

Outline • Delay variation problem • Triple Modular Redundancy (TMR) • Re-synthesis for delay variation tolerance • Experimental results • Conclusion 25

Experimental Flow • Given a circuit, optimize the circuit by script.delay and obtain the circuit’s delay. • Re-synthesize the circuit using dt = 10% * the circuit’s delay or 15% * the circuit’s delay 26

Statistical Analysis • Compare the statistically timing between a circuit and its re-synthesized circuit. • Assume each gate’s delay to be a probability density function as described in [Liou DAC02]. • Run Monte-Carlo to generate 10,000 samples for both a circuit and its re-synthesized circuit. • Count the number of samples whose delay satisfies a pre-defined delay requirement. • Delay requirement = 1.1 * the circuit’s delay 28

Conclusion • Re-synthesize for dt delay tolerance. • Adopt wire removal and signal sharing to reduce area overhead. • Area penalty is about 21% for 10% delay tolerance. 30

Reliability Design • Logic Re-synthesis for delay variation tolerance (DAC 04) • A Vectorless Estimation of Maximum Instantaneous Current for Sequential Circuits (ICCAD 04) 31

Power Noises • Excessively large current through power bus may cause IR drop and EM. • Severe IR drop and EM degrade the performance and reliability. • Accurate estimation of Maximum Instantaneous Current (MIC) to analyze noises. 32

0 0 Maximum Instantaneous Current • Maximum Instantaneous Current (MIC) • Input vectors and time. t=1 t=2 t=3 Maximum current=4 at time t=1. Maximum current=3 at time t=3 33

Previous Work • Vector dependent: • Find a vector pair • Lower bound estimation • Vector Independent: • Not find the worst case vectors • Upper bound estimation • iMax and PIE [H. Kriplani et al.] 34

Outline • Maximum instantaneous current (MIC) problem • Signal correlation problems • MIC estimation based on the concept of mutual exclusive switching • Experimental results & conclusion 35

? No correlation Correlation Summary • Identifying signal correlation is important for MIC estimation. • Contribution: Efficiently identify complex combinational and sequential correlations. 36

The two transitions cannot occur simultaneously Combinational Correlation • Signal correlation in a combinational circuit. 37

t=4 Cannot occur simultaneously t=4 Combinational Correlation • Can efficiently recognize complicated combinational correlations. 38

t=0 t=1 Sequential Correlation • Correlation across sequential elements. (0, 1) (f1, f2)= (0, 0) (1, 0) (1, 1) f2 f1 39

Sequential Correlation • Some (next) states are not reachable from a current state. • Deriving state transition diagram is NOT practical. • Implicitly obtain sequential correlation without the need of state transition diagram. • None of the previous work can detect sequential correlation. 40

Before Exploring Signal Correlation… • Decide whether a set of gates can switch simultaneously at time=t1. • Goal: Find necessary conditions for a gate to switch at time=t1. 41

An Example for MES Detection Mutually Exclusive Switching at t=4 ? 42

0 1 1 0 0 1 0 0 1 Initial values Stable values Conflicts Mutually Exclusive Switching Switch at t =4 Switch at t =4 43

Conflicts Mutually Exclusive Switching Mutually Exclusive Switching at t=4 44

g Necessary Conditions in Sequential Circuits switch at t=2 Flip-flop 45

g g 0 0 0 Flip-flop Necessary Conditions in Sequential Circuits • To reveal sequential correlation, we link the two circuit copies through flip-flops. switch at t=2 Initial values Stable values 46

MES MIC Estimation Based on MES • Use an undirected graph to present the MES relation. • Find a set of nodes that have no edge in between. Switch simultaneously. Current contribution =1 Maximum current =3 at time=t1 MES relation at time=t1 47

Experimental Flow • Combinational and sequential MCNC ISCAS benchmarks. • Upper bound estimations: iMax, PIE (1000 s_nodes) , and MES. • Lower bound estimations: Random simulation for 3 days. 48

iMax Random PIE Results for Combinational Circuits iMax=2.6 PIE=2.3 Random=0.95 iMax=2.3 PIE=1.7 49

iMax Random PIE Results for Sequential Circuits iMax=3.1 PIE=2.3 50