VHDL

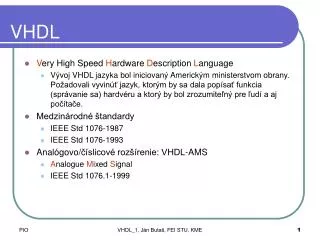

VHDL. Introductie. VHDL als documentatie. VHDL = VHSIC Hardware Description Language VHSIC = Very High Speed Integrated Circuit VHDL is begin jaren ‘80 ontwikkeld in opdracht van het departement van defensie (DoD) van de VS.

VHDL

E N D

Presentation Transcript

VHDL Introductie

VHDL als documentatie • VHDL = VHSIC Hardware Description Language • VHSIC = Very High Speed Integrated Circuit • VHDL is begin jaren ‘80 ontwikkeld in opdracht van het departement van defensie (DoD) van de VS. • Zij wilden in eerste instantie een eigen beschrijving van het gedrag van de asics in de toestellen die ze aankochten. • VHDL werd aanvankelijk dus gebruikt als documentatie en beschrijving van specificaties. Merlijn Aurich – TSO / Invomec

VHDL voor simulatie • Buiten documentatie is VHDL ook nuttig is om simulaties op uit te voeren, dus om de werking van de asic te controlleren op een computer. • Hierdoor kwamen de eerste VHDL simulatie tools op de markt. • Door zijn uitwisselbaarheid won VHDL aan populariteit. Iedere fabricant had namelijk voordien zijn eigen taal bv Verilog (later ook gestandardiseerd en nu de grote tegenhanger van VHDL), AHDL(Altera),… Merlijn Aurich – TSO / Invomec

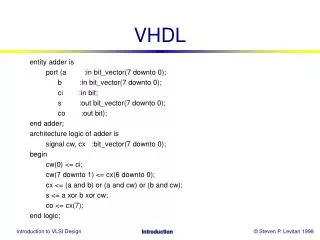

VHDL gestandardiseerd door IEEE • In 1987 werd VHDL gestandaardiseerd door IEEE. • Enkele bedrijven kwamen vervolgens op het idee om software te schrijven waarmee je VHDL kan synthetiseren. • Synthetiseren = het omzetten van een VHDL beschrijving in een netlist. Een netlist is een tekstbestand waarin staat welke standaardcel via welke verbinding aan welke andere standaardcel hangt. • Voorbeelden van standaardcellen: and poorten, flipflops, adders, inverters, buffers…De standaardcellen zijn getekend door een designer. Merlijn Aurich – TSO / Invomec

Voorbeeld van een netlist • module SUB1 ( SHIFT_IN_W1, SHIFT_CLK01, SUB1_1_to_SUB1_2 ); • input SHIFT_IN_W1 ; • input SHIFT_CLK01 ; • output SUB1_1_to_SUB1_2 ; • wire DFF_instance_QB , buf1_to_buf2, DFF_to_buf1 ; • BUFBD1 BUFBD1_instance2 ( • .Z(buf2_to_buf3), • .A(buf1_to_buf2) • ); • BUFBD1 BUFBD1_instance1 ( • .Z(buf1_to_buf2), • .A(DFF_to_buf1) • ); • DFF DFF_instance ( • .Q(DFF_to_buf1), • .QB(DFF_instance_QB), • .CLOCK(SHIFT_CLK01), • .DATA(SHIFT_IN_W1) • ); • endmodule /* SUB1 */ Merlijn Aurich – TSO / Invomec

Synthetiseerbare VHDL (asics) • Aangezien VHDL bedoeld was als documentatie en voor simulatie, zijn de mogelijkheden van de taal vrij uitgebreid. Je kan bijvoorbeeld files openen en erin schrijven of ervan lezen. • Gevolg: slechts een gedeelte van de taal is synthetiseerbaar. • Sommige VHDL constructies zijn helemaal niet synthetiseerbaar. • Sommige VHDL expressies worden genegeerd door synthesetools. Deze expressies hebben wel betekenis tijdens simulaties. (zie volgende slide). Merlijn Aurich – TSO / Invomec

Entity inverter is port ( A : in bit; Z : out bit ); End entity; Architecture behaviour of inverter is begin Z <= not A after 5 ns; End architecture; Entity inverter is port ( A : in bit; Z : out bit ); End entity; Architecture RTL of inverter is begin Z <= not A; End architecture; Voorbeeld: verschil synthetiseerbare en niet-synthetiseerbare VHDL Merlijn Aurich – TSO / Invomec

VHDL voor programeerbare logica • In de jaren 90 begon met ook het nut ervan in te zien om VHDL te gebruiken voor configuratie/programmatie van programmeerbare logica. • Voorheen gebruikte elke fabricant zijn eigen taal. • FPGA: vluchtig (SRAM gebaseerd) • vb: de Flex op het experimenteerbord. • PLD: niet vluchtig (EEPROM gebaseerd) • vb: De Max op het experimenteerbord. • Bekijk de datasheets voor meer informatie Merlijn Aurich – TSO / Invomec

Van VHDL 87 naar VHDL 93 • De syntax van VHDL 87 was niet altijd consistent. • Daarom werden de taal lichtjes veranderd. Dit werd VHDL 93. • Wij gebruiken de syntax van VHDL 93 Merlijn Aurich – TSO / Invomec

Probleem van het standaard type bit • Het type bit is één van de basistypes van VHDL. • Voor dit type bit bestaan er slechts 2 mogelijke waarden: 0 (laag) of 1 (hoog). • In realiteit zijn er echter veel meer mogelijkheden. • Een signaal kan: • hoog-impedant zijn • open drain zijn • onbekend zijn • … • Dit is een probleem voor simulatie. Merlijn Aurich – TSO / Invomec

DE IEEE standard 1164 library • Veel tool vendors boden hun eigen bibliotheken aan met daarin meerwaardige logica. Dit zorgde voor incompatabiliteiten tussen de verschillende tools. • Uiteindelijk werd aan de standaard de bibliotheek IEEE standard 1164 toegevoegd. Hierin zit o.a. het negenwaardige type std_ulogic. • TYPE std_ulogic IS ( • 'U', -- Uninitialized • 'X', -- Forcing Unknown • '0', -- Forcing 0 • '1', -- Forcing 1 • 'Z', -- High Impedance • 'W', -- Weak Unknown • 'L', -- Weak 0 • 'H', -- Weak 1 • '-' -- Don't care • ); Merlijn Aurich – TSO / Invomec

Het std_logic type • Std_ulogic heeft 1 probleem: wat is de waarde indien er twee std_ulogic signalen aan elkaar hangen met verschillende waarde? • ‘0’ + ‘1’ = ? • ‘L’ + ‘H’ = ? • Daarom werd ook het type std_logic gedefineerd. Std_logic is een resolved type, wat wil zeggen dat wanneer twee std_logic signalen aan elkaar hangen, en beide signalen een andere waarde hebben, er via een functie (een resolve functie) bepaald wordt wat de waarde van het uiteindelijke signaal wordt. Merlijn Aurich – TSO / Invomec

VHDL • Wij houden ons vooral bezig met het synthetiseerbare gedeelte van VHDL. • Om er zeker van zijn dat je VHDL synthetiseerbaar is, hou je je best aan de standaard templates, gezien in de lessen van het eerste jaar • Zo zijn er templates voor de verschillende soorten flipflops, multiplexers en state machines Merlijn Aurich – TSO / Invomec

Entity en architecture Library IEEE; Use IEEE.std_logic_1164.all; entityinverter is port( A :instd_logic; Z :outstd_logic); end entity; architectureRTL2of inverteris begin Z<= notA; end architecture; • Library IEEE; • Use IEEE.std_logic_1164.all; • entityinverter is • port( • A :instd_logic; • Z :outstd_logic); • end entity; • architectureRTL1of inverteris • begin • process(A) • begin • Z<= notA; • end process; • end architecture; Merlijn Aurich – TSO / Invomec

And, or, not • Library IEEE; • Use IEEE.std_logic_1164.all; • entityand_or_not is • port( • A , B :instd_logic; • And_out, Or_out :outstd_logic; • Not_out : out std_logic_vector(1 downto 0)); • end entity; • architectureRTL1of and_or_not is • begin • And_out<=A and B; • Or_out <= A or B; • Not out <= (not B) ¬ (A); --concatenatie • end architecture; Merlijn Aurich – TSO / Invomec

Multiplexer • Library IEEE; • Use IEEE.std_logic_1164.all; • entitymux is • port( • A , B, S :instd_logic; • Z :outstd_logic); • end entity; • architectureRTL1of mux is • begin • process(A,B, S) • begin • if S = ‘0’ then • Z <= A; • else • Z <= B; • end process; • end architecture; Merlijn Aurich – TSO / Invomec

Geklokt Process: Flipflop • Library IEEE; • Use IEEE.std_logic_1164.all; • entity flipflop is • port ( • D : in std_logic; • clock : in std_logic; • Q : out std_logic ); • end entity; • architecture RTL of flipflop is • begin • process(clock) • begin • if rising_edge(clock) then • Q <= D; • end if; • end process; • end architecture; Merlijn Aurich – TSO / Invomec

Geklokt Process: Flipflop met asynchrone reset • Library IEEE; • Use IEEE.std_logic_1164.all; • entity reset_flipflop is • port ( • D, reset : in std_logic; • clock : in std_logic; • Q : out std_logic ); • end entity; • architecture RTL of reset_flipflop is • begin • process(clock, reset) • begin • if reset = ‘0’ then • Q <= ‘0’; • elsif rising_edge(clock) then • Q <= D; • end if; • end process; • end architecture; Merlijn Aurich – TSO / Invomec

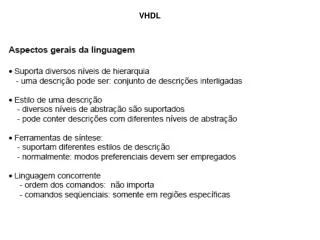

Process Process Process Process The VHDL Connectivity Model The VHDL “View of Life” Multiple Processes • executing statements in sequence, like concentional “software” Interacting ‘concurrently’ • connected by signals Contained within an entity/architecture • or several for a hierarchical design Merlijn Aurich – TSO / Invomec