字位同时扩展示例

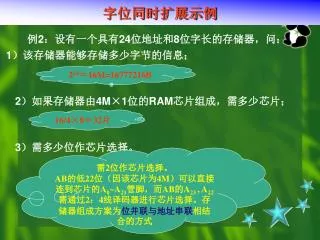

字位同时扩展示例. 例 2 :设有一个具有 24 位地址和 8 位字长的存储器,问: 1 )该存储器能够存储多少字节的信息; 2 )如果存储器由 4M×1 位的 RAM 芯片组成,需多少芯片; 3 )需多少位作芯片选择。. 2 24 = 16M=16777216B. 16/4×8 = 32 片. 需 2 位作芯片选择。 AB 的低 22 位(因该芯片为 4M )可以直接连到芯片的 A 0 ~A 21 管脚,而 AB 的 A 23 , A 22 需通过 2 : 4 线译码器进行芯片选择。存储器组成方案为 位并联与地址串联 相结合的方式. CPU 与存储器连接示例 1.

字位同时扩展示例

E N D

Presentation Transcript

字位同时扩展示例 例2:设有一个具有24位地址和8位字长的存储器,问: 1)该存储器能够存储多少字节的信息; 2)如果存储器由4M×1位的RAM芯片组成,需多少芯片; 3)需多少位作芯片选择。 224=16M=16777216B 16/4×8=32片 需2位作芯片选择。 AB的低22位(因该芯片为4M)可以直接连到芯片的A0~A21管脚,而AB的A23 , A22需通过2:4线译码器进行芯片选择。存储器组成方案为位并联与地址串联相结合的方式

CPU与存储器连接示例1 设CPU有16根地址线,8根数据线,并用MREQ作访 存控制信号 (低电平有效),用WR作读/写控制信号 (高电 平为读,低电平为写)。现有下列存储芯片:1KX4位RAM; 4KX8位RAM;8KX8位RAM;2KX8位 ROM;4KX8位ROM; 8KX8位ROM及74LS138译码器和各种门电路,如下图所示(见 下页)。画出CPU与存储器的连接图,要求: (1) 主存地址空间分配: 6000H~67FFH为系统程序区; 6800H~6BFFH为用户程序区。 (2) 合理选用上述存储芯片,说明各选几片? (3) 详细画出存储芯片的片选逻辑图。

示例1解答 第一步,先将16进制地址范围写成二进制地址码,并 确定其总容量。

示例1解答 第二步,根据地址范围的容量以及该范围在计算机 系统中的作用,选择存储芯片。 由6000H~67FFH系统程序区的范围,应选1片2KX8位的 ROM,无需选4KX8位和8KX8位的ROM,否则就浪费了。 由6800H~6BFFH用户程序区的范围,应选2片1KX4位的 RAM芯片,选其他芯片也必然浪费。 第三步,分配CPU的地址线。 将CPU的低11位地址A10~A0与2KX8位的ROM地址线相 连;将CPU的低10位地址A9~A0与2片1KX4位的RAM地址线相 连。剩下的高位地址与访存控制信号MREQ共同产生存储芯片 的片选信号。 第四步,片选信号的形成。 由题给出的74138译码器输入逻辑关系可知,必须保证控制端G1为高,G2A与G2B为低,得下图所示。

CPU与存储器连接示例2 CPU及其他芯片假设同示例1,画出CPU与存储器 的连接图。要求主存的地址空间满足下述条件:最小8K 地址为系统程序区,与其相邻的16K地址为用户程序区,最 大4K地址空间为系统程序工作区。详细画出存储芯片的片选 逻辑并指出存储芯片的种类及片数。 第一步,根据题目的地址范围写出相应的二进制地址码。

示例2解答 第二步,根据地址范围的容量及其在计算机系统中的 作用,确定最小8K系统程序区选一片8KX8位ROM;与其相 邻的16K用户程序区选2片8KX8位RAM;最大4K系统程序工作 区选1片4KX8位RAM。 第三步,分配CPU地址线。 将CPU的低13位地址线A12~A0与1片8KX8位ROM和两片 8KX8位 RAM的地址线相连;将CPU的低12位地址线A11~A0 与1片4KX8位RAM的地址线相连。 第四步,形成片选信号。 将74LS138译码器的控制端G1接+5V,G2A和G2B接MREQ, 以保证译码器正常工作。CPU的A15、A14、A13分别接在译码 器的C、B、A端,作为变量输入,则其输出 Y0、Y1、Y2 分别 作ROM、RAM1和RAM2的片选信号。此外,根据题意,最 大4K地址范围的A12为高,故经反相后再与Y7相“与”,其输 出作为4KX8位RAM的片选信号,如下图所示。

CPU与存储器连接示例3 用Intel 2114组成4KX8bit的RAM. 分析 Intel 2114为1KX4bit的SRAM芯片,其逻辑符 号如图所示。一个芯片的容量(1K)和字长(4bit)均不能满足 4KX8bit的RAM的要求,因此需要使用字位同时扩展的方法。 用两片Intel2114,采用位扩展法组成1KX8bit的模板;再用4 块模板采用字扩展法组成4KX8bit的RAM。 2片 4块 1K×4bit 1K×8位 4K×8bit 位扩展 字扩展 因此总共需要2X4=8片Intel2114芯片。

示例3解答 解 用Intel 2114组成的4K×8bit的RAM如图所示。

CPU与存储器连接示例4 有4片Intel2114芯片,按下图所示连接(见下页)。试问: (1) 如图所示的连接组成几部分存储区域?共有多大的存 储器容量?字长是多少? (2) 写出每部分存储区域的地址范围。 (3) 说明图中存储器的地址是否连续,若不连续,应该怎 样修改才能使存储器的地址是连续的。

示例4解答 解 (1) Intel 2114是1KX4 bit的SRAM芯片,而CPU有 数据总线8根(D7~D0),由图所示可知,两片Intel 2114 通过位扩展组成一页。图中(1),(2)两个芯片的片选信号并联, 组成第1页,(3),(4)两个芯片片选信号并联组成第2页,每页 存储容量为1KX8bit。 因此,如图所示的连接组成两部分存储区域(两页),共有 2KX8bit的存储容量,字长8bit。 (2) 第1页的地址范围是FC00H~FFFFH,第2页的地址范 围是7C000H~7FFFH。见下表所示。

示例4解答 解 (3) 由(2)的分析结果可知图中存储器的地址是不连 续的。改进的方法是将A15与A10对换。此时,第 1页的 地址范围不变,仍为FC00H~FFFFH,第2页 的地址范围变 为F800H~ FBFFH。这样存储器地址范围就连续了,为 F800H~FFFFH。 在上表中,A9~A0为片内地址,最小为全“0”,最大为全 “1”,A15 ~A10的取值应分析片选电路得出。通过上表可以 容易地写出存储器地址范围,由于二进制书写太长且不直观, 所以通常写成十六进制的形式。由上表可以明显看出地址不 连续,原因是A15与A10的关系颠倒了。