Lab 1 Calculator Overview

Lab 1 Calculator Overview. CSE 45493-2 Functional Verification SUNY New Paltz. Calculator has 4 functions: Add Subtract Shift left Shift right Calculator can handle 4 requests in parallel All 4 requestors use separate input signals All requestors have equal priority

Lab 1 Calculator Overview

E N D

Presentation Transcript

Lab 1 Calculator Overview CSE 45493-2 Functional Verification SUNY New Paltz

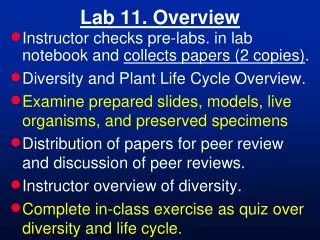

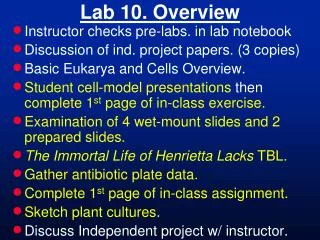

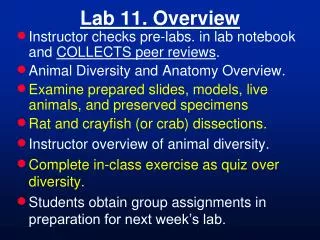

Calculator has 4 functions: • Add • Subtract • Shift left • Shift right • Calculator can handle 4 requests in parallel • All 4 requestors use separate input signals • All requestors have equal priority • Each port must wait for its response prior to sending the next command Specification

Input/Output description c_clk req1_cmd_in<0:3> out_resp1<0:1> req1_data_in<0:31> out_data1<0:31> out_resp2<0:1> req2_cmd_in<0:3> calc_top req2_data_in<0:31> out_data2<0:31> out_resp3<0:1> req3_cmd_in<0:3> req3_data_in<0:31> out_data3<0:31> out_resp4<0:1> req4_cmd_in<0:3> req4_data_in<0:31> out_data4<0:31> reset<0:7>

I/O Description • Input commands: • 0 - No-op • 1 - Add operand1 and operand2 • 2 - Subtract operand2 from operand1 • 5 - Shift left operand1 by operand2 places • 6 - Shift right operand1 by operand2 places • Input Data • Operand1 data arrives with command • Operand2 data arrives on the following cycle Calculator Input Command and Data

Outputs • Response line definition • 0 - no response • 1 - successful operation completion • 2 - invalid command or overflow/underflow error • 3 - Internal error • Data • Valid result data on output lines accompanies response (same cycle) Calculator Output Command and Data

Calculator Input/Output timing req1_cmd_in<0:3> req1_data_in<0:31> out_resp1<0:1> out_data1<0:31> Each port must wait for its response prior to sending the next command!

Clocking • When using a cycle simulator, the clock should be held high (c_clk in the calculator model) • The clock should be toggled when using an event simulator such as Model Sim • Calculator priority logic • Priority logic works on first come first serve algorithm • Priority logic allows for 1 add or subtract at a time and one shift operation at a time Other information

Other information (con't) • Resets • Hold reset(1:7) to '1111111'b at start of testcase for seven cycles. • During the reset period, outputs of the calculator should be ignored • Shift operation • Only the low order 5 bits of the second operand are used • Arithmetic operations are unsigned Calculator Design

What scenarios do we need to verify? ___________________________________________________ ___________________________________________________ ___________________________________________________ ___________________________________________________ ___________________________________________________ ___________________________________________________ Create a Test plan

Build the model • mkdir calculator1 • cd calculator1 • vsim Then put the cursor on the ModelSim main window • vlib work • vmap work /home/yang97/verification/cal1/work • vlib stdlogic • vmap stdlogic /home/yang97/verification/cal1/stdlogic • vlib ieee • vmap ieee /opt/apps01/mentor_g/modeltech/ieee • vlib grd_demo • vmap grd_demo /home/yang97/verification/cal1/grd_demo On Unix Machine

Check the waveform • Then go to pulldown menu simulate, select simulate. It will pop up a simulate window, chose design model work/demo_top to load up. Return to ModelSim main window pulldown menu View chose Signals then chose your desired signal, use Force to input stimuli. • There are 5+ bugs in the design! • How many can you find by altering the simple testcase?

Sample Do File • Create a file *.do, i.e. calc1.do --add wave -r /* add wave /demo_top/reset add wave /demo_top/c_clk add wave /demo_top/error_found add wave /demo_top/req1_cmd_in add wave /demo_top/req1_data_in add wave /demo_top/out_resp1 add wave /demo_top/out_data1 add wave /demo_top/req2_cmd_in add wave /demo_top/req2_data_in add wave /demo_top/out_resp2 add wave /demo_top/out_data2 add wave /demo_top/req3_cmd_in add wave /demo_top/req3_data_in add wave /demo_top/out_resp3 add wave /demo_top/out_data3

Do File (Continue) add wave /demo_top/req4_cmd_in add wave /demo_top/req4_data_in add wave /demo_top/out_resp4 add wave /demo_top/out_data4 force -freeze sim:/demo_top/reset 1111111 0, 0000000 700 force -freeze sim:/demo_top/c_clk 0 0, 1 {50 ns} -r 100 force -freeze sim:/demo_top/error_found(0) 0 0 force -freeze sim:/demo_top/error_found(1) 0 0 force -freeze sim:/demo_top/error_found(2) 0 0 force -freeze sim:/demo_top/error_found(3) 0 0 force -freeze sim:/demo_top/req4_cmd_in 0000 0, 0110 700, 0000 800 force -freeze sim:/demo_top/req4_data_in 16#00000000 0, 16#ffffffff 700, 16#00000000 800, 16#0 900 force -freeze sim:/demo_top/req3_cmd_in 0000 0, 0110 701, 0000 801 force -freeze sim:/demo_top/req3_data_in 16#00000000 0, 16#ffffffff 701, 16#00000001 801, 16#0 901

Do File (Continue) force -freeze sim:/demo_top/req2_cmd_in 0000 0, 0110 704, 0000 804 force -freeze sim:/demo_top/req2_data_in 16#00000000 0, 16#ffffffff 704, 16#00000002 804, 16#0 904 force -freeze sim:/demo_top/req1_cmd_in 0000 0, 0110 705, 0000 805 force -freeze sim:/demo_top/req1_data_in 16#00000000 0, 16#ffffffff 705, 16#00000003 805, 16#0 905 run 2000 • You may run your do file from VSIM by typing • do test.do