KEKTDC

KEKTDC

E N D

Presentation Transcript

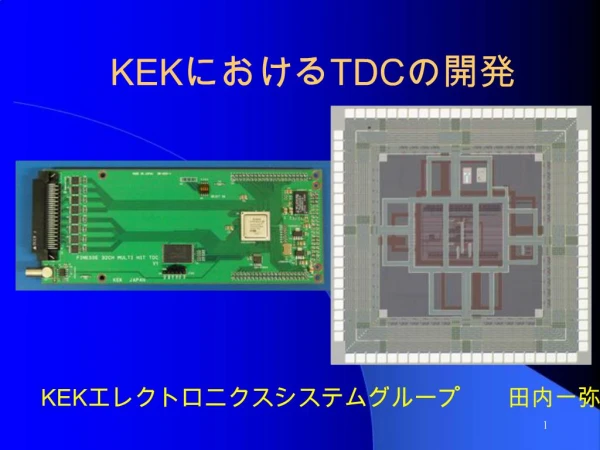

1. 1 KEK????TDC??? KEK???????????????? ????

2. 2008-11-21 2 ?? FPGA?TDC???(<1ns)

SOI?????TDC???(<30ps)

???

3. 2008-11-21 3 FINESSE 32ch Multi-Hit TDC COPPER DAQ System???????????????? ??

TDC????FPGA???????

4. 2008-11-21 4 ??(1) ???:1ns/bit

?????????:65us(16bit)

input ECL/PECL/LVDS 32ch(68pin??????????)

LEMO: COMMON START/STOP

FIFO??(HIT?):1023hit/ch

Double pulse resolution :32ns

output data:16bit counter??(?????????)?ch0??ch31??1trigger???HIT??????????

?????????????FINESSE?FIFO????HIT???

???????????COPPER?FIFO???????

5. 2008-11-21 5 ??(2) Time Window????

???CommonStop?????????

6. 2008-11-21 6 TDC in FPGA FPGA?TDC????????<1ns?????

TDC?????????????????????

7. 2008-11-21 7 TDC??? ??? FPGA?1GHz??????!

Spartan3?300MHz?Virtex5?500MHz??

8. 2008-11-21 8 ???(1) CLOCK(250MHz)????90????????4?????1ns????????

9. 2008-11-21 9 ???(2) ???CLOCK???????CLOCK???????????

10. 2008-11-21 10 Performance(1) ??:??16bit TDC tester

Range 0ns � 2000ns

11. 2008-11-21 11 Performance(2) ??FIT????????????

12. 2008-11-21 12 FPGA TDC Summary 1ns????32ch multi hit TDC?FPGA???????

????????????clock????4???8???????????????????????????FPGA?clock??????????????

13. 2008-11-21 13 High Resolution TDC (<30ps) ????

?????<30ps

????CLK??10MHz~

30MHz

??????

0.20�m SOI

???4??1.8V

??????2.4mm x 2.4mm

14. 2008-11-21 14 TMC?30ps?????? ?????<30ps

TMC(time memory cell)??

DUAL PLL?????

15. 2008-11-21 15 ?????TMC?? PLL?1???

?????????360MHz???

16??delay??1????174ps/bit???30ps???

16. 2008-11-21 16 ???????? 2??PLL?????????????????

TD2(195ps)-TD1(174ps)=21ps/bit?????

17. 2008-11-21 17 ?????????????? PLL???????????????????????????????????????????????

18. 2008-11-21 18 ??????????? ????????Delay???????????????

19. 2008-11-21 19 ????????????????

20. 2008-11-21 20 ???????? ???????????CLK????UP/DOWN????????

??????????????????????????????????

21. 2008-11-21 21 ???????????? ??CLK?ROSC?CLK????????????UP�DOWN???

22. 2008-11-21 22 ??????? Chip02:??CLK=10.0MHz~22.3MHz

Chip03:??CLK=10.4MHz~22.4MHz

Chip04:??CLK=11.8MHz~23.5MHz

23. 2008-11-21 23 CLOCK ??? RingOSC???

24. 2008-11-21 24 High Resolution TDC SUMMARY

25. 2008-11-21 25 ??? FPGA?TDC???(<1ns)

SOI?????TDC???(<30ps)