UNIT 4 BASIC CIRCUIT DESIGN CONCEPTS

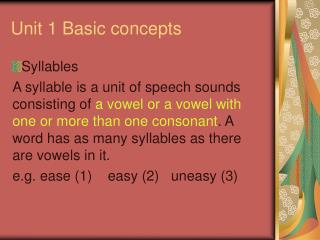

UNIT 4 BASIC CIRCUIT DESIGN CONCEPTS. ( Pucknell p:- 86-110). Each of layers have their own characteristics like capacitance and resistances Concepts such as sheet resistance Rs and a standard unit capacitance □Cg

UNIT 4 BASIC CIRCUIT DESIGN CONCEPTS

E N D

Presentation Transcript

UNIT 4BASIC CIRCUIT DESIGN CONCEPTS (Pucknell p:- 86-110)

Each of layers have their own characteristics like capacitance and resistances • Concepts such as sheet resistance Rs and a standard unit capacitance □Cg • Also delay associated with wiring, with inverters and with other circuitry may be evaluated in terms of a delay unit τ .

sheet resistance Rs • Consider a uniform slab of conduction material of resistivity ρ,of width W, thickness t, length between faces L • Consider the resistance between two opposite faces RAB= ρL/A Ω • Where area of the slab A=Wt. RAB= ρL/Wt Ω

Now, consider the case in witch L=W, that is a square of resistive material, then RAB= ρ/t =Rs • Where • Rs =ohm per square or sheet resistance • The table of values for a 5µm technology is listed below.5µm technology means minimum line width is 5µm and λ= 2.5µm.

Area capacitances of layers Standard unit of capacitance □Cg Some area capacitance calculations CAPACITANCE ESTIMATION

There are many layers and thus forms parallel plat capacitance effect • Dielectric thickness , we can calculate area capacitance as follows: • C=εo ε ins A farads D • D= thickness of the dioxide in cm • A = area of the plate in cm2 • εo = permittivity of free space-8.854x10-14f/cm • ε ins = relative permitivity of sio2=4.0 Area capacitances of layers

Typical values of area capacitance are set out in table for 5µm technology

The unit □Cg is defined as gate-to-channel capacitance of a MOS transistor having W=L=feature size □Cg was evaluated for any MOS, for example 5µm MOS circuits: Standard unit of capacitance □Cg • Area/standard square = 5µm X 5µm = ? • Capacitance value (from table) = 4 X 10-4 pF/µm2 • Thus , standard value □Cg = 25µm2 X 4 X 10-4 pF/µm2 = ?

area capacitance calculated by relative to that of a standard gate Consider the area in metal 1 Capacitance to substrate = relative area X relative C value =1.125 □Cg Consider the same area in polysilicon = ? Consider the same area in n-type diffusion = ? Some area capacitance calculations L = 20λ W=3λ

Total capacitance CT=Cm+Cp+Cg =7.20 □Cg <- 100 λ -> I <- 4 λ -> I 4λ 3 λ 1λ 2 λ 2 λ Metal Diffusion Polysilicon

Total capacitance CT=Cm+Cp+Cg= Metal 1 |<- 50 λ -> I <- 4 λ -> I <- 50 λ -> I 4λ 3 λ 1λ 2 λ 2 λ Diffusion Polysilicon • Total capacitance CT=Cm+Cp+Cg = 7 □Cg

The concept of sheet resistance and standard unit capacitance can be used to calculate the delay • consider that a one feature size poly is charged by one feature size diffusion then the delay is • Time constant τ =[1 Rs (n channel) X 1 □Cg ] • For 5µm technology • τ = 0.1 nsec DELAY τ

τ is not much differ from transit time τsd • τsd = L2 / µn Vds • Assume that Vds varies with Cg from oV to 63% of Vdd in period τ , then calculate τsd • τsd =0.13 nsec

Consider 4:1 ratio nMOS inverter The delay associated with the inverter will depend on whether it is being turned off or on Consider pair of cascaded inverters then over delay will be INVERTER DELAYS • Td= (1 + Z p.u / Z p.d) τ

Considering CMOS inverters , then equal size pull-up p-transistor and pull-down n-transistor Then Rs will asymmetry Gate capacitance is double because the input is connected to the common poly, putting both the gate capacitance in parallel..

DELAY τ • The concept of sheet resistance and standard unit capacitance can be used to calculate the delay • consider that a one feature size poly is charged by one feature size diffusion then the delay is • Time constant τ =[1 Rs (n channel) X 1 □Cg ] • For 5µm technology • τ = 0.1 nsec

τ is not much differ from transit time τsd • τsd = L2 / µn Vds • Assume that Vds varies with Cg from oV to 63% of Vdd in period τ , then calculate τsd • τsd =0.13 nsec

INVERTER DELAYS • Consider 4:1 ratio nMOS inverter • The delay associated with the inverter will depend on whether it is being turned off or on • Consider pair of cascaded inverters then over delay will be • Td= (1 + Z p.u / Z p.d) τ

Considering CMOS inverters , then equal size pull-up p-transistor and pull-down n-transistor • Then Rs will asymmetry • Gate capacitance is double because the input is connected to the common poly, putting both the gate capacitance in parallel..

INVERTER DELAYSEstimation of CMOS inverter delayRise time estimation Fall time estimation

INVERTER DELAYS • Consider 4:1 ratio nMOS inverter • The delay associated with the inverter will depend on whether it is being turned off or on • Consider pair of cascaded inverters then overall delay will be • Td= (1 + Z p.u / Z p.d) τ

Considering CMOS inverters , then equal size pull-up p-transistor and pull-down n-transistor • Then Rs will asymmetry • Gate capacitance is double because the input is connected to the common poly, putting both the gate capacitance in parallel.

Estimation of CMOS inverter delay • The inverter either charges or discharges the load capacitance CL. • Raise-time and fall-time estimations obtained by following analysis

Rise time estimation • In this condition p-device stays in saturation for entire charging period of the load capacitance CL • the p device is in saturation current given by Idsp=ßp(Vgs-|Vtp|)2 /2 ----(1)

The above current charges the capacitance and it has a constant value. The output is the drop across the capacitance, given by • Vout =Idsp x t /CL ------(2) • Let t= τr ,Vout=Vdd, Vtp=0.2Vdd and Vgs=Vdd • We have τr = 3CL /ßpVdd

Fall time estimation • Similar reasoning can be applied to the discharge of CL through the n- transistor • Making similar assumptions we may write for fall-time : τf = 3CL /ßnVdd

Summary of CMOS fall time and rise factors • Final expression we may deduce that: τr / τf = ßn / ßp • Raise time is slower by factor of 2.5 when both ‘n’ and ‘p’ are in same size • In order to achive symmetrical operation need to make Wp=2.5 Wn • The factors which affect rise-time and fall-time as follows: • τr and τf are proportional to 1/Vdd • τr and τf are proportional to CL • τr =2.5 τf for equal n and p transistor geometries

Driving large capacitance loads Super buffersBiCMOS driverCascaded inverters as drivers

The problem of driving large capacitive loads arises when signals must travel outside the chip. • Usually it so happens that the capacitance outside the chip are higher. • To reduce the delay these loads must be driven by low resistance.

Super buffers • Consider Vin=1 • Inverter formed by T1 and T2 is turned on and thus the gate of T3 is pulled down to 0V but T4 is turned on and the output is pulled down • Consider Vin=0,then the gate of T3 is allowed to rise quickly to Vdd,T4 is turned off. • T3 is made to conduct with Vdd on its gate,i.e twice the average voltage that applied to gate • Super buffers are better solution for large capacitance load delay problems

BiCMOS driver VDD R Vout 1 0 Vin CL GND

BiCMOS driver • High current drive capabilities for small areas in silicon • Working of bipolar transistor depends on two main timing components: • Tin the time required to charge the base of the transistor which is large • TLthe time take to charge output load capacitor which is less

Delay T CMOS • Critical value of load capacitance CL(crit) below which the BiCMOS driver is slower than a comparable CMOS driver BiCMOS Tin CL(crit) Load Capacitance CL

Cascaded inverters as drivers • N cascaded inverters, each one of which is larger than the preceding by a width factor f . • Now both f and N can be complementary. If f for each stage is large the number of stages Nreduces but delay per stage increases. Therefore it becomes essential to optimize. 4: f2 4: f 4:1 CL 1:1 1: f 1: f2 GND

Fix N and find the minimum value of f. • For nMOS inverters • Delay per stage = fτfor ↑Vin • or = 4fτfor ↓Vin • The delay for a nMOS pair is 5 fτ

For N=even • Td=2.5Neτ for nmos, • Td=3.5 Neτ for cmos • For N=odd

Propagation delay • Cascaded pass transistors: delay introduced when the logic signals have to pass through a chain of pass transistors • The transistors could pose a RC product delay • Ex: the response at node V2 is given by C dV2/dt =(I1-I2)= [(V1-V2)(V2-V3)]/R

Lump all the R and C we have Rtotal=nrRs ….eq-1 Ctotal=ncロCg ….eq-2 Where r=relative resistance/section in terms of Rs c=relative capacitance/section in terms ofロCg • Overall delay τd for n sections is given by τd = n2rc Long wires may be a problem with slowly rising signals

wiring capacitances • Fringing field: is due to parallel fine metal lines running across the chip for power connection. Total wire capacitance Cw=Carea+Cff • Interlayer capacitance: is due to different layers cross silicon area • Peripheral capacitance: is due to junction of two devices (regions) Total diffusion capacitance Ctotal = Carea + Cperi

Choice of layer • Vdd and Vss lines must be distributed on metal lines due to low Rs value • Long lengths of poly must be avoided because they have large Rs • The resistance effects of the transistors are much larger, hence wiring effects due to voltage divider effects b/w wiring and transistor resistances • Diffusion areas must be carefully handled because they have larger capacitance to substrate.