PADS Power Aware Distributed Systems Middleware Techniques and Tools

300 likes | 414 Views

This document outlines methods for extending the dynamic power range in sensor networks, focusing on the transition from low-power monitoring modes to high-activity intervals. Key topics include architectural approaches, middleware techniques, and development of power-aware algorithms for effective resource management. The research aims for significant improvements in power efficiency through innovative scheduling approaches and tools for evaluating power management strategies. Accomplishments highlight ongoing work in power measurement, adaptive trade-offs, and the integration of multimedia data within sensor platforms.

PADS Power Aware Distributed Systems Middleware Techniques and Tools

E N D

Presentation Transcript

PADSPower Aware Distributed SystemsMiddleware Techniques and Tools USC Information Sciences InstituteBrian Schott, Bob Parker UCLAMani Srivastava Rockwell Science CenterCharles Chien

PADS Project Q: How can you extend the dynamic power range of sensor networks from quiescent months of monitoring to frenetic minutes of activity? • Architectural Approaches • Power Aware Research Platform Testbed • Deployable Power Aware Sensor Platform • Middleware, Tools, and Techniques • Power Aware Resource Scheduling in RTOS • Techniques for Network-Wide Power Management • Power Aware Algorithms • Multi-Resolution Distributed Algorithms UCLA

Introduction to UCLA PADS Team • PI • Mani Srivastava • Other faculty • Rajesh Gupta • Students • Sung Park, Pavan Kumar, Paleologos Spanos, Vijay Raghunathan, Cristiano Ligieri, and Ravindra Jejurikar

Research Agenda • Broad goals • Middleware techniques for “JIT” power through coordinated scheduling and power management of computing and communication resources locally at a sensor node (RTOS) as well as globally in a sensor network (protocols) • Tools for evaluating and designing the power management techniques • Target 10-30x gain in power efficiency • Specific subtasks • Power management within a sensor node • Power-aware RTOS scheduling under timing constraints • Resource management with energy-speed and energy-accuracy control knobs • Tools for RTOS power management evaluation, and power-aware kernel synthesis • Network-wide power management • Network resource allocation for global power management • Power-aware network protocols • Hybrid sensor network simulation framework for power vs. quality evaluation of network level power management techniques and protocols • Power management with multimedia sensor data • Power characterization, extension of PADS techniques to streaming multimedia • Integration with sensor nodes (Rockwell nodes, research platform)

Accomplishments Since Last Review • Power measurement, analysis, and modeling • Power models for SensorSim • Power analysis of various nodes in the lab • Power management of sensor node processor via RTOS • Adaptive power-fidelity trade-off via prediction of run-time • Implementation on eCos • Validation on multimedia and sensor processing tasks • Development of generic API to power-aware OS (on-going) • Tools to evaluate power management strategies (on-going) • Power management of sensor node radio • Development of the “dynamic modulation scaling” concept • Various energy-aware wireless packet scheduling techniques • Power-aware sensor node architecture • Energy-efficient packet forwarding architecture for sensor nodes • Experimental validation via lab prototype • Publications • One at International Conference on VLSI Design (published) • Three at ISLPED (accepted) • One at Sigmetrics (accepted) • One at Winter Simulation Conference (accepted) • Some more submitted

DAQ I. Sensor Network Power Measurement, Analysis & Modeling SensorViz Power Measurements Data from SensIT Experiments Power Models Node LocationsTarget TrajectoriesSensor ReadingsUser TrajectoriesQuery Traffic SensorSim Simulator

User Node Sensor Node Sensor Node Sensor Node SensorSim Architecture Sensor Node Functional Model User Application User Node SensorWare Network Stack Power Model Network Layer Sensor App Battery Model MAC Layer Sensor Stack3 Network Stack Physical Layer Sensor Stack2 Sensor Layer Radio Network Layer Sensor Layer Sensor Stack1 Wireless Channel Physical Layer CPU Sensor Layer MAC Layer Physical Layer Wireless Channel Physical Layer ADC (Sensor) Physical Layer Sensor Channel3 Wireless Channel Sensor Channel2 Sensor Channel1 Sensor Channel Target Node Target Application Target Node Sensor Stack Sensor Layer Physical Layer Sensor Channel

Power analysis of sensor nodes: Where does the power go? • High-end sensor node: Rockwell WINS nodes • StrongARM processor • Connexant’s RDSSS9M 900MHz DECT radio (128 kbps, ~ 100m) • Seismic sensor • Low-end sensor node: Experimental node similar to Berkeley’s COTS motes • Atmel AS90LS8535 microcontroller • RF Monolithic’s DR3000 radio (2.4, 19.2, 115 kbps, ~ 10-30m) • No sensors (but microcontroller has ADC)

Power Analysis of Rockwell’s WINS Nodes (Measurements) Summary • Processor • Active = 360 mW • doing repeated transmit/receive • Sleep = 41 mW • Off = 0.9 mW • Sensor = 23 mW • Processor : Tx = 1 : 2 • Processor : Rx = 1 : 1 • Total Tx : Rx = 4 : 3 at maximum range • comparable at lower Tx

Power Analysis of Experimental Node (Measurements) Note • All powers in mW • Microcontroller (with ADC) • Active = 8.7 mW • Idle = 5.9 mW • Off = 3 mW

Some Observations from Power Analysis • In WINS node, radio consumes 33 mW in “sleep” vs. “removed” • Argues for module level power shutdown • Tx and Rx power • Rx power within 40% of maximum Tx power • Under certain circumstances, Tx power < Rx power! • Argues for: • MAC protocols that do not “listen” a lot • Low-power paging (wakeup) channel • Processor power fairly significant (30-50%) share of overall power • Sensor transducer power negligible • Use sensors to provide wakeup signal for processor and radio

II. Power Management for Wireless Sensor Node Processor Sensors Radio CPU Dynamic Voltage Scaling Scalable Signal Processing Dynamic Modulation Scaling Coordinated Power Management Power Manager (Minimalist) Real Time Operating System

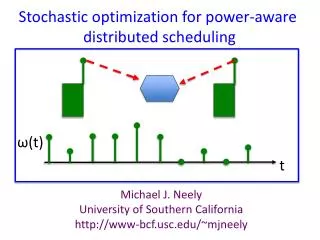

Predictive DVS for Adaptive CPU Power-Fidelity Tradeoff • Wireless systems resilient to packet loss • Time varying computational load Proactive DVS strategy involving prediction oftask instance runtime Power aware RTOS for embedded applications Normalized energy Average Exec. Time / Worst Case Exec. Time • Up to 75% reduction in energy over worst case based voltage scheduling with negligible loss in fidelity (up to 4% deadline misses) on variety of multimedia and signal processing tasks

Implementation • Implemented under eCoS using Intel’s Assabett board • DVS-enabled eCoS on iPaQ to be ready soon

Power-aware API Application Threads Why? • Ease of porting to different processors • Allow apples-to-apples comparison on the same set of applications To OS:task: set period, set deadline, set WCET, set actual remaining execution time, set hard/soft, create task instanceinterrupt handler: create task instance To Task Instance:get remaining execution time, kill Power-Management Functions eCoS Normal eCoS System Calls Power-awareTask Scheduler PowerRelatedTask DataStructures DVS HAL Hardware

Tool to Evaluate PowerManagement Strategies • Current approach: simulation • Simulation framework using PARSEC to compare different power management strategies under various types of task schedulers • Problem: long simulations, biased by choice of specific task set • Ongoing: analysis-based tool • Based on “competitive analysis” to derive worst case bounds on improvement yielded by a power management strategy • metric: competitive ratio = how much worse than optimal off-line strategy • Take into account transition cost (power, time) • Implementation based on formal model checking tool which is used as a simulator for power management policy • Problems: excessive memory hog, only a bound • Future: integrate analysis and simulation

III. Dynamic Power Management of Sensor Node Radios Sensors Radio CPU Dynamic Voltage Scaling Scalable Signal Processing Dynamic Modulation Scaling Coordinated Power Management Power Manager (Minimalist) Real Time Operating System

Ebit (J) RS (MHz) b Tbit (s) RS (MHz) b Dynamic Modulation Scaling • Energy and delay of data transmission depend on modulation settings • Tradeoffs for QAM • adapt b (number of bits per symbol) • Operate at maximum RS that can be implemented efficiently • Similar tradeoffs are possible for other scalable modulation schemes • PSK, DPSK • ASK • OFDM

Voltage scaling Modulation scaling V b f Rb Ebit (J) b = 6 b = 4 b = 2 Tbit (s) Analogy Between Dynamic Voltage and Modulation Scaling • Scaling modulation on the fly results in energy awareness • Strong analogy between modulation scaling and voltage scaling • Low power techniques, like parallelism • Packet scheduling like task scheduling • Other power management techniques

Analogy Between Dynamic Voltage and Modulation Scaling Radio Digital Hardware

Eav (J) Queue Radio Processor R-DPM Tav (s) Queue-Based Dynamic Modulation Scaling • Radio Dynamic Power Management (R-DPM) for best-effort data packet service • Adapt modulation based on number of packets in the queue • Different {queue, b}-settings result in different points on the energy-delay tradeoff

Energy Aware Real Time Packet Scheduling • Analogous to RTOS task scheduling • Exploit variation in packet length to perform aggressive DMS static staticdyn staticdyn stretch Energy savings (%) Lavg/Lmax • Up to 69% reduction in transmission energy Framework for coordinated power management of computing and communication sub-systems

ecomb escaling (J/packet.hop) Data combining tradeoff Modulation scaling tradeoff Combining tcomb tscaling(s/packet.hop) Data Combining versus Modulation Scaling • Data combining • Gains depend on correlation in time or space • Reduction in packet size or increase in reliability • Modulation scaling • Overall tradeoff

MultihopPacket CommunicationSubsystem Rest of the Node GPS RadioModem MicroController CPU Traditional Approach Sensor ACCEPT FORWARD DROP Action 65.567 0.133 % of received packets 34.300 IV. Power-aware Sensor Node Architecture • Problem: radio often simply relays packets in multihop network • NS-2 simulation: 1000x1000 terrain, 30 nodes, DSR, CBR traffic from random SRC and DEST • Traditional approach: main CPU woken up, packets sent to it across serial bus • power hungry computing and communication operations

Energy Impact of Our Packet Forwarding Architecture …zZZ • Simple packet processor in the radio • Packets are redirected as low in the protocol stack as possible • Measured + simulated results using Atmel AVR and Triscend E520 with Rockwell Nodes • Lower latency (44 ms) • once PrFW > 3% PrAC • Lower energy (savings) • Average of 17.5 mJ/packet with Atmel AVR • Average of 7.5 mJ/packet with Triscend E520 MultihopPacket CommunicationSubsystem Rest of the Node GPS RadioModem MicroController CPU Sensor Our Approach

CPU MCU a Ediff 1167*PMCU 16*PMCU WINS (351mW) WINS (351mW) Atmel AVR (15mW) E520 (470mW) 0.747 23.4 Energy Savings • Difference in Energy consumption is also dominated by the Serial port crossing penalty and the relation (a) of the power consumption of the Microcontroller and the Sensor CPU Energy difference due to ACCEPT Energy difference due to FWD Serial Port crossover penalty For Simulation Data

Near-term (Summer) Plans • Power-management of CPUs • Power analysis of SA-2 with variable voltage • Soon getting SA-2 board being donated by Intel • Finish power-aware API • Power-management of radios • Further development of energy-aware packet scheduling • Better understanding its utility • So far power management under traffic variations only • Next: combine traffic and channel variations • Some validation using prototype, perhaps using FPGA • Coordinated CPU& radio power management • Modeling • ARL sensor data and algorithms • Incorporate into sensorsim • Combined modeling of CPU and radio power consumption(Joulestrack + Sensorsim?) • Node architecture • SA-2 and TMS320C55