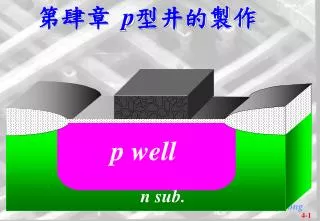

第肆章 p 型井的製作

第肆章 p 型井的製作. p well. n sub. 定義 p 型井. 上 HMDS 後送入 90℃ 烤箱 30 秒。 上光阻。 軟烤 (100℃ 烤箱 90 秒鐘 ) 。 曝光。 硬烤 (120℃ 烤箱 90 秒鐘 ) 。 顯影。 硬烤 (100℃ 烤箱 90 秒鐘 ) 。 檢查 (ADI) 。. PR. PAD oxide. 400 ± 40Å. n well. 1.5 m m. p< 100 >. 開始離子佈植. 硬烤 (125℃ 烤箱 20 分鐘 ) 。

第肆章 p 型井的製作

E N D

Presentation Transcript

第肆章 p型井的製作 p well n sub.

定義p型井 • 上HMDS後送入90℃烤箱30秒。 • 上光阻。 • 軟烤(100℃烤箱90秒鐘) 。 • 曝光。 • 硬烤(120℃烤箱90秒鐘) 。 • 顯影。 • 硬烤(100℃烤箱90秒鐘) 。 • 檢查(ADI) 。 PR PAD oxide 400±40Å n well 1.5mm p<100>

開始離子佈植 • 硬烤(125℃烤箱20分鐘) 。 • 硼離子(B11)佈植,180keV,7×1012 ions/㎝2,7o角。 B11 7×1012 180kev ,7o角 PR PR PAD oxide 400±40Å p<100> n well p<100>

去除光阻與驅入 • 去除光阻(先以O2電漿灰化光阻再去除,800瓦、30分鐘 • 、80℃) • 以卡洛氏酸去除光阻(30分鐘) • 以100:1的HF預先浸泡清洗(去除新長出來的原生氧化 • 層)30秒。 • 清洗晶片:1. 卡洛式酸清洗 90秒 • 2. NH4OH+H2O2+H2O 90秒 • 3. HCl+H2O2+H2O 90秒 • 晶片送入爐管加熱把佈植的硼作驅入 1000 800 昇溫 氣體通N2 推入晶圓 氣體通N2 降溫 氣體通N2 拉出晶圓 氣體通N2 驅入----氣體通N2

硼驅入 p well深度大約3mm PAD oxide 400±40Å 1.5mm n well 3.0mm p well p<100> 以100:1的HF去除氧化層(30秒) n well p well p<100> 清洗晶片:1. 卡洛式酸清洗 90秒 2. NH4OH + H2O2 + H2O 90秒 3. HCl + H2O2 + H2O 90秒

長墊層二氧化矽 PAD oxide 150±15Å 開始乾氧氧化 氣體通O2 靜置(等穩定) 氣體通N2+O2 拉出晶圓 氣體通N2 n well 920 p well p<100> 800 推入晶圓 氣體通N2+O2 降溫 氣體通N2 昇溫 氣體通N2+O2

沉積氮化矽層 • 780℃ SiH2Cl2/NH3沉積氮化矽 1500±150Å。 • 上HMDS後送入90℃烤箱30秒。 • 上光阻。 • 軟烤(100℃烤箱90秒鐘) 。 • 曝光 PR n well p well Si3N4 p<100> SiO2

氮化矽圖案 • 硬烤(120℃烤箱90秒鐘) 。 • 顯影。 • 硬烤(125℃烤箱20分鐘) 。 • 檢查(ADI) 。 • 硬烤(115℃烤箱30分鐘) 。 PR n well Si3N4 p well SiO2 p<100>

熱氧化與沉積氧化層 • 熱氧化是利用矽晶圓本身與外面提供的氧氣(乾氧)或水氣 • (溼氧)產生氧化;因此矽晶圓本身會參予反應,在第二章 • 的53頁就提到“每長出厚度 t 的二氧化矽時,就會耗損掉 • 厚度大約 0.45t 的矽,因此二氧化矽是同時往上與往下成 • 長出來” 。 • 沉積是利用外界提供二氧化矽的原料,藉由物理或化學的 • 方法,長在矽晶圓上面,因此矽晶圓本身並不會參予反應 二氧化矽 二氧化矽 矽晶圓 矽晶圓 矽晶圓 熱氧化 反應前的矽晶圓 沉積後的

薄膜特性 • 薄膜特性: • 好的階梯覆蓋能力 • 具有充填高深寬比間隙之能力 • 好的厚度均勻性 • 高的純度及密度 • 理想配比可控制 • 具有低應力的高薄膜品質 • 電性佳 • 基板材料和薄膜附著性優越

IC的多層金屬化-1 氮化矽 氧化層 金屬Ⅱ ILD 金屬Ⅰ 氧化層 多晶矽 多晶矽 場氧化層 p+ p+ n+ n+ p- p- n well 金屬前氧化層 側壁氧化層 p磊晶層 閘極氧化層 p+矽基板

IC的多層金屬化-2 保護層(PD) 金屬層間介電質(IMD) ILD-6 Al-Cu ILD-5 M-4 ILD-4 M-3 ILD-3 M-2 ILD-2 WCVD M-1 ILD-1 VIA 多晶矽閘極 LI金屬 LI金屬 LI氧化層 STI p+ n+ n+ STI n+ STI p+ p+ STI n well p well n well p磊晶層 p矽基板

薄膜沉積過程 1. 氣體分子到達表面。 2. 源材料於晶圓表面移動。 3. 源材料於晶圓表面反應。 4. 成核。 5. 島狀物成長。 6. 島狀物成長合併。 7. 連續薄膜。 氣體分子 成核 表面反應 連續薄膜 島狀物聚結 矽基板

CVD的基本化學反應與觀念 • 化學作用或熱分解(裂解)。 • 薄膜的材料由外加氣體供應。 • CVD製程的反應物必須為氣相的形式。 • 基本化學反應: • 熱裂解:化合物分解 (破壞鍵結或分解),如果以熱的方式, • 則處於無氧的環境。 • 光分解:化合物分解,以輻射能的方式分解鍵結。 • 還原:由分子與氫作用產生化學反應。 • 氧化:原子或分子與氧進行化學反應。 • 氧化還原:結合還原反應與氧化反應,產生兩種新的化合物。

CVD反應爐 APCVD LPCVD PECVD 壓 力 閥 反應氣體1 三區段加熱線圈 反應氣體 鈍氣 RF 電源 反應氣體2 反 應 爐 薄膜 晶圓 電漿 由 真 空 邦 浦 抽 出 氣體注入形式 內 部輪 廓 熱 電 偶 反應氣體 矽 晶 片 尖峰熱電偶 (外部、控制) N2 N2 N2 N2 N2 N2 氣 體 進 入 加熱板 真 空 邦 浦 抽 出 晶圓 溫度 溫度均勻區 加熱器 架構形式 爐管長度

APCVD、LPCVD與PECVD 性質 APCVD LPCVD PECVD 壓力(Torrs) ~760 0.1~1 1~10 沉積溫度(℃) 700~800 300~400 組成 SiO2或Si3N4 Si3N4 SixNyHz 階梯覆蓋 除TEOS外,其餘都不好 良好 均勻 23℃在矽晶片上的應力(達因/ ㎝2) 1.2~1.8×1010(張力) 1~8×109(張力或壓縮力) 適用性 不適合沉積IMD 適合沉積PMD 適合沉積IMD、PD、PMD 特點 可使用電漿產生的氟自由基清洗反應爐

CVD傳輸及反應圖 1)反應物之質量傳輸 CVD反應爐 氣體輸送 7)副生成物的吸解 8)副產物移除 2)薄膜先前 物反應 副產物 出口 3)氣體分子 擴散 5)先前物擴散進入基板 連續薄膜 6)表面反應 4)先前物吸附 矽基板

CVD氣體流 氣體流 反應物擴散 反應產物 沈積之薄膜 矽基板 矽基板

晶圓表面上之氣流動態 氣體流 氣體流 邊界層 滯留層 矽基板 矽基板 氣體分子或原子到達邊界層,就會開始產生滯留的狀態, 甚至停留了下來,磊晶上去。

氣體的表面遷移率 • 氣體擴散到邊界層。 • 邊界層的氣體被晶片表面吸收與移動。 • 氣體在晶片表面移動的能力稱為表面遷移率。 • 表面遷移率將影響到薄膜的階梯覆蓋與間隙填充能力。

CVD化學反應動力學-1 化學反應速率方程式為: A為常數 Ea為活化能 k為波滋漫常數 T為晶圓基版溫度 ∵化學反應速率∝e溫度 而且沉積速率(D.R.)∝化學反應速率(C.R.) 沉積速率(D.R.) ∝邊界層源材料擴散速率(D) 沉積速率(D.R.) ∝晶片表面吸附率(A.R.) Ea 反應前 反應後 DH

CVD化學反應動力學-2 沉積速率(D.R.)區間: 在氣相成核區沉積,將造 成大量的粒子污染晶圓與 機台。 質量傳輸控制區沉積的優 點是沉積速率與溫度無關 低溫區 中溫區 高溫區 對溫度很敏感 對溫度較不敏感 對溫度很敏感 表面反應限制區 質量傳輸控制區 氣相成核區 斜率= E k / 不理想的沉積區 理想的沉積區 不理想的沉積區 a 表面 反應 限制 區 質量傳輸控制區 氣 相 成 核 區 ln D.R. 沉積速率 , [B][C]表晶片表面的源材料濃度 1/ T

表面吸附 • 源材料擴散過邊界層,並到達晶片表面,可能會被晶 • 片表面吸附,它的吸附機構分成: • Ⅰ、物理吸附。 • Ⅱ、化學吸附。 束縛能 晶 片 表 面 物理吸附 到晶片表 面距離 束縛能低 化學吸附 束縛能高

表面吸附-物理、化學吸附 • 物理吸附的束縛能比較低,每個分子的吸附能量低於 • 0.5eV ,它的力量有凡得瓦力與電偶極-電偶極彼此 • 間的吸引力,大約 400℃ 或離子轟擊就足以瓦解物理 • 吸附力,並讓分子離開晶片表面,因此它比化學吸附 • 的表面移動率來的高。 • 化學吸附的束縛能比較高,晶片表面會與源材料分子 • 形成化學鍵,每個分子的吸附能量高於 2eV,由於吸 • 附能量比較高,所以 450℃ 以下也無法打斷它的化學 • 鍵,不過離子轟擊的能量大約有 10~20eV ,應該足以 • 打斷化學鍵,並將源材料分子釋放,由於化學鍵束縛 • 能比較高,因此表面移動率很低。

表面吸附-矽烷 • 矽烷的分子結構是一種正三角錐形結構,矽原子恰好 • 位於這個正三角錐形結構的正中心位置,因此不會對 • 基板形成任何的物理或化學吸附,不過矽烷很容易分 • 解成SiH3、SiH2或 SiH,並產生活性很高的自由基, • 因此會與基板形成化學吸 • 附或化學鍵。 • 基於上述的理由,矽烷很 • 容易產生投影片29頁所提 • 到的懸突物,造成空洞或 • 階梯覆蓋不佳。 H H Si H H

CVD薄膜的階梯覆蓋 CVD薄膜 a c 結構 結構 h b d w 矽基板 a d 側壁階梯覆蓋= 底部階梯覆蓋= a b - ( ) c b 相似性 = 懸突= b h b 深寬比= w c

到達角度 • 右下圖的A有最大的角度(270o) ,C的角度最小(90o) 。 • 氣體分子或原子材料到達邊界層,角A的角度最大,因此角 • A的氣體分子或原子材料會累積的最多;甚至產生懸突物。 • 如果氣體分子或原子材料的表面遷移率比較大的話,角A產 • 生的懸突物將移動到別的地方,形成類似左下圖的均勻分佈 厚度均勻 均勻階梯覆蓋 不均勻的階梯覆蓋 180° 懸突物 270° B A 90° C

到達角度的修正 • 藉由蝕刻的技術,將接觸開口蝕刻程錐形角度(如下圖), • 以便達到更大的到達角度,能讓一些 CVD 製程更容易將 • 接觸窗口的空洞填滿。 較小到達角度 較大到達角度 磷玻璃 氮化矽 二氧化矽 矽基板

薄膜沈積的深寬比 • 薄膜沈積的深寬比越大,表示洞穴的開口越小,因此間 • 隙越不容易填滿。 2 1 500 Å 250 Å h 深寬比= = 深寬比= w D 500 Å h 500Å w 250Å

空洞的形成 • 懸突物是因為到達角度效應與低遷移率所造成的。 • 當懸突物薄膜厚度增加,將使得到達角度增加而更加惡化。 • 當兩邊的懸突物相靠攏,甚至合併,將會使下面的空隙形成 • 空洞。 • 空洞內的氣體將會腐蝕積體電路內的材料,造成可靠性的問 • 題。 • 減少製程的壓力,以提高源氣體材料的平均碰撞路徑,可以 • 有效減少到達角度與改善階梯覆蓋,因此 LPCVD 階梯覆蓋 • 效果優於APCVD的階梯覆蓋效果。 空洞 金屬 金屬 介電質 介電質 介電質 金屬 金屬 金屬 金屬 矽基板 矽基板 矽基板

階梯覆蓋、壓力與移動率 • 高表面遷移率會有好的階梯覆蓋,因此選擇高表面遷移率 • 的材料,將有效解決階梯覆蓋的問題。 • 高表面遷移率也有好的似型性的優點(下圖最右邊)。 • 溫度也能提供源材料破壞吸附鍵所需的能量,以提高表面 • 遷移率。 • 對 PECVD 而言,電漿相當於提供能量讓源材料從基片表 • 面釋放與提高表面遷移率,因此PECVD不需要太高的製程 • 溫度。 金屬 金屬 金屬 矽基板 矽基板 矽基板 APCVD 低遷移率 LPCVD 低遷移率 高遷移率

氬離子的濺射 氬離子的濺射 • 濺射是類似蝕刻製程,一般都在30mTorr下,氬離子轟擊 • 晶圓表面,並移除一部份表面介電質。 • 被轟擊而移除的表面介電質將被真空邦浦抽離開反應爐。 • 濺射的蝕刻率很低,不過階梯角落的薄膜蝕刻率比一般表 • 面處的薄膜蝕刻率來的快。階梯角落的薄膜蝕刻的平面斜 • 率大約為45度左右。 • 濺射是類似蝕刻製程,一般都在30mTorr下,氬離子轟擊 • 晶圓表面,並移除一部份表面介電質。 • 被轟擊而移除的表面介電質將被真空邦浦抽離開反應爐。 • 濺射的蝕刻率很低,不過階梯角落的薄膜蝕刻率比一般表 • 面處的薄膜蝕刻率來的快。階梯角落的薄膜蝕刻的平面斜 • 率大約為45度左右。 Ar+ Ar+ Ar+ Ar+ Ar+ Ar+ Ar+ Ar+ 被移除掉的介電質 被移除掉的介電質 45o 45o 介電質 介電質 矽基板 矽基板

氬離子濺射介電質的回蝕刻 沉積 沉積 金屬 金屬 矽基板 矽基板 Ar+Ar+Ar+Ar+Ar+Ar+Ar+ 氬離子濺射條件: 壓力(mTorr) 30 蝕刻 金屬 RF功率(W) 300 磁場(G) 50 矽基板 流量(sccm) 50 沉積 / 蝕刻 / 沉積

薄膜的間隙填充-1 • 當有懸浮產生,就可能產生空洞;因此利用氬離子濺射 • 蝕刻的方法(上一頁投影片),將晶片的懸浮物回蝕刻消 • 除,並將開口放大,以提高到達角度(投影片第29頁), • 如此可以將間隙回填,這個方法稱為沉積 / 蝕刻 / 沉積 • 法,這方法一般都用在IMD製程。 註:未掺雜的矽玻璃(USG) USG USG USG Al-Cu Al-Cu Al-Cu 矽基板 矽基板 矽基板 沉積 回蝕刻 沉積

薄膜的間隙填充-2 • 高表面遷移率會有好的階梯覆蓋與似型性,在下圖中, • 薄膜幾乎可以完整的把間隙填滿。O3與TEOS CVD與鎢 • 的CVD就屬於這種。 • 黏附係數越低的源材料,它的表面遷移率就會越大,因 • 此像TEOS、WF6、SiH4的階梯覆蓋與似型性都很好。 金屬 金屬 金屬 金屬 金屬 金屬 源材料 SiH4 SiH3 SiH2 SiH TEOS WF6 矽基板 矽基板 矽基板 黏附係數 3×10-4~3×10-5 0.04~0.08 0.15 0.94 10-3 10-4

薄膜的間隙填充-3 • 高密度電漿CVD製程的特色是沉積與濺射蝕刻可以同時 • 在反應爐內完成,缺點是沉積的速度太慢。 • 高密度電漿CVD的壓力大約幾個mTorr,透過高密度電 • 漿的轟擊消除掉懸突物(所以金屬上面的介電質呈現三角 • 形),並且打開較大到達角度,再從底部不斷的往上沉積 • 。 金 屬 金 屬 金 屬 金 屬 金 屬 金 屬 金 屬 金 屬 金 屬 矽基板 矽基板 矽基板

TEOS-1 • TEOS中文為四乙氧基矽烷。 • TEOS的移動率很高,因此以TEOS作為CVD • 原料的階梯覆蓋率與似型性極高。 H H H C H H C 100 O H H H H H O C O C 30 C Si C H Vapor Pressure (Torr) H H H H O 10 H C H 3 C H H 1 H 10 20 30 40 50 60 70 80 90 100 110 Temperature (°C) TEOS蒸氣壓 TEOS分子式

TEOS-2 • TEOS應用在STI、側壁空間層、PMD與IMD。 • TEOS的移動率很高,因此以TEOS作為CVD原料的階梯 • 覆蓋率與似型性極高。 • TEOS的製程系統有(a)熱沸式(b)氣泡式(c)注入式三種。 控制器 加熱氣體管線 加熱氣體管線 載氣 邦浦 控制器 載 氣 控制器 加壓 氣體 反應爐 注入 閥 反應爐 控制器 控制器 液態 TEOS TEOS 邦浦 液態 TEOS 反應爐 恆溫烤箱 載氣氣泡 恆溫烤箱 邦浦 注入式 熱沸式 氣泡式

O3-TEOS USG-1 400℃,O3+TEOS USG 應用在 STI 或 IMD。O3比例多,會有較好的薄膜品質,但若TEOS的比例太低,沉積的速度又太慢 左下圖的TEOS階梯覆蓋相當完美,薄膜沈積的相當均勻。 右下圖的TEOS空洞間隙填滿也相當完美,幾乎完全看不到有任何的空隙。 TEOS的階梯覆蓋 TEOS的空洞間隙填滿

O3-TEOS USG-2 • STI 以 O3 + TEOS的反應溫度大約550℃。 • IMD以 O3 + TEOS的反應溫度大約400℃。 • 使用O3 + TEOS 製程,卻都還需要一次PECVD的原因是: • ①因為STI 以 O3 + TEOS 的氧化層是多孔,而且會吸收水氣 • ,所以製程上都還需要用一次PECVD來封密隔離水氣。 • ②因為以 O3 + TEOS 製程做出的氧化層張力比較大,因此需 • 要一層有壓縮力的PECVD來減緩張力。

PECVD RF產生器 電極 1.反應物進入反應爐 PEVCD反應爐 氣體傳送 RF電場 7.副產物吸解 8.副產物去除 2.藉由電場將反應物分解 抽出 副產物 3.薄膜先前物形成 5.先前物擴 散入基板 連續薄膜 6.表面反應 4.先前物吸附 矽基板 電極

PECVD TEOS-1 • PECVD + TEOS + 氬濺射可以用來當成類似投影片35頁 • 的沉積 / 蝕刻 / 沉積法,做為填滿空隙與平坦化用。 • PECVD + TEOS USG 用在當成 IMD 的自旋塗佈的氧化 • 矽與 O3 + TEOS USG 的阻擋層或覆蓋層。 • PECVD TEOS也可以用在PMD 製程中的PSG與BPSG。 • 反應式如下: • 不過PECVD的電漿可能傷害到閘極氧化層,因此大多數製 • 程是選擇O3 + TEOS CVD BPSG 或 PSG 。 TEPO

PECVD TEOS-2 • 氟矽玻璃( FSG )的介電係數(3.5~3.8)比 USG 的介電係數 • (4.0~4.2)低,因此作成IMD或PMD的材料,它的寄生電 • 容值會比較小,元件傳導線的速度會比較快。 • FSG CVD 反應方程式為: • FSG、SiO2與SiF4的特性比較: SiF4 SiOxFy(FSG) SiO2 氣態 固態 固態 er ~1 3.2<er<3.8 er = 3.9 er比較小且F容易外洩 F比較多 F比較少 er比較大

PECVD TEOS-3 • FSG的填空能力比USG好,特別是間隙的角落。 • 若利用PECVD TEOS SiF4,就可以不用回蝕刻,並可以 • 作出無空隙0.65mm的製程,如果有配合回蝕刻,將可以 • 作出無空隙0.35mm的製程。 CF4 + O2 + 濺射蝕刻平坦化 PECVD TEOS氧化矽沉積 平坦化回蝕刻

PECVD TEOS-4 • 當增加 TEOS 的溫度時,從下圖看到它的沉積率隨溫度增加 • 而增加,但溫度超過300℃左右,沉積率反而下降。一般沉積 • 製程時候,所採用的溫度大約在400~550℃左右,可以看到沉 • 積率是下降的。 • TEOS 隨溫度超過300℃左右,沉積率反而下降的原因是因為 • TEOS製程是物理吸附作用,因此吸附力很小,鍵能也很低, • 當溫度超過 300℃ 時,溫度 • 對吸附力的影響非常大,並 • 因從溫度穫得的能量得以克 • 服微弱的鍵能,而離開表面 • ,因此才有溫度越高,沉積 • 率反而下降的現象。 400~550℃ 製 程 窗 口 增加化學 反應速率 沉積速率 減低源材料 吸收反應物 吸附速率 溫度

PECVD TEOS-5 • PECVD TEOS 是在質量傳輸限制區內操作(投影片第24頁), • 瓶頸是TEOS的流量多寡控制,因此增加TEOS流量,將有效 • 提高沉積速度。 • 從第二章第69頁投影片的圖(本頁右下圖)看到當矽過量,理論 • 上,折射率也應該會增加,不過由於 TESO 分子(本章投影片 • 第39頁)中的矽與四個氧原子鍵結,因此增加 TEOS 流量並不 • 會讓折射率增加,從結果來看,它的折射率只有薄膜密度改 • 變才會有些許的改變,而且 • 是越緻密,折射率才越高。 折射率 4.0 氧過量 氮過量 複晶矽 3.0 氧過量 氮過量 氮化物 2.01 Si3N4 矽過量 氮氧化矽過渡區 1.46 氮過量 矽過量 SiO2 1.0 氧過量 氧化物 沉積速率 折射率 製程窗口 TEOS流量

PECVD TEOS-6 • 當增加 TEOS 流量時,薄膜厚度應該也會增加,平均每 • 單位厚度被離子轟擊的數量會比較少,因此它的收縮應 • 力會比較小,而且薄膜也比較鬆弛,因此蝕刻的速度比 • 例也會增加(請參考左下圖)。 • 對 PECVD TEOS 而言,增加RF功率,沉積速度會先增 • 加,並逐漸減緩,當RF功率非常高的時候,沉積速度會 • 開始減小。不過隨RF功率增加,離子撞擊的力量也會增 • 加,它的收縮應力也會不斷的增加(請看右下圖)。 離子轟擊 降低反應 物吸附 自由基 增加反 應速率 沉積速率 壓縮式應力 濕蝕刻速率 製程窗口 TEOS流量 RF功率

矽烷與PECVD-1 • PECVD 對矽烷製程,溫度越高,矽烷擴散速度越快 (與 • TEOS不同,因為矽烷是化學性吸附,所以吸附力很大, • 鍵能也很高,溫度在400℃對矽烷的吸附速度幾乎沒有影 • 響 ),沉積速度也越快,而且階梯覆蓋與似型性也越好。 沉積速率 對溫度不 敏感區域 沉積速率 對溫度敏 感區域 沉積速率 溫度 沉積速率 製程窗口 溫度