Automatic generation of software -based functional failing test

220 likes | 419 Views

Automatic generation of software -based functional failing test. Giovanni Squillero. GOAL. To propose a methodology for automatically devising a functional failing test for a microprocessor, without any information about the underlying microarchitecture. Outline. Background

Automatic generation of software -based functional failing test

E N D

Presentation Transcript

Automatic generation of software-based functional failing test Giovanni Squillero

GOAL • To propose a methodology for automatically devising a functional failing test for a microprocessor, without any information about the underlying microarchitecture giovanni.squillero@polito.it

Outline • Background • (Functional) failing tests • Proposed methodology • Experimental evaluation • Conclusions giovanni.squillero@polito.it

Background giovanni.squillero@polito.it

“Very few chips ever designed function or meet their performance goal the first time” • R. McLaughlin, S. Venkataraman, C. Lim (2009) giovanni.squillero@polito.it

Background Pre-silicon DESIGN Post-silicon Tape out PROTOTYPE giovanni.squillero@polito.it

Functional failing test AF56ED90 AF96FB90 giovanni.squillero@polito.it

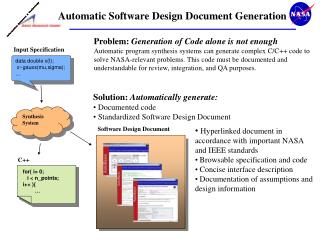

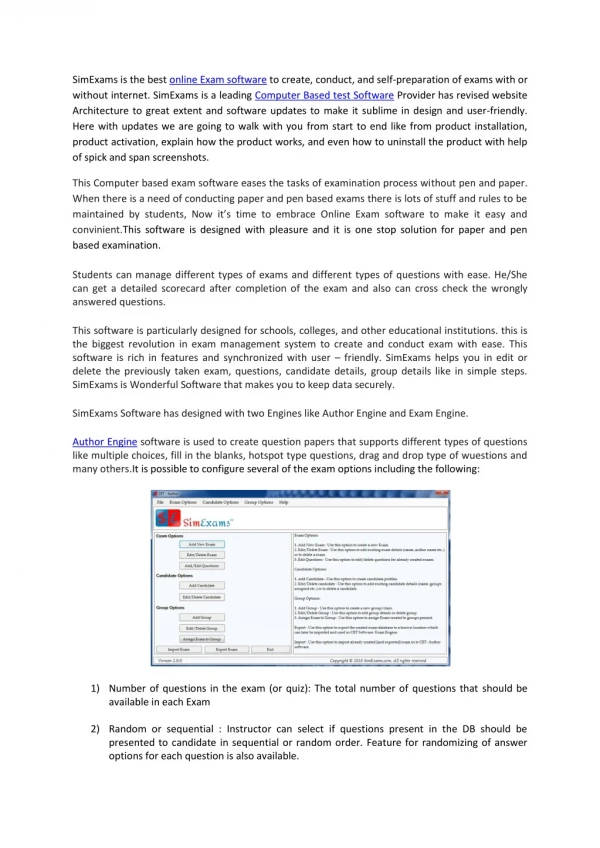

Framework XML µGP asm giovanni.squillero@polito.it

Language Specification • Integer instructions • Legacy x87 • Single-instruction/multiple-data (SIMD) • MMX, SSE, SSE2, SSE3, SSSE3, SSE4, … • Threads • L1 cache hit/miss XML giovanni.squillero@polito.it

Feedback optimization evaluation • Main loop: • Execute the program in safe condition and record signature • Increase frequency and/or decrease core voltage and execute the program until a different signature is detected Record critical status Candidate test Frequency/Voltage Results slave master giovanni.squillero@polito.it

Experimental evaluation • Possible comparison: • State of the art Stability Tests from the overclockers community IEEE Computer, 2004 giovanni.squillero@polito.it

Target system • Intel Pentium Dual-Core E2180 • 2007 • Dual core (2 threads) • SSE 3 • Water cooling giovanni.squillero@polito.it

Target system • Intel Core i7-950 • 2009 • Quad core (8 threads) • Simultaneous multithreading • SSE 4.2 • Water cooling giovanni.squillero@polito.it

Undervolting (@2.93 GHz) giovanni.squillero@polito.it

Undervolting (@3.82 GHz) giovanni.squillero@polito.it

Overclocking (@1.2500 V) giovanni.squillero@polito.it

Overclocking (@1.24375 V) giovanni.squillero@polito.it

HUMIES CLAIM (D) • The result is publishable in its own right as a new scientific result independent of the fact that the result was mechanically created giovanni.squillero@polito.it

HUMIES CLAIM (E) • The result is equal to or better than the most recent human-created solution to a long-standing problem for which there has been a succession of increasingly better human-created solutions giovanni.squillero@polito.it

HUMIES CLAIM (G) • The result solves a problem of indisputable difficulty in its field giovanni.squillero@polito.it

Giovanni Squillero Politecnico di Torino Dipartimento di Automatica e Informatica Corso Duca degli Abruzzi, 24 I-10129 Torino ITALY Tel: +39-011564.7186 Fax: +39-011564.7099 http://www.cad.polito.it/staff/squillero/ giovanni.squillero@polito.it giovanni.squillero@polito.it