MTJ Design Space

MTJ Design Space. Review of Papers Amr’s Slides. Published STT-MRAM Designs.

MTJ Design Space

E N D

Presentation Transcript

MTJ Design Space Review of Papers Amr’s Slides

Published STT-MRAM Designs • M. Hosomi, et al., "A novel nonvolatile memory with spin torque transfer magnetization switching: spin-ram," Electron Devices Meeting, 2005. IEDM Technical Digest. IEEE International , vol., no., pp.459-462, 5-5 Dec. 2005 • T. Kawahara, et al., "2 Mb SPRAM (SPin-Transfer Torque RAM) With Bit-by-Bit Bi-Directional Current Write and Parallelizing-Direction Current Read," Solid-State Circuits, IEEE Journal of , vol.43, no.1, pp.109-120, Jan. 2008 • C.J. Lin, et al., "45nm low power CMOS logic compatible embedded STT MRAM utilizing a reverse-connection 1T/1MTJ cell," Electron Devices Meeting (IEDM), 2009 IEEE International , vol., no., pp.1-4, 7-9 Dec. 2009 • R. Nebashi, et al., "A 90nm 12ns 32Mb 2T1MTJ MRAM," Solid-State Circuits Conference - Digest of Technical Papers, 2009. ISSCC 2009. IEEE International , vol., no., pp.462-463,463a, 8-12 Feb. 2009 • D. Halupka, et al., "Negative-resistance read and write schemes for STT-MRAM in 0.13µm CMOS," Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2010 IEEE International , vol., no., pp.256-257, 7-11 Feb. 2010 • K. Tsuchida, et al., "A 64Mb MRAM with clamped-reference and adequate-reference schemes," Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2010 IEEE International , vol., no., pp.258-259, 7-11 Feb. 2010

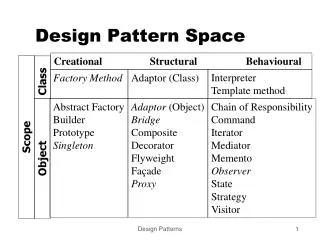

Design Comparisons [2] * Based on simulation results

Design Space Exploration Papers • Found two papers on MTJ design space (both almost completely ignore CMOS side): • Kangho Lee; Kang, S.H., “Design Consideration of Magnetic Tunnel Junctions for Reliable High-Temperature Operation of STT-MRAM,” Magnetics, IEEE Transactions on , vol. 46, no. 6, pp.1537-1540, June 2010 • Qualcomm • Tai Min, et al., , "A Study of Write Margin of Spin Torque Transfer Magnetic Random Access Memory Technology," Magnetics, IEEE Transactions on , vol. 46, no. 6, pp.2322-2327, June 2010 • MaglC-IBM MRAM Alliance

Qualcomm • More of an exploration of MTJ operation at High Temp.

MaglC-IBM MRAM Alliance • Metric of choice BER • Focuses on reducing Write Current for a given BER

Amr’s Slides: Feasibility Region Typical MOS Variations MOS & MTJ Variations Max values for a specific Write Current • IBM 90nm CMOS • VWL = VDD = 1 V • IWR = 500 μA • Wa = 2.56 μm • WP,MUX = 16 μm • WN,MUX = 8 μm • MOS K varies +/- 20% • MOS VT varies +/- 50mV • MTJ: RA = 2 Ω.μm2 • MTJ: KRA = 34 Ω.μm2/nm • MTJ: TMR = 100% • MTJ: KTMR = 200 %/nm • MTJ: ΔtMgO = 0.2 Ao • Current Sensing: VR= 600 mV • Current Sensing: ΔIR= 20 μA Min requirements for specific Read Scheme