Current Project: Microfluidics

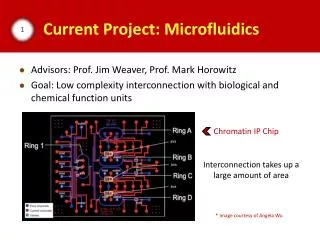

Current Project: Microfluidics. Advisors: Prof. Jim Weaver, Prof. Mark Horowitz Goal: Low complexity interconnection with biological and chemical function units. Chromatin IP Chip. Interconnection takes up a large amount of area. * Image courtesy of Angela Wu.

Current Project: Microfluidics

E N D

Presentation Transcript

Current Project: Microfluidics • Advisors: Prof. Jim Weaver, Prof. Mark Horowitz • Goal: Low complexity interconnection with biological and chemical function units Chromatin IP Chip Interconnection takes up a large amount of area * Image courtesy of Angela Wu

Goal: Low Complexity Interconnection • Advisors: Prof. Jim Weaver, Prof. Mark Horowitz • Goal: Low complexity interconnection with biological and chemical function units Introduce digital elements to control the valves on chip Fluidic latch Bio/Chem units

Goal: Low Complexity Interconnection • What makes state elements work? • They hold states as 0 or 1 (Plow or Phigh) • 0/1 States as control signals for valves • Valves are widely used • Pinch valves, peristaltic pumps, serial-in parallel out registers… EX: Peristaltic pump 1 0 1 1 0 0 1 1 0 0 1 0 0 1 1 0 0 1 1 0 1 Analyte A Analyte B

Continued: IP Chip • Goal Reduce interconnection complexity & integrate with biological/chemical analysis units • Method Gain valves digital state elements allow sharing of control signals by different load signals

IP Chip: Complexity optimization • Problem: how many data lines and control lines for minimum total lines to manage N states individually? • Convert to a math problem: N states, m data lines, n control lines (load & load_b pairs) Choice of (m,n) for minimum total number of lines? Equality holds when that gives minimum total number of lines (m+n)

IP Chip: Complexity optimization • Convert to a math problem: N states, m data lines, n control lines (load & load_b pairs) Choice of (m,n) for minimum total number of lines? • In IP layout, N=18 gives minimum total number of 12 lines 6 data lines, 6 control lines, 6/2=3 load/load_b groups Equality holds when for minimum (m+n)

IP Chip: Layout blocks Ver. 1 D0 D1 D2 D3 D4 D5 L L L L L L L L Load_0 Load_b_0 L L Load_1 Load_b_1 L L Load_2 Load_b_2 L L L L L L

IP Chip: Layout blocks Ver. 2 D0 D1 D2 D3 D4 D5 L L L L L L Load_0 Load_b_0 L L L L Load_1 Load_b_1 L L L L L L L L Load_2 Load_b_2

IP Chip: Layout blocks comparison • Ver. 1 beats Ver. 2 for: • simpler routing • less extra space for data lines between middle and side latches • better control scheme – side vertical 3 latches are loaded simultaneously L L L L L L L L L L L L L L L L L Ver. 1 Ver. 2 L L L L L L L L L L L L L L L L L L L

Summer Goals • G-valve Testing • Breakthrough or dead-end? • Building IP chip • From layout to fabrication • Fabrication skills • Practice makes perfect