期末复习

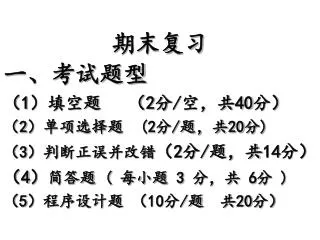

期末复习. 一、考试题型 ( 1 )填空题 ( 2 分 / 空,共 40 分) ( 2 )单项选择题 (2 分 / 题,共 20 分 ) ( 3 )判断正误并改错 ( 2 分 / 题,共 14 分) ( 4 ) 简答题 ( 每小题 3 分,共 6 分 ) ( 5 )程序设计题 ( 10 分 / 题 共 20 分). 什么是 16 位字长的 CPU 呢?. 运算器一次最多可处理 16 位的数据 寄存器的最大宽度是 16 位 寄存器与运算器之间的通路(内部总线)为 16 位. 20 位地址总线. CPU. 16 位数据总线. 主存.

期末复习

E N D

Presentation Transcript

期末复习 一、考试题型 (1)填空题 (2分/空,共40分) (2)单项选择题 (2分/题,共20分) (3)判断正误并改错(2分/题,共14分) (4)简答题 ( 每小题 3 分,共 6分 ) (5)程序设计题 (10分/题 共20分)

什么是16位字长的CPU呢? • 运算器一次最多可处理16位的数据 • 寄存器的最大宽度是16位 • 寄存器与运算器之间的通路(内部总线)为16位

20位地址总线 CPU 16位数据总线 主存 控制总线 8086CPU与主存的三总线连接示意

8086微处理器及其系统一、8086的功能结构 • 总线接口单元 • 指令队列、指令指针(IP)、段寄存器(CS/DS/SS/ES)、地址加法器和总线控制逻辑 • 管理与系统总线的接口,负责对存储器和外设访问 • 执行单元 • ALU、通用寄存器、标志寄存器和控制电路 • 负责指令译码、数据运算和指令执行 • 指令预取 • EU单元译码执行指令,同时BIU单元读取后续指令 • 最简单的指令流水线技术

OF DF IF TF SF ZF AF PF CF 全 零 标 志 单 步 标 志 符 号 标 志 辅 助 进 位 溢 出 标 志 方 向 标 志 中 断 标 志 奇 偶 校 验 进 位 标 志 IF=1 允许中断 IF=0 关闭中断 DF=1 地址指针自动减量DF=0 地址指针自动增量 PF=1 偶校验 PF=0 奇校验 • 状态标志寄存器FLAGS

例1:执行两个数的加法,分析对标志位的影响。例1:执行两个数的加法,分析对标志位的影响。 标志: 运算结果最高位为0 ∴SF=0; 运算结果本身≠0 ∴ZF=0 低8位中1的个数为奇数个 ∴PF=0; 最高位没有进位 ∴CF=0 第三位向第四位无进位 ∴AF=0; 次高位向最高位没有进位 ,最高位向前没有进位 ∴OF=0。

物理地址 8086CPU的地址线是20位的,这样最大可寻址空间应为220=1MB,其物理地址范围从00000H~FFFFFH。 而8086CPU寄存器都是16位的。可以处理的地址为0000H ~FFFFH 那么,这1MB空间如何用16位寄存器表达呢?

学校 体育馆 图书馆 0m 2000m 2826m 物理地址=2826m 逻辑地址=2000:826m 采用分段管理的方法解决 相关的段地址和偏移地址合起来称为逻辑地址。 逻辑地址=段基址:偏移地址 例:

1MB空间的址址编码情况 00000H、00001H、00002H、00003H、…、0000FH 00010H、00011H、00012H、00013H、…、0001FH 00020H、00021H、00022H、00023H、…、0002FH 00030H、 … FFFF0H、FFFF1H、FFFF2H、 … 、 …、 FFFFFH,由于每小节的起始低4位都是0,因此可以不表示出来,而高16位就可以完全放入段寄存器了。

把1M字节地址空间划成若干逻辑段。每个逻辑段必须满足两个条件:一是逻辑段的起始地址(简称段首址)必须是16的倍数;二是逻辑段的最大长度为64K。把1M字节地址空间划成若干逻辑段。每个逻辑段必须满足两个条件:一是逻辑段的起始地址(简称段首址)必须是16的倍数;二是逻辑段的最大长度为64K。 逻辑段与逻辑段可以相连,也可以不连,还可以重叠。 逻辑地址=段基址:偏移地址 物理地址=2826H 逻辑地址=2000H:826H

结论: • 存储器采用分段管理后,一个内存单元可用段的起始地址和段内地址(又称偏移地址)两个逻辑地址来描述,表示为段基址:偏移地址。 • 存储器采用分段管理后,其物理地址的计算方法为: 物理地址= 10H ×段基址 + 偏移地址 = 16 ×段基址 + 偏移地址 所以简便的方法是在段基址的最低位补以0H,再加上偏移量。 例: 逻辑地址=200H:826H 物理地址=2826H

4个16位的段寄存器分别称为: CS(Code Segment):代码段寄存器 DS (Data Segment):数据段寄存器 SS (Stack Segment):堆栈段寄存器 ES (Extra Segment):附加数据段寄存器

00000H 10550H CS=1055H 代码段 <=64KB IP 150A0H DS=150AH 数据段 <=64KB SI,DI,BX EFF00H SS=EFF0H 堆栈段 <=64KB SP,BP FFFFFH ① 段大小最大64KB ②每个段内的偏移地址是0000─FFFFH 物理地址=段基地址+段内地址

寻址方式 1. 立即数寻址 MOV AX,080AH 2. 寄存器寻址 MOV AX,BX 3. 直接寻址 MOV AX,[22A0H] 4. 寄存器间接寻址 MOV AX,[SI] MOV AX,[BP] 5.寄存器相对寻址 MOV AX,20H[BP] MOV AX,[SI+20H]

6. 基址变址寻址 MOV AX,[BX+SI] MOV AX,[BX][SI] 7.相对基址变址寻址 MOV AX,[BX+SI+250H] 8. I/O端口寻址 IN AL,21H MOV DX,3421H OUT DX,AL

填空题: 1.8086/8088CPU从基本构成上可分为、和 三部分;从功能结构上可分为和两部分。 2.若CS=A200H,指出当前代码段可寻址的最大存储空间是从物理地址H到H。 • 微处理器8086地址总线为 位,可直接寻址空间为 字节。 • 段的定义以“段名 ”表示开始,以“段名 ”表示结束。 答案:1.运算器;寄存器;控制器;EU;BIU 2.A2000H,B1FFFH 3. 20,1M 4. SEGMENT, ENDS

选择题: 1.物理地址的计算方法是()。 A.段地址+偏移地址 B. 段地址逻辑左移4位+偏移地址 C.段地址╳16H+偏移地址 D. 段地址╳16+偏移地址 2. 确定下一条指令的物理地址的表达式是( )。 A.CS╳16+IP B. DS╳16+SI C.SS╳16+SP 答案:1. B,D 2. A

数据段:在存储器中开辟的数据区,供存放初始数据,大小由DB,DW伪指令设定。数据定义伪指令用来定义程序中使用的数据在存储单元中位置。格式:[变量名] 助记符 操作数功能:为变量分配单元,并为其初始化或者只预留空间。

01 02 03 04 47 56 45 44 43 01 02 01 01 例:DATA1 SEGMENT TABLE DW 0101H,0102HCHAR DB‘CDEFG’CC DD 01020304HDATA1 ENDS 小结:DB定义字节,DW定义字(2个字节),DD定义双字(这4个字节) CC CHAR TABLE 注意:在数据段中使用的标号TABLE、CHAR、CC后面没有“:”,它们是同时描述内存地址和单元长度的标号。

堆栈的工作原理 FFFF:FFFF 堆栈是一种用来存储数据的逻辑数据结构,它按照先进后出的方式工作。在8086系统中,堆栈是用内存中的某一段连续的地址空间实现的。 在8086系统中,堆栈是在内存中倒挂生长的。 0:0

思考: 若SS的内容为2000H,SP=0140H,如果在堆栈中存入5个数据,SS和SP的内容各是多少? 如果从堆栈中取出2个数据,SS和SP的内容又是多少? SS=2000H SP=0136H SS=2000H SP=013AH

代码段(Code Segment) • 代码段用来存放程序的指令序列 • 代码段寄存器CS存放代码段的段地址 • 指令指针寄存器IP指示下条指令的偏移地址 • 处理器利用CS:IP取得下一条要执行的指令 • 标号和名字都是一个符号,标号后面有冒号(:),而名字后面无冒号。

[例]先查看内存2000:1000内容,然后执行如下程序后(-G=0 10),AX,BX,CX中的内容是什么?

程序运行结果:AX=00BE BX=1000 CX=0606

例如 0~9的编码为: 高3位 低4位 字符 011 00000 011 00011 011 00102 011 00113 011 01004 011 01015 011 01106 011 01117 011 10008 011 10019

每一个字符有一个编码。 常用字符有128个,编码从0到127。 空格 20H 32 ‘0’~‘9’ 30H~39H 48~57 ‘A’~‘Z’ 41H~5AH 65~90 ‘a’~‘z’ 61H~7AH 97~122 控制字符:0~32,127;普通字符:94个。 每个字符占一个字节,用7位,最高位为0。

将datasg段中每个单词的头一个字母改写为大写字母。将datasg段中每个单词的头一个字母改写为大写字母。 assume cs:codesg, ds:datasg datasg segment db '1. file ' db '2. edit ' db '3. search ' db '4. view ' db '5. options ' db '6. help ' datasg ends

codesg segment start: mov ax, datasg mov ds, ax mov bx, 0 ;mov bx,offset datasg mov cx, 6 ss1: mov al, [bx+3] and al, 11011111b ; sub al,20h mov [bx+3], al add bx, 16 loop ss1 mov ax, 4c00h int 21h codesg ends end start

[例]数据段中有某字符串首址为BLOCK。如果其中出现字符‘u’, 将它的偏移地址推进栈中。试在下面程序段的空白处填上适当的指令或操作数以实现上述功能。 DATA SEGMENT BLOCK DB ‘Let ┉ $’ DATA ENDS STA SEGMENT STACK DW 50 DUP(?) STA ENDS CODE SEGMENT ASSUME CS:CODE, DS:DATA, SS:STA

START:MOV AX, DATA MOV DS, AX MOV SI, offset BLOCK A1: MOV AL,[SI] CMP AL,’$’ JZ JIESU CMP AL, ‘u’ JNZ A2 PUSH SI A2: INC SI JMP A1

JIESU: MOV AX,4C00H INT 21H CODE ENDS END START

两种工作模式: 最小方式(MN/MX=1): 适用于单处理机系统,即系统中只有一个8086/8088,所有总线控制信号都由其产生。 最大方式(MN/MX=0): 系统包含多个处理机,其中8086/8088为主处理机,还有协处理器8087、8089等。通常由专门的总线控制器(8288)产生总线控制信号。

最小模式的系统组成: 最小模式的典型配置

填空题: 在8086最大方式中, 8282(74LS373,74LS244)的作用是;8286(74LS245)的作用是;8288的作用是;8284的作用是 。 答案: 将分时复用信号线AD19~0上的地址信息锁存起来,形成20位地址总线; 增强数据总线的驱动能力; 对CPU的状态信息译码,形成系统控制总线 给CPU提供同步后的RESET、READY、CLK信号;

总线周期时序: • 定义:利用总线完成一个字长信息的传输时间;1个指令周期包含1个或多个总线周期。 • 1个总线周期正常情况下由4个时钟周期(T1―T4)组成;时钟周期由主频决定; • 空闲周期TI和等待周期TW; • 读、写、中断响应、总线保持与响应等的总线周期时序

总线操作的概念: 典型的总线周期

8086与存储器连接 D7-D0低8位数据总线 D15-D8高8位数据总线 00000H 00001H D8-D15 D7-D0 512k X 8位奇存储体 512k X 8位偶存储体 A19-A1 A19-A1 FFFFEH CS CS FFFFFH A19-A1 地址总线 BHE A0 A0=0访问偶地址存储体,A0=1表示访问奇地址存储体

硬件: 系统总线 +接口电路 +输入/出设备 (I/O设备、外设) I/O接口的基本概念: 将I/O设备与系统总线连接的部件 系统 总线 DMAC 中断控制电路 输入/出方式 USB 并行接口 RS-232串口

数 据 输 出 +5V U Y Y Y Y Y Y Y 5 6 0 1 2 3 4 cc 管 脚 图 74LS138 13 1 4 7 8 16 10 9 14 5 2 6 3 12 15 11 A C B G GND Y G G 7 2 B 2 A 1 输出 地 输入选择 允许(使能) 组件:3-8线译码器

译码器应用举例 • 每个输出端连接一盏灯,控制亮、灭 C B A 输出端 结果 0 0 0 Y0=0 选Y0 0 0 1 Y1=0 选Y1 … 1 1 1 Y7=0 选Y7 通过程序控制C、B、A 以便选择输出端Y0~Y7

与存储器地址译码在原理和方法上完全相同 • I/O地址不太强调连续,多采用部分译码

微机的输入输出方式有哪几种?各有什么特点?微机的输入输出方式有哪几种?各有什么特点? (1)无条件:需要外设处于就绪状态,硬件简单; (2)查询:CPU需要不断地查询外设是否就绪,浪费CPU时间,硬件较简单; (3)中断:外设准备好后,向CPU发中断请求,请求CPU完成数据传输,外设与CPU并行;硬件又比前两者复杂。 (4)DMA:CPU对DMAC初始化后,由DMAC控制总线完成数据传送;CPU与I/O并行。速度快,用于大量数据传输。DMAC占用总线时,CPU不能用。硬件更复杂。

(1)无条件传送输出:锁存器 • 使用D触发器构成 • 输入端为D端,控制端为C端 • 两个相反的输出信号Q和Q • 直接复位R或直接置位S控制端 • 电平锁存:电平控制输出能跟随输入变化 • 边沿锁存:输出只能锁存输入的状态 • 74LS373:电平锁存的8位三态缓冲锁存器 • 74LS374:边沿锁存的8位三态缓冲锁存器

D7 D6 : D0 微处 理器 …… 地 址 译 码 74LS373 OE G Q7 Q6 Q5 Q4 Q3 Q2 Q1 Q0 驱动器 无条件传送方式——简单快捷的外部设备

无条件传送输入:三态缓冲器 • 三态缓冲器:加有控制端的同相器或反相器 • 控制端T有效时,控制输入A端输出到Y端 • 控制端T无效时,输出Y端呈现高阻状态 • 74LS244:双4位三态同相缓冲器 • 双向三态缓冲器:两个三态缓冲器构成 • 输出允许控制端OE:控制数据的输出 • 方向控制端DIR:控制数据驱动的方向 • 74LS245:8位双向三态缓冲器芯片

+5V D0 D1 D7 1Y1 1A1 1Y2 1A2 74LS244 2Y4 2A4 1G 2G 74LS244构成简单输入端口: M/IO CS RD 开关

(2)程序查询方式 • 查询传送有查询和传送两个环节 • 首先查询外设工作状态 • 检测、等待外设准备就绪 • 进行数据传输 • 设计实现查询功能的电路 • 连接外设的状态输入信号 • 保存在状态寄存器中 • 通过状态端口读取 • 实际中常引入超时判断 • 查询需大量时间,效率较低