第五章 数字信号处理系统的实现

第五章 数字信号处理系统的实现. 数字滤波器的实现方法: a. 利用专用计算机; b. 直接利用计算机和通用软件编程实现。 一个数字滤波器的系统函数一般可表示为有理函数形式: 为 I I R 滤波器形式, { } 都为 0 时就是一个 FIR 滤波器。 对于这样一个系统,也可用差分方程来表示:. DF. IIR 、 FIR 的系统函数 网络结构形式 软、硬件实现.

第五章 数字信号处理系统的实现

E N D

Presentation Transcript

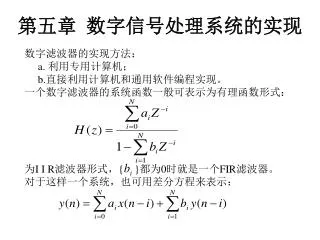

第五章 数字信号处理系统的实现 数字滤波器的实现方法: a.利用专用计算机; b.直接利用计算机和通用软件编程实现。 一个数字滤波器的系统函数一般可表示为有理函数形式: 为I I R滤波器形式,{ }都为0时就是一个FIR滤波器。 对于这样一个系统,也可用差分方程来表示:

DF IIR、FIR的系统函数 网络结构形式 软、硬件实现

即一个输出序列是其过去 点的线性组合加上当前输入序列与过去 点输入序列的线性组合。 除了与当前的输入 有关,同时还与过去的输入和过去的输出有关,系统是带有记忆的。 对于上面的算式,可以化成不同的计算形式,如直接计算、分解为多个有理函数相加、分解为多个有理函数相乘等等,不同的计算形式也就表现出不同的计算结构,而不同的计算结构可能会带来不同的效果,或者是实现简单,编程方便,或者是计算精度较高等等。 另外,数字信号是通过采样和转换得到的,而转换的位数是有限的(一般6、8、10、12、16位),所以存在量化误差,另外,计算机中的数的表示也总是有限的,经此表示的滤波器的系数同样存在量化误差,在计算过程中因有限字长也会造成误差。

量化误差主要有三种误差: ①A/D变换量化效应; ②系数的量化效应; ③数字运算的有限字长效应。

5.1 数字滤波器的结构 一、数字网络的信号流图表示 差分方程中数字滤波器的基本操作:①加法,②乘法,③延迟。 为了表示简单,通常用信号流图来表示其运算结构。对于加法、乘法及延迟这三种基本运算。

只有输出支路的节点称为输入节点或源点; 只有输入支路的节点称为输出节点或阱点; 既有输入支路又有输出支路的节点叫做混合节点。 通路是指从源点到阱点之间沿着箭头方向的连续的一串支路,通路的增益是该通路上各支路增益的乘积。 回路是指从一个节点出发沿着支路箭头方向到达同一个节点的闭合通路,它象征着系统中的反馈回路。组成回路的所有支路增益的乘积通常叫做回路增益。

梅逊(Mason)公式 式中Tk为从输入节点(源点)到输出节点(阱点)的第k条前向通路增益; Δ为流图的特征式 为所有不同回路增益之和. 为每两个互不接触回路增益之和 Δk是不接触第k条前向通路的特征式余因子

例:利用梅逊公式计算图中的系统函数 有两条前向通路: 一个回路,其回路增益为 则系统函数

信号流图的转置定理: 对于单个输入、单个输出的系统,通过反转网络中的全部支路的方向,并且将其输入和输出互换,得出的流图具有与原始流图相同的系统函数。

信号流图转置的作用: ①转变运算结构; ②验证计算流图的系统函数的正确与否。 运算结构对滤波器的实现很重要,尤其对于一些定点运算的处理机,结构的不同将会影响系统的精度、误差、稳定性、经济性以及运算速度等许多重要的性能。对于无限长单位冲激响应(I I R)数字滤波器与FIR数字滤波器,它们在结构上各有自己不同的特点,因此我们在下面将对它们分别加以讨论。

二、IIR数字滤波器的结构 IIR数字滤波器的结构特点:存在反馈环路,递归型结构。 同一系统函数,有各种不同的结构形式。其主要结构有: (1) 直接型 直接由 IIR DF 的差分方程所得的网络结构。

上述结构缺点: ①需要2N个延迟器(z-1),太多。 ②系数ai、bi对滤波器性能的控制不直接,对极、零点的控制难,一个ai、bi的改变会影响系统的零点或极点分布。 ③对字长变化敏感(对ai、bi的准确度要求严格)。 ④易不稳定,阶数高时,上述影响更大。

(2)直接Ⅱ型 上面直接型结构中的两部分可分别看作是两个独立的网络(H1(z)和H2(z)),两部分串接构成总的系统函数: 由系统函数的不变性(系统是线性的),得

直接II型优缺点: 优点:延迟线减少一半,为N个,可节省寄存器或存储单元。 缺点:同直接型。 通常在实际中很少采用上述两种结构实现高阶系统,而是把高阶变成一系列不同组合的低阶系统(一、二阶)来实现。

(3)级联型(串联) 一个 N 阶系统函数可用它的零、极点表示,即把它的分子、分母都表达为因子形式 由于系数 、 都是实数,极、零点为实根或共轭复根,所以有

、 ——实根 、 ——复根 且 将共轭因子合并为实系数二阶因子,单实根因子看作二阶因子的一个特例,则 、 ——为实系数。 用若干二阶网络级联构成滤波器,二阶子网络称为二阶节,可用正准型结构实现。

级联型结构的优缺点: 优点: ①简化实现,用一个二阶节,通过变换系数就可实现整个系统; ②极、零点可单独控制、调整,调整 、 可单独调整第 对零点,调整 、 可单独调整第 对极点; ③各二阶节零、极点的搭配可互换位置,优化组合以减小运算误差; ④可流水线操作。 缺点: 二阶节电平难控制,电平大易导致溢出,电平小则使信噪比减小。

(4)并联型 将系统函数展开成部分分式之和,可用并联方式构成滤波器: 将上式中的共轭复根成对地合并为二阶实系数的部分分式, 上式表明,可用L个一阶网络、M个二阶网络以及一个常数 并联组成滤波器 H(z),结构如下图:

特点: ①系统实现简单,只需一个二阶节,系统通过改变输入系数即可完成; ②极点位置可单独调整; ③运算速度快(可并行进行); ④各二阶网络的误差互不影响,总的误差小,对字长要求低。 缺点: 不能直接调整零点,因多个二阶节的零点并不是整个系统函数的零点,当需要准确的传输零点时,级联型最合适。

FIR DF 特点: 主要是非递归结构,无反馈,但在频率采样结构等某些结构中也包含有反馈的递归部分。 它的系统函数和差分方程一般有如下形式: 三、FIR DF网络结构形式

基本的结构形式有下几种: (1)直接型(卷积型、横截型) 卷积型:差分方程是信号的卷积形式; 横截型:差分方程是一条输入x(n)延时链的横向结构。

直接型的转置: 图

(2)级联型(串联型) 当需要控制滤波器的传输零点时,可将系统函数分解 为二阶实系数因子的形式: 于是可用二阶节级联构成, 每一个二阶节控制一对零点。 缺点: ①所需要的系数a比直接型的h(n)多; ②乘法运算多于直接型。

(3)线性相位型 FIR的重要特点是可设计成具有严格线性相位的滤波器,此时 满足偶对称或奇对称条件。 偶对称时, N为偶数, N为奇数,

由上两式,可得到线性相位FIR滤波器的结构,如图。由上两式,可得到线性相位FIR滤波器的结构,如图。 优点: 线相相位型结构的乘法次数减为 (N偶数) (N奇数) (横截型结构乘法次数:N次)

(4)频率采样型 第二章讨论了有限长序列可以进行频域采样。 现 是长为 的序列,因此也可对系统函数H(z)在单位圆上作 等分采样,这个采样值也就是 的离散付里叶变换值H(k)。 根据上一章的讨论,用频率采样表达z函数的内插公式为:

H(z)由两部分级联而成, 第一部分( 部分) 这是一个由 节延时器组成的梳状滤波器,它在单位圆上有 个等分的零点: 其频响为

第二部分(IIR部分)是一组并联的一阶网络: 此一阶网络在单位圆上有一个极点: 该网络在 处的频响为 ,是一个谐振频率为 的谐振器。这些并联谐振器的极点正好各自抵消一个梳状滤波器的零点,从而使这个频率点的响应等于 。 两部分级联后,就得到频率采样型的总结构,

这一结构的最大特点是它的系数H(k)直接就是滤波器在 处的响应,因此,控制滤波器的响应很直接。 两个主要的缺点: ①所有的系数 和 都是复数,计算复杂。 ②所有谐振器的极点都在单位圆上,考虑到系数量化的影响,有些极点实际上不能与梳状滤波器的零点相抵消,使系统的稳定性变差。

为了克服这两个缺点,作两点修正: 1)将所有零点和极点移到半径为 的圆上, 略小于 1,同时频率采样点也移到该圆上,以解决系统的稳定性。这时

2)共轭根合并,将一对复数一阶子网络合并成一个实系数的二阶子网络。这些共轭根在圆周上是对称点即2)共轭根合并,将一对复数一阶子网络合并成一个实系数的二阶子网络。这些共轭根在圆周上是对称点即 同样,h(m)因是实数,其 DFT 也是圆周共轭对称的,

因此可将第k及第N-k个谐振器合并为一个二阶网络因此可将第k及第N-k个谐振器合并为一个二阶网络 其中

这个二端网络是一个有限Q值的谐振器,谐振频率为 。 除了以上共轭极点外,还有实数极点,分两种情况: 当N为偶数时,有二个实数极点 ,对应H(0)和H(N/2),有二个一阶网络: 所以有

当 为奇数时,只有一个实数极点 ,对应H(0),有一个一阶网络: 所以有

频率采样型特点: 1.选频性好,适于窄带滤波,大部分H(k)为0,只有较少的二阶子网络; 2.不同的FIR滤波器,若长度相同,可通过改变系数用同一个网络实现; 3. 复用性好。 缺点:结构复杂,采用的存贮器多。