University of Portland School of Engineering: Digital Lock Project Overview

120 likes | 143 Views

Engaging overview of the digital lock project featuring a detailed scorecard, accomplishments, future plans, and identified issues. Follows the journey from introduction to successful completion. Delivered in partnership with the Owyhee Digital Lock Team.

University of Portland School of Engineering: Digital Lock Project Overview

E N D

Presentation Transcript

Project OwyheeDigital Lock Team Jessica Rice Julie Barton-Smith Cory Johnson • Advisor • Dr. Inan, Dr. Osterberg • Industry Representative • Mr. Wes Mickanin University of Portland School of Engineering

Overview • Introduction • Scorecard • Additional Accomplishments • Plans • Issues/Concerns University of Portland School of Engineering

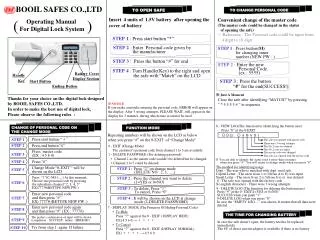

Introduction • Digital lock • On MOSIS chip • Keypad entry with key override • Block Diagram University of Portland School of Engineering

Introduction ctd. University of Portland School of Engineering

Scorecard • Establish Testing Protocol • Series of 6 tests • Right and Wrong Codes • Door Open • 2 Wrongs Make a Right • Test Logic & Debug Logic Design • Ran Command File • It Worked! University of Portland School of Engineering

Scorecard ctd. • Begin Design of Macro-model • Discussed Using CPLD’s • Use 6 Functional Blocks • Update Website • Formalize Project Plan • Change Request Approved University of Portland School of Engineering

Additional Accomplishments • Acquired electric latch and door knob • Sent in chip 2 days early • Teleconferenced with Dr. Osterberg University of Portland School of Engineering

Plans • Finish designing macro-model • Design Approval Meeting • Order Parts University of Portland School of Engineering

Milestones University of Portland School of Engineering

Concerns/Issues • Hardware Interface with MOSIS Chip • Re-Learning ABEL • Not Being in Same State Over Break University of Portland School of Engineering

Conclusions • Introduction • On Chip Digital Lock • Scorecard • All finished except Macro-model Design • Additional Accomplishments • Sent Out Chip Early • Plans • Macro-model • Issues/Concerns • Interfacing with chip University of Portland School of Engineering

Questions? University of Portland School of Engineering

![Multi-controlled Digital Door lock [Anykey]](https://cdn3.slideserve.com/5744120/multi-controlled-digital-door-lock-anykey-dt.jpg)