概 述

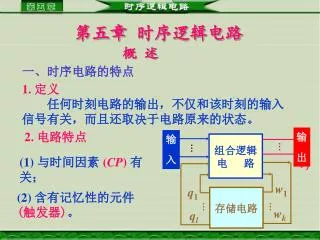

x 1. y 1. 组合逻辑 电 路. …. …. …. …. x i. y j. w 1. q 1. 存储电路. …. …. w k. q l. 第五章 时序逻辑电路. 概 述. 一、时序电路的特点. 1. 定义. 任何时刻电路的输出,不仅和该时刻的输入信号有关,而且还取决于电路原来的状态。. 2. 电路特点. 输 出. 输 入. (1) 与时间因素 ( CP ) 有关;. (2) 含有记忆性的元件 ( 触发器 ) 。. x 1. y 1. 组合逻辑 电 路. …. …. …. …. x i.

概 述

E N D

Presentation Transcript

x1 y1 组合逻辑 电 路 … … … … xi yj w1 q1 存储电路 … … wk ql 第五章 时序逻辑电路 概 述 一、时序电路的特点 1. 定义 任何时刻电路的输出,不仅和该时刻的输入信号有关,而且还取决于电路原来的状态。 2. 电路特点 输 出 输 入 (1) 与时间因素 (CP) 有关; (2) 含有记忆性的元件 (触发器)。

x1 y1 组合逻辑 电 路 … … … … xi yj w1 x1 y1 q1 存储电路 y2 x2 … … wk ql J Q1 1J Q2 C1 K 1K CP 二、时序电路逻辑功能表示方法 1. 逻辑表0达式 (1) 输出方程 (2) 驱动方程 (3) 状态方程 2. 状态表、卡诺图、状态图和时序图

CP Y(tn) 输出 X(tn) 输入 组合 电路 组合 电路 组合 电路 存储 电路 Y(tn) 输出 X(tn) 输入 存储 电路 Q W CP 三、时序逻辑电路分类 计数器、寄存器、读/写存储器、 顺序脉冲发生器等。 1. 按逻辑功能划分: 2. 按时钟控制方式划分: 同步时序电路 触发器共用一个时钟 CP,要更新状态的触发器同时翻转。 异步时序电路 电路中所有触发器没有共用一个 CP。 Mealy型 3. 按输出信号的特性划分: Moore型

5.1 时序电路的基本分析和设计方法 5.1.1 时序电路的基本分析方法 1. 分析步骤 时序电路 特性方程 驱动方程 时钟方程 输出方程 状态方程 CP 触 发 沿 计算 状态图 状态表 时序图

Y & FF0 FF1 FF2 1J 1J 1J C1 C1 C1 1K 1K 1K CP 2. 分析举例 [例 5.1.1] [解] 写方程式 时钟方程 输出方程 (Moore 型) (同步) 特性方程 驱动方程 状态方程

计算,列状态转换表 画状态转换图 /1 /1 /1 /1 /1 111 110 000 001 011 100 0 0 0 1 0 0 1 1 有效状态和有效循环 /0 /1 0 1 1 1 101 010 1 1 1 1 无效状态和无效循环 1 1 0 1 /1 0 1 0 0 能否自启动? 存在无效状态,但没有 形成循环。 能自启动: 1 0 1 0 1 0 1 1 不能自启动: 无效状态形成循环。 0 1 0 1

Q2n+1 Q1n+1 Q0n+1 Q1nQ0n Q1nQ0n Q1nQ0n Q2n 00 01 11 10 00 01 11 10 00 01 11 10 Q2n Q2n 0 0 1 1 0 1 1 0 1 1 1 1 0 0 0 0 0 1 1 0 1 1 0 0 0 0 0 1 1 1 Q1nQ0n Q2n 00 01 11 10 0 1 方法2利用卡诺图求状态图 Q2n+1 Q1n+1 Q0n+1 000 001 011 100 110 111 011 001 111 101 010 101 000 110 010 100

/1 /1 /1 /1 /1 111 110 000 001 011 100 /0 1 2 3 4 5 6 CP 画时序图 CP下降沿触发 Q2 0 0 0 0 0 1 0 1 1 1 1 1 1 1 0 1 0 0 0 0 0 Q1 Q0 Y

状态方程 [例 5.1.2] 写方程式 [解] 时钟方程 Mealy型 输出方程 驱动方程

Q0n+1 Q1n+1 Q1nQ0n Q1nQ0n Q2n+1 00 01 11 10 SQ2n Q1nQ0n 00 01 11 10 SQ2n 1 0 0 1 00 01 11 10 00 01 11 10 SQ2n 0 1 0 1 00 01 11 10 0 0 1 0 1 0 0 1 00 01 11 10 0 1 0 1 1 1 0 1 1 0 0 1 0 0 0 1 1 0 0 1 1 0 0 1 0 1 0 1 0 0 1 0 Q1nQ0n Q1nQ0n Q2n Q2n 00 01 11 10 00 01 11 10 0 0 1 1 Q2n+1 Q1n+1 Q0n+1 S = 1 S = 0 001 010 100 011 011 100 010 001 110 101 111 000 101 000 000 111

状态 转换表 状态图 S/Y1Y2 1/10 能自启动 1/11 /00 /00 /00 /00 /00 0/00 0/00 111 000 001 010 011 100 101 110 111 1/00 110 0/01

1/10 /00 /00 /00 /00 /00 0/00 0/00 111 000 001 010 011 100 101 110 111 1/00 110 0/01 画时序图 当 S = 0 时,每 8 个 CP 一个循环; 当 S =1 时,每 6 个 CP 一个循环。

& 1D 1D 1D C1 C1 C1 FF2 FF0 FF1 CP & (Q0 有效) 异步时序电路 [例 5.1.3] [解] 写方程式 时钟方程 驱动方程 (CP 有效) 状态 方程 (CP 有效)

101 000 001 010 110 100 011 111 求状态转换表 CP2CP0 0 0 0 1 0 0 0 1 1 0 1 0 0 0 0 0 0 1 1 0 0 1 1 0 CP2CP1CP0 CP2CP0 CP2CP1CP0 CP2CP0 CP2CP1CP0 能自启动 CP2CP0 CP2CP1CP0

000 001 010 100 011 1 2 3 4 5 CP Q0 画时序图 不画无 效状态 Q0 Q1 Q2

5.1.2 时序电路的基本设计方法 1. 设计的一般步骤 逻辑 抽象 状态 化简 时序逻辑 问题 状态转换 图(表) 最简状态 转换图(表) 选定触发 器的类型 逻辑 电路图 求出 驱动方程 电路方程式 (状态方程) 检查能否 自启动

00 01 11 10 00 01 11 10 0 1 0 1 /0 /0 /0 /0 /0 100 101 000 011 010 001 /1 2. 设计举例 按如下状态图设计时序电路。 [例 5.1.3.4] [解] 已给出最简状态图,若用同步方式: 输出方程 Y 0 0 0 0 为方便,略去右上角 标n。 0 1 状态方程 1 1 0 1 0 0 0 1 0 1 0 1 0

FF0 1J C1 1K & FF1 FF2 1J & & 1J C1 C1 1K 1K CP 选用 JK 触发器 检查能否自启动: 驱动方程 /0 /1 110111000 能自启动 逻辑图 约束项 Y 1 (Moore型)

0/10 1/00 /00 1/00 1/00 /00 /00 1/00 000 011 010 100 101 001 111 110 1/01 Y1 Y2 Q1nQ0n Q1nQ0n 00 01 11 10 00 01 11 10 PQ2n PQ2n 0 0 0 0 0 1 0 0 00 01 11 10 00 01 11 10 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 按如下状态图设计时序电路。 [例 5.1.5] P/Y1Y2 [解] 选用上升沿触发的 D 触发器 时钟方程 输出方程

0/10 1/00 /00 1/00 1/00 /00 /00 1/00 000 011 010 100 101 001 111 110 1/01 Q2n+1Q2n+1 Q0n+1 Q2n+1Q1n+1 Q0n+1 Q2n+1 Q1n+1 Q0n+1 Q2n+1Q0n+1 Q0n+1 Q1nQ0n Q1nQ0n Q1nQ0n Q1nQ0n PQ2n PQ2n PQ2n PQ2n 00 01 11 10 00 01 11 10 00 01 11 10 00 01 11 10 001 001 001 001 010 010 010 010 000 000 000 000 011 011 011 011 00 01 11 10 00 01 11 10 00 01 11 10 00 01 11 10 101 101 101 101 110 110 110 110 000 000 000 000 111 111 111 111 001 001 001 001 010 010 010 010 100 100 100 100 011 011 011 011 状态方程 =D0 =D1 =D2 驱动方程 逻辑图等 (略)

1/0 1/0 S1 S0 S2 1/1 0/0 0/0 0/0 [例 5.1.6] 设计 一个串行数据检测电路,要求输入 3 或 3 个以上数据1时输出为 1,否则为 0。 逻辑抽象,建立原始状态图 [解] S2 — 连续输入 2 个 1 S0 — 原始状态(0) S3 — 连续输入 3 或 3 个以上 1 S1 — 输入1个1 Y — 输出入数据 X — 输入数据 1/0 1/0 1/1 S1 S0 S2 0/0 S3 1/1 0/0 0/0 0/0 0/0 0/0 状态化简

Q1nQ0n X 1/0 1/0 1/0 1/0 00 01 11 10 01 S1 00 S0 11 S2 1/1 1/1 0/0 0/0 0 0/0 0/0 0/0 0/0 1 M = 3,取 n = 2 状态分配、状态编码、状态图 S0= 00 S0= 01 S0= 11 选触发器、写方程式 选 JK ( ) 触发器,同步方式 输出方程 状态方程 Y Q2 Q1 0 0 0 1 0 0 1 1

1 0 1 0 1 0 0 1 & FF1 FF0 & 1J X 1J Q1 Q0 C1 C1 1 1K 1K CP 驱 动 方 程 约束项 无效状态10 逻 辑 图 Y 1/1 0/0 10 11 00 能自启动 (Mealy 型)

5.2 计数器 (Counter) 5.2.1 计数器的特点和分类 一、计数器的功能及应用 对时钟脉冲 CP 计数。 1. 功能: 分频、定时、产生节拍脉冲和脉冲 序列、进行数字运算等。 2. 应用: 二、计数器的特点 Moore 型 计数脉冲 CP 1. 输入信号: 时钟触发器 2. 主要组成单元:

三、 计数器的分类 二进制计数器 十进制计数器 N 进制(任意进制)计数器 按数制分: 加法计数器 减法计数器 可逆计数 (Up-Down Counter) 按计数 方式分: 按时钟 控制分: 同步计数器 (Synchronous ) 异步计数器 (Asynchronous ) 按开关 元件分: TTL 计数器 CMOS 计数器

5.2.2 二进制计数器 计数器计数容量、长度或模的概念 计数器能够记忆输入脉冲的数目,即电路的有效状态数 M 。 000 111 3 位二进制同步加法计数器: /1 4 位二进制同步加法计数器: 1111 0000 /1 n 位二进制同步加法计数器:

来一个CP翻转一次 当Q0=1,CP到来即翻转 当Q1Q0=1,CP到来即翻转 一、二进制同步计数器 FF2、FF1、FF0 Q2、Q1、Q0 (一)3 位二进制同步加法计数器 n 位二进制同步加法计数器级联规律: 设计方法一: 按前述设计步骤进行 (P270 271) 设计方法二: 按计数规律进行级联 — Carry 向高位的进位 C = Q2nQ1nQ0n = T0 J0= K0 = 1 J1= K1 = Q0 = T1 = T2 J2= K2 = Q1Q0

& & FF0 FF1 FF2 C Q0 Q1 Q2 1J 1J 1J 1 C1 C1 C1 1K 1K 1K Q0 CP & Q1 Q1 Q2 Q2 C & FF0 FF1 FF2 Q0 Q1 Q2 1J 1J 1J 1 C1 C1 C1 1K 1K 1K Q0 CP J0= K0 =1 J1= K1 = Q0 J2= K2 = Q1Q0 串行进位 触发器 负载均匀 并行进位 低位触发 器负载重

B = Q2nQ1nQ0n T1=Q0n T2= Q1nQ0n Q2 & & FF0 FF1 FF1 B Q0 Q1 1J 1J 1J Q2 1 C1 C1 C1 1K 1K 1K Q0 Q1 CP (二)3 位二进制同步减法计数器 Borrow 级联规律: —向高位发出的借位信号 若用T 触发器: T0 = 1

& & & 1 U/D C/B 1J 1J 1J 1 Q1 Q0 Q2 C1 C1 C1 1K 1K 1K FF0 FF1 FF2 CP Q0 Q1 Q2 1 1 1 T0 = 1、T1= Q0n、T2= Q1nQ0n (三)二进制同步可逆计数器 单时钟输入二进制同步可逆计数器 加/减 控制端 加计数 T0 =1、T1=Q0n、T2= Q1nQ0n 减计数

FF0 FF1 1 1 Q0 Q1 1J 1J FF2 C1 C1 1 Q2 1K 1K 1J C1 1K Q0 Q1 Q2 1 1 1 & & CP1= CPU ·Q0n+ CPD · Q0n CP2=CPU · Q1nQ0n+ CPD · Q1nQ0n 双时钟输入二进制同步可逆计数器 加计数脉冲 CPU 减计数脉冲 CPD CPU 和CPD 互相排斥 CP0= CPU+ CPD CPU= CP,CPD= 0 CPD= CP,CPU= 0

VCC CO Q0 Q1 Q2 Q3 CTT LD 0 0 0 0 Q0 Q1 Q2 Q3 0 0 1 1 CTP CO 16 15 14 13 12 11 10 9 74161 CTT 74161(3) LD CP 1 2 3 4 5 6 7 8 CR D0D1 D2 D3 CRCP D0D1 D2 D3CTP 地 CR = 0 CR=1,LD=0,CP (四) 集成二进制同步计数器 1. 集成 4 位二进制同步加法计数器 1) 74LS161 和 74LS163 逻辑功能示意图 引脚排列图 0 0 1 1 Q3 Q0 = 0000 异步清零 Q3 Q0 = D3 D0 同步并行置数

CR=1, LD=1, CP, CR=1,LD =1, 74163 74161的状态表 CTP = CTT =1 二进制同步加法计数 CTPCTT = 0 保持 若 CTT = 0 CO = 0 若 CTT = 1

VDD 2CR2Q32Q22Q12Q02EN2CP Q0 Q1 Q2 Q3 16 15 14 13 12 11 10 9 CC4520 CC4520 1 2 3 4 5 6 7 8 1CP1EN1Q01Q11Q1Q31CR VSS EN CP CR 2) CC4520 计数脉 冲输入 也可作 使能端 使能端 也可作 计数脉 冲输入 异 步 清 零

减计数时CO/BO = Q3nQ2nQ1nQ0n VCC D0 CP RCCO/BO LD D2 D3 Q0 Q1 Q2 Q3 16 15 14 13 12 11 10 9 CT=1,CO/BO=1时, RC CT 74191 CO/BO 74191 U/D 1 2 3 4 5 6 7 8 CP LD D0D1 D2 D3 D1Q1Q0 CTU/DQ2 Q3地 2. 集成 4 位二进制同步可逆计数器 加计数时CO/BO = Q3nQ2nQ1nQ0n 并行异 步置数 1) 74191(单时钟)

VCC D0 CR BO CO LD D2 D3 Q0 Q1 Q2 Q3 BO CR 16 15 14 13 12 11 10 9 CPU 74193 CO 74193 CPD LD 1 2 3 4 5 6 7 8 D0D1 D2 D3 D1Q1Q0 CPD CPU Q2 Q3地 2) 74193(双时钟)

CP Q0 Q1 Q2 C CP FF0 FF1 FF2 1J 1J 1J Q0 Q1 Q2 1 1 1 C1 C1 C1 & 1K 1K 1K Q1 Q2 Q0 CP1=Q0 CP2=Q1 二、二进制异步计数器 CP0 = CP (一)二进制异步加法计数器 CP1 = Q0 CP2 = Q1 用T 触发器 (J=K =1) 下降沿触发 C = Q2nQ1nQ0n 并行 进位 CP0= CP 若采用上升沿触发的 T 触发器

& C FF1 FF0 FF2 Q0 Q1 & Q2 1D 1D 1D C FF1 FF0 FF2 Q0 C1 Q1 C1 C1 Q2 1D 1D 1D CP C1 C1 C1 Q0 CP Q1 Q0 Q1 Q2 Q2 D触发器构成的 T触发器 ( D = Q ), ——下降沿触发 若改用上升沿触发的 D 触发器?

FF0 FF2 FF1 1J 1J 1J Q2 Q0 Q1 C1 C1 C1 CP 1K 1K 1K Q2 Q1 Q0 B 1 1 & 1 B=Q2nQ1nQ0n (二)二进制异步减法计数器 用T触发器 (J=K =1)上升沿触发 0 0 0 0 1 2 3 4 5 6 7 8 1 1 1 1 1 0 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 二进制异步计数器级间连接规律 0 0 0 CP0= CP CP1= Q0 CP2= Q1

VCC CR Q3 D3 D1 Q1 CP0 Q0 Q1 Q2 Q3 14 13 12 11 10 9 8 74197 CT/LD CP1 1 2 3 4 5 6 7 74197 CP0 CR CT/LD Q2 D2 D0Q0 CP1 地 D0D1 D2 D3 (三)集成二进制异步计数器 74197、74LS197 计数/置数 异步清零 异步置数 加法计数 二 — 八 — 十六进制计数

Q2 Q3 Q1 FF3 FF1 FF2 1J 1J 1J C1 C1 C1 1K 1K 1K Q3 Q2 Q1 1 1 1 CP0 CP1 Q0 FF0 1J C1 1K Q0 1 二-八-十六进制计数器的实现 M = 2 计数输出: M = 8 计数输出: M = 16 计数输出: 其它:74177、74LS177、74293、74LS293 等。

/0 /0 /0 /0 0000 0001 0010 0011 0100 /0 /1 /0 /0 /0 /0 1001 1000 0111 0110 0101 C Q1nQ0n 00 01 11 10 Q3nQ2n 0 0 0 0 00 01 11 10 0 0 0 0 0 1 (8421BCD 码) 5.2.3 十进制计数器 一、十进制同步计数器 (一)十进制同步加法计数器 状态图 时钟方程 输出方程

Q3n+1 Q2n+1 Q1n+1 Q0n+1 Q1nQ0n Q3nQ2n 00 01 11 10 0001 0010 0011 0100 00 01 11 10 0110 1000 0111 0101 J1= Q3nQ0n, K1= Q0 0000 1001 & Q1 C FF1 Q0 FF0 FF2 FF3 Q2 Q3 & & & 1J 1J 1J 1J 1 C1 C1 C1 C1 1K 1K 1K 1K & Q3 CP 状态方程 检查能否自启动 驱动方程 将无效状态1010 1111 代入状态方程: J0 = K0 = 1, 1010 1011 0100 1110 1111 1000 J2 = K2 = Q1nQ0n 1100 1011 0100 J3 = Q2nQ1nQ0n,K3 = Q0n 选择下降沿、JK 触发器 能自启动 逻辑图

/1 /0 /0 /0 0111 0000 1001 1000 0110 /0 /0 /0 /0 /0 /0 0011 0100 0101 0001 0010 (二) 十进制同步减法计数器 (略) (三) 十进制同步可逆计数器 (略)

VCC CO Q0 Q1 Q2 Q3 CTT LD 16 15 14 13 12 11 10 9 74160(2) 1 2 3 4 5 6 7 8 CRCP D0D1 D2 D3CTP 地 (四) 集成十进制同步计数器 74160、74162 1. 集成十进制同步加法计数器 (引脚排列与74161相同) 同步计数功能: 保持功能: 异步清零功能: (74162 同步清零) 进位信号保持 同步置数功能: 进位输出低电平

VCC D0 CP RC CO/BO LD D2 D3 16 15 14 13 12 11 10 9 74191 1 2 3 4 5 6 7 8 D1Q1Q0 CTU/DQ2 Q3地 2. 集成十进制同步可逆计数器 (1) 74190 (单时钟,引脚与74191相同) 异步并行置数功能: 同步可逆计数功能: 加法计数 减法计数 保持功能:

VCC D0 CR BO CO LD D2 D3 16 15 14 13 12 11 10 9 74193 1 2 3 4 5 6 7 8 D1Q1Q0 CPD CPU Q2 Q3地 (2) 74192 (双时钟,引脚与74193相同) 异步清零功能: 异步置数功能: 同步可逆计数功能: 加法计数 减法计数 保持功能

VCC R0B R0A CP1 CP0Q0Q3 1 0 0 1 0 0 0 0 14 13 12 11 10 9 8 74290 CP 1 2 3 4 5 6 7 CP Q0 Q1 Q2 Q3 S9A S9B Q2 Q1 地 1 1 1 1 M1 =2 CP0 M1 = 5 CP1 S9A S9B R0B R0A 二*、十进制异步计数器 (三) 集成十进制异步计数器 异步清零功能 异步置“9”功能 CP CP 异步计数功能 M =2 M=5 M=10

VCC R0B R0A CP1 CP0Q0Q3 0 0 0 0 1 0 0 1 14 13 12 11 10 9 8 74290 CP 1 2 3 4 5 6 7 CP Q0 Q1 Q2 Q3 S9A S9B Q2 Q1 地 M1 =2 CP0 1 1 1 1 M1 = 5 CP1 S9A S9B R0B R0A 二*、十进制异步计数器 (三) 集成十进制异步计数器 异步清零功能 异步置“9”功能 CP CP 异步计数功能 M =2 M=5 M=10

异步 清零 同步置数 5.2.4 N 进制计数器 用触发器和门电路设计 方法 清零端 用集成计数器构成 (同步、异步) 置数端 [例] 利用EWB观察同步和异步归零的区别。 六进制 计数器 七进制 计数器