Computação Reconfigurável

290 likes | 417 Views

Computação Reconfigurável. Aula teórica 3. Objetivos. Compreender o fluxo de projeto. Desenvolver projetos simples que incluem dois ficheiros: VHDL (comportamental) e UCF. Desenvolver projetos hierárquicos utilizando VHDL estrutural e comportamental.

Computação Reconfigurável

E N D

Presentation Transcript

Computação Reconfigurável Aula teórica 3

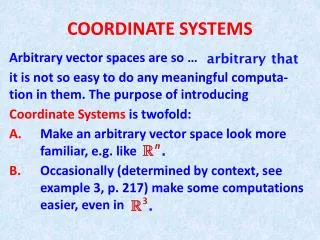

Objetivos • Compreender o fluxo de projeto. • Desenvolver projetos simples que incluem dois ficheiros: VHDL (comportamental) e UCF. • Desenvolver projetos hierárquicos utilizando VHDL estrutural e comportamental. • Compreender processos combinatórios e sequenciais. • Compreender sincronização. • Compreender como utilizar templates. • Compreender como utilizar blocos de memória embutidos.

O fluxo de projeto Iniciar um projeto novo Criar um projeto com base no projeto anterior O projeto anterior vai ser alterado ou

O fluxo de projeto possível • Criar um projeto novo: File → New Project → . . . . • Escolher um projeto (uns projetos) anterior(es) mais parecido(s). • Utilizar opções: Project → Add Copy of Source → . . . .

Passos importantes: • Definir o tipo de FPGA: • Nexys-2/500 • Nexys-2/1200 • Atlys • Escolher o próprio ficheiro de implementação: • para Nexys-2/500 • para Nexys2/1200 • para Atlys www.ieeta.pt/~skl→ Courses→ 2º SemesterComputação Reconfigurável→ Ficheiros UCF para FPGAs da Xilinx (ficheiro rar)

Passos importantes: UCF VHDL

NET "clk" LOC = "B8"; # Bank = 0, Pin name = IP_L13P_0/GCLK8, Type = GCLK, Sch name = GCLK0 # 7 segment display NET "seg<0>" LOC = "L18"; # Bank = 1, Pin name = IO_L10P_1, Type = I/O, Sch name = CA NET "seg<1>" LOC = "F18"; # Bank = 1, Pin name = IO_L19P_1, Type = I/O, Sch name = CB NET "seg<2>" LOC = "D17"; # Bank = 1, Pin name = IO_L23P_1/HDC, Type = DUAL, Sch name = CC NET "seg<3>" LOC = "D16"; # Bank = 1, Pin name = IO_L23N_1/LDC0, Type = DUAL, Sch name = CD NET "seg<4>" LOC = "G14"; # Bank = 1, Pin name = IO_L20P_1, Type = I/O, Sch name = CE NET "seg<5>" LOC = "J17"; # Bank = 1, Pin name = IO_L13P_1/A6/RHCLK4/IRDY1, Type = RHCLK/DUAL, Sch name = CF NET "seg<6>" LOC = "H14"; # Bank = 1, Pin name = IO_L17P_1, Type = I/O, Sch name = CG NET "dp" LOC = "C17"; # Bank = 1, Pin name = IO_L24N_1/LDC2, Type = DUAL, Sch name = DP NET "an<0>" LOC = "F17"; # Bank = 1, Pin name = IO_L19N_1, Type = I/O, Sch name = AN0 NET "an<1>" LOC = "H17"; # Bank = 1, Pin name = IO_L16N_1/A0, Type = DUAL, Sch name = AN1 NET "an<2>" LOC = "C18"; # Bank = 1, Pin name = IO_L24P_1/LDC1, Type = DUAL, Sch name = AN2 NET "an<3>" LOC = "F15"; # Bank = 1, Pin name = IO_L21P_1, Type = I/O, Sch name = AN3 # Leds NET "Led<0>" LOC = "J14"; # Bank = 1, Pin name = IO_L14N_1/A3/RHCLK7, Type = RHCLK/DUAL, Sch name = JD10/LD0 NET "Led<1>" LOC = "J15"; # Bank = 1, Pin name = IO_L14P_1/A4/RHCLK6, Type = RHCLK/DUAL, Sch name = JD9/LD1 NET "Led<2>" LOC = "K15"; # Bank = 1, Pin name = IO_L12P_1/A8/RHCLK2, Type = RHCLK/DUAL, Sch name = JD8/LD2 NET "Led<3>" LOC = "K14"; # Bank = 1, Pin name = IO_L12N_1/A7/RHCLK3/TRDY1, Type = RHCLK/DUAL, Sch name = JD7/LD3 NET "Led<4>" LOC = "E17"; # Bank = 1, Pin name = IO, Type = I/O, Sch name = LD4? s3e500 only NET "Led<5>" LOC = "P15"; # Bank = 1, Pin name = IO, Type = I/O, Sch name = LD5? s3e500 only NET "Led<6>" LOC = "F4"; # Bank = 3, Pin name = IO, Type = I/O, Sch name = LD6? s3e500 only NET "Led<7>" LOC = "R4"; # Bank = 3, Pin name = IO/VREF_3, Type = VREF, Sch name = LD7? s3e500 only #NET "Led<4>" LOC = "E16"; # Bank = 1, Pin name = N.C., Type = N.C., Sch name = LD4? other than s3e500 #NET "Led<5>" LOC = "P16"; # Bank = 1, Pin name = N.C., Type = N.C., Sch name = LD5? other than s3e500 #NET "Led<6>" LOC = "E4"; # Bank = 3, Pin name = N.C., Type = N.C., Sch name = LD6? other than s3e500 #NET "Led<7>" LOC = "P4"; # Bank = 3, Pin name = N.C., Type = N.C., Sch name = LD7? other than s3e500 # Switches NET "sw<0>" LOC = "G18"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = SW0 NET "sw<1>" LOC = "H18"; # Bank = 1, Pin name = IP/VREF_1, Type = VREF, Sch name = SW1 NET "sw<2>" LOC = "K18"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = SW2 NET "sw<3>" LOC = "K17"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = SW3 NET "sw<4>" LOC = "L14"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = SW4 NET "sw<5>" LOC = "L13"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = SW5 NET "sw<6>" LOC = "N17"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = SW6 NET "sw<7>" LOC = "R17"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = SW7

# Buttons NET "btn<0>" LOC = "B18"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = BTN0 NET "btn<1>" LOC = "D18"; # Bank = 1, Pin name = IP/VREF_1, Type = VREF, Sch name = BTN1 NET "btn<2>" LOC = "E18"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = BTN2 NET "btn<3>" LOC = "H13"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = BTN3 Índices do array Nome do sinal Exemplo: # Buttons NET “MyButton<0>" LOC = "B18"; # Bank = 1, Pin name = IP, Type = INPUT, Sch name = BTN0 NET “YourButton" LOC = "D18"; # Bank = 1, Pin name = IP/VREF_1, Type = VREF, Sch name = BTN1 std_logic_vector std_logic

www.ieeta.pt/~skl→ Courses→ 2º SemesterComputação Reconfigurável→ Seção: Matéria importante :

Projetos simples que incluem dois ficheiros: VHDL (comportamental) e UCF library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity MyCase is port ( dipswitches : in std_logic_vector (7 downto 0); leds : out std_logic_vector (7 downto 0) ); end MyCase; architecture Behavioral of MyCase is begin process (dipswitches) begin case conv_integer(dipswitches) is when 0 => leds <= (others=>'1'); -- all leds are ON when 1 => leds <= (3 downto 0 => '1', others=>'0'); -- "00001111" when 2 to 10 => leds <= (0=>dipswitches(0),7=>dipswitches(1),others=>'1'); -- "11111110" when 16|18|20 => leds <= "11110000"; -- "11110000" when others => leds <= (others=>'0'); -- "11111111" end case; end process; end Behavioral;

Projetos simples que incluem dois ficheiros: VHDL (comportamental) e UCF library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity MyCase is port ( dipswitches : in std_logic_vector (7 downto 0); leds : out std_logic_vector (7 downto 0) ); end MyCase; architecture Behavioral of MyCase is begin process (dipswitches) begin case dipswitches is when "000000--" => leds <= (others=>'1'); -- all leds are ON when "--111111" => leds <= (3 downto 0 => '1', others=>'0'); -- "00001111" when "10101010" => leds <= (0=>dipswitches(0),7=>dipswitches(1),others=>'1'); "11111110" when "01010101" => leds <= "11110000"; -- "11110000" when others => leds <= (others=>'0'); -- "11111111" end case; end process; end Behavioral; www.ieeta.pt/~skl→ Courses→ 2º SemesterComputação Reconfigurável→ Secção: Matéria importante : VHDL por ordem alfabética

Projetos hierárquicos utilizando VHDL estrutural e comportamental library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity arrays is port ( clk,reset : in std_logic; LED_out_display : out std_logic_vector(7 downto 0) ); end arrays; architecture Behavioral of arrays is -- definition of one-dimension array of vectors of type std_logic_vector type RAM is array (255 downto 0) of std_logic_vector(7 downto 0); signal my_RAM : RAM; signal divided_clk : std_logic; begin process(clk,reset) -- original input clock variable tmp : integer range 0 to 255; begin if reset = '1' then tmp := 0; elsif rising_edge(clk) then my_RAM(tmp) <= conv_std_logic_vector(tmp,8); if (tmp < 255) then tmp := tmp + 1; else tmp := 0; end if; end if; end process;

Projetos hierárquicos utilizando VHDL estrutural e comportamental process(divided_clk,reset) -- divided clock by the component “clock_divider” variable tmp : integer range 0 to 255; begin if reset = '1' then tmp := 255; elsif rising_edge(divided_clk) then -- output to LEDs of 8-bit vectors in descending order beginning from "11111111", i.e. all -- the LEDs are ON LED_out_display <= my_RAM(tmp); tmp := tmp - 1; end if; end process; to_divide_clock: entity work.clock_divider generic map (how_fast => 23) port map ( clk,reset, divided_clk); end Behavioral;

Projetos hierárquicos utilizando VHDL estrutural e comportamental library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity clock_divider is generic ( how_fast : integer := 25 ); port ( clk,reset : in std_logic; divided_clk : out std_logic ); end clock_divider; architecture Behavioral of clock_divider is signal internal_clock : std_logic_vector (how_fast downto 0); begin process(clk,reset) begin if clk'event and clk = '1' then -- the same as rising_edge(clk) if reset = '1' then -- synchronous reset internal_clock <= (others=>'0'); else internal_clock <= internal_clock+1; end if; end if; end process; divided_clk <= internal_clock(internal_clock'left); -- the most left bit of internal_clock end Behavioral;

Projetos hierárquicos utilizando VHDL estrutural e comportamental library IEEE; use IEEE.std_logic_1164.all; entity FULLADD is port ( A, B, CIN : in std_logic; SUM, CARRY : out std_logic); end FULLADD; architecture STRUCT of FULLADD is signal s1, s2, s3 : std_logic; component half_adder port( A,B : in std_logic; SUM, CARRY : out std_logic); end component; component ORGATE port( A,B : in std_logic; Z : out std_logic); end component; begin u1: half_adder port map(A,B,s1,s2); u2: half_adder port map(s1,CIN,SUM,s3); u3: ORGATE port map(s2,s3,CARRY); end STRUCT; NET "A" LOC = "K18"; NET "B" LOC = "H18"; NET "CIN" LOC = "G18"; NET "CARRY" LOC = "J15"; NET "SUM“ LOC = "J14“; 3 1 2

Processos combinatórios e sequenciais process(clk,reset) variable tmp : integer range 0 to 255; begin if reset = '1' then tmp := 0; elsif rising_edge(clk) then my_RAM(tmp) <= conv_std_logic_vector(tmp,8); if (tmp < 255) then tmp := tmp + 1; else tmp := 0; end if; end if; end process; Processo sequencial. reset assíncrono process(clk,reset) begin if clk'event and clk = '1' then -- the same as rising_edge(clk) if reset = '1' then -- synchronous reset internal_clock <= (others=>'0'); else internal_clock <= internal_clock+1; end if; end if; end process; Processo sequencial. reset síncrono

Processos combinatórios e sequenciais process (dipswitches) begin case conv_integer(dipswitches) is when 0 => leds <= (others=>'1'); when 1 => leds <= (3 downto 0 => '1', others=>'0'); when 2 to 10 => leds <= (0=>dipswitches(0),7=>dipswitches(1),others=>'1'); when 16|18|20 => leds <= "11110000"; when others => leds <= (others=>'0'); end case; end process; Processo combinatório

Compreender sincronização if clk'event and clk = '1' then … if rising_edge(clk) then … if clk'event and clk = ‘0' then … if falling_edge(clk) then … Unidade de controlo Unidade de execução

Blocos de memória embutidos entity ROM_example is generic ( rom_addr_bits : integer := 6; rom_width : integer := 3 ); port ( six_bit_binary_vector : in std_logic_vector(rom_addr_bits-1 downto 0); rom_output : out std_logic_vector(rom_width-1 downto 0) ); end ROM_example; architecture Behavioral of ROM_example is type ROM is array (0 to (2**rom_addr_bits-1)) of std_logic_vector (rom_width-1 downto 0); constant my_ROM : ROM :=("000","001","001","010","001","010","010","011", "001","010","010","011","010","011","011","100", "001","010","010","011","010","011","011","100", "010","011","011","100","011","100","100","101", "001","010","010","011","010","011","011","100", "010","011","011","100","011","100","100","101", "010","011","011","100","011","100","100","101", "011","100","100","101","100","101","101","110"); begin rom_output <= my_ROM(conv_integer(six_bit_binary_vector)); end Behavioral;

Blocos de memória embutidos Sequential (FSM-based) circuit Distributed ROM 3 LSB Distributed ROM 3-bit result 6-bit binary vector Distributed ROM 3-bit result 6-bit binary vector LSB – less significant bits 2-bit result 2-bit result a) 3-bit result Adder 6-bit binary vector MSB – most significant bits b) 3 MSB c)