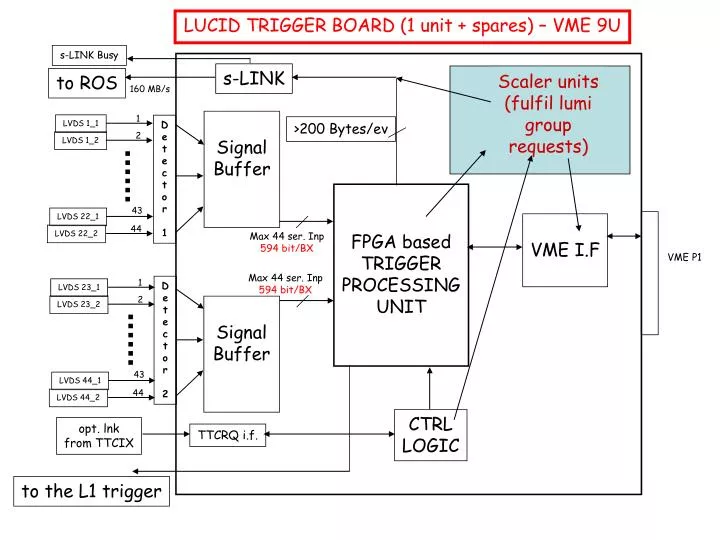

Advanced VME 9U s-LINK Scaler and Trigger Board for High-Speed Data Processing

E N D

Presentation Transcript

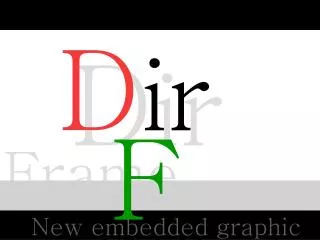

LUCID TRIGGER BOARD (1 unit + spares) – VME 9U s-LINK Busy s-LINK Scaler units (fulfil lumi group requests) to ROS 160 MB/s 1 Signal Buffer LVDS 1_1 D e t e c t o r 1 >200 Bytes/ev 2 LVDS 1_2 FPGA based TRIGGER PROCESSING UNIT 43 LVDS 22_1 VME I.F 44 LVDS 22_2 Max 44 ser. Inp 594 bit/BX VME P1 Max 44 ser. Inp 594 bit/BX 1 D e t e c t o r 2 LVDS 23_1 2 LVDS 23_2 Signal Buffer 43 LVDS 44_1 44 LVDS 44_2 CTRL LOGIC opt. lnk from TTCIX TTCRQ i.f. to the L1 trigger

LARRY (LUCEDRO) TRIGGER BOARD – VME 9U s-LINK Busy s-LINK Scaler units (fulfil lumi group requests) to ROS 160 MB/s 1 LVDS 1_1 D e t e c t o r 1 ~200 Bytes/ev 2 LVDS 1_2 Mezzanine FPGA based TRIGGER PROCESSING UNIT 43 LVDS 22_1 VME I.F 44 LVDS 22_2 44 ser. Inp 594 bit/BX VME P1 44 ser. Inp 594 bit/BX 1 D e t e c t o r 2 LVDS 23_1 2 LVDS 23_2 Mezza nine Tracks from AM 43 LVDS 44_1 FIFO 44 LVDS 44_2 opt. lnk from TTCIX CTRL LOGIC TTCRQ i.f. Hits to AM Clock BX CTRL ? TRIGGER