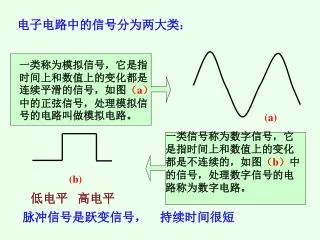

一类称为模拟信号,它是指时间上和数值上的变化都是连续平滑的信号,如图 ( a ) 中的正弦信号,处理模拟信号的电路叫做模拟电路。

(a). (b). 电子电路中的信号分为两大类 :. 一类称为模拟信号,它是指时间上和数值上的变化都是连续平滑的信号,如图 ( a ) 中的正弦信号,处理模拟信号的电路叫做模拟电路。. 一类信号称为数字信号,它 是指时间上和数值上的变化 都是不连续的,如图 ( b ) 中 的信号,处理数字信号的电 路称为数字电路。. 低电平 高电平. 脉冲信号是跃变信号, 持续时间很短. 数字电路和模拟电路的区别:. ( 1 )信号不同:. 电路中: 低电平 高电平. 基本数字:逻辑 0 逻辑 1. ( 2 )研究的问题不同。.

一类称为模拟信号,它是指时间上和数值上的变化都是连续平滑的信号,如图 ( a ) 中的正弦信号,处理模拟信号的电路叫做模拟电路。

E N D

Presentation Transcript

(a) (b) 电子电路中的信号分为两大类: 一类称为模拟信号,它是指时间上和数值上的变化都是连续平滑的信号,如图(a)中的正弦信号,处理模拟信号的电路叫做模拟电路。 一类信号称为数字信号,它 是指时间上和数值上的变化 都是不连续的,如图(b)中 的信号,处理数字信号的电 路称为数字电路。 低电平 高电平 脉冲信号是跃变信号, 持续时间很短

数字电路和模拟电路的区别: (1)信号不同: 电路中: 低电平 高电平 基本数字:逻辑0 逻辑1 (2)研究的问题不同。 模拟电路:输入输出之间的大小、相位等问题。 数字电路:输入输出之间的逻辑关系。

工具 (3)分析方法不同。 模拟电路:微变等效电路、图解法 数字电路:逻辑分析与设计,逻辑代数 (4)电路组成相同,但元件工作状态不同。 模拟电路:晶体管多工作在放大状态 数字电路 :晶体管工作在开关状态,也就是 交替地工作在饱和与截止两种状态。

第13章 门电路和组合逻辑电路 13.1 基本门电路及其组合 13.2 TTL门电路 *13.4组合逻辑电路的分析和设计 *13.5加法器 *13.6编码器 13.7译码器和数字显示

13.1 基本门电路及其组合 13.1.1逻辑代数的基本概念 • 数字电路输入输出是逻辑关系 • 逻辑是指事物的因果关系,或者说条件 和结果的关系

逻辑变量与逻辑函数 逻辑函数:如果对应于输入逻辑变量A、B、C、…的每一组确定值,输出逻辑变量Y就有唯一确定的值,则称Y是A、B、C、…的逻辑函数。记为 注意:1.逻辑变量的取值只有两种,即逻辑0和逻辑1。 2.变量取值须经定义才有意义。 • 研究工具 逻辑代数(布尔代数)

Y=AB 13.1.1 、三种基本逻辑运算 1、与逻辑(与运算) 开关A,B 串联,控制 灯泡Y: 真值表

与逻辑的定义:仅当决定事件(Y)发生的所有条件(A,B,C,…)均满足时,事件(Y)才能发生。表达式为:与逻辑的定义:仅当决定事件(Y)发生的所有条件(A,B,C,…)均满足时,事件(Y)才能发生。表达式为: Y=A B C… 与逻辑(与运算) 逻辑符号

2、或逻辑(或运算) 开关 A,B 并联 控制 灯泡 Y: Y=A+B 真值表

逻辑符号 或逻辑(或运算) 或逻辑的定义:当决定事件(Y)发生的各种条件(A,B,C,…)中,只要有一个或多个条件具备,事件(Y)就发生。表达式为: Y=A+B+C+…

Y=A 3、非逻辑(非运算) 非逻辑指的是逻辑的否定。当决定事件(Y)发生的条件(A)满足时,事件不发生;条件不满足,事件反而发生。表达式为: 开关A控制灯泡Y: 逻辑符号 真值表

(2)或非运算:逻辑表达式为: 常用的逻辑运算 (1)与非运算:逻辑表达式为:

(3)异或运算:逻辑表达式为: (4)同或运算:逻辑表达式为:

(5) 与或非运算:逻辑表达式为: 上述逻辑运算的实现依赖于门电路

门电路是实现一定逻辑关系的电路,是组成数字电路的门电路是实现一定逻辑关系的电路,是组成数字电路的 基本单元 高电平 “1” 正逻辑: “0” 低电平 逻辑电平:高电平、低电平 一定电压范围(不是某固定值) 如:TTL电路:高电平额定值:3V(2—5V) 低电平额定值:0.3V(0—0.8V)

13.1.2 分立元件门电路简介 1、二极管与门 Y=AB

2、二极管或门 Y=A+B

3、三极管非门 Y A

+5v R1 B1 A C1 B 13.2 TTL集成门电路 13.2. 1TTL与非门的基本原理 +5V R2 R4 R1 T1 B1 T3 C1 A B T2 Y T4 R3

+5V R4 B1= 0 R2 R1 T3 拉电流 B1 T1 A B T2 AB 任= 0 Uo Y= 1 +5v T4 R3 R1 RL B1 A C1 B 设 uA= 0.3V Uo= 5– Ube3– UD– UR2(小) = 5– 0.7– 0.7=3.6V VB1= 0.3+0.7= 1V T2 、T4 截 止 T3导 通

+Vcc R1 T1 +5V R2 R1 R4 VB1=2.1V VC2=1V T3 uo=0.3V T1 A B T2 Uo Y=0 AB全=1 T4 R3 设 UA=UB=3.6V R5 灌电流 VB1升高,足以使T2 ,T4导通 VC2=VCE2+VBE4=0.3+0.7=1V,使T3截止。

二极管D截止,Y=AB 13. 2. 2三态输出门电路 +5V R4 R2 R1 VB2=1V VB1=1V D T3 EN T2 A B T1 Y EN=1时, T4 R3 EN=0时 VB1=1V, T2 、T4截止; 二极管D导通,使VB2=1V,T3截止,输出端开路(高阻状态)

功能表 符号 A & F B 功能表 符号 & A F B 三态门的符号及功能表 使能端高电平 起作用 使能端低电平 起作用

A2B2 EN1 0 EN2 1 EN3 0 三态门的用途 三态门主要作为TTL电路与总线间的接口电路。 公用总线 工作时,EN1、EN2、EN3轮流接入高电平。将不同数据分时送入总线。 A2 B2

& & & & 14 13 12 11 10 9 8 +VC 74LS00 地 1 2 3 4 5 6 7 13. 2. 3 TTL与非门组件 TTL与非门组件就是将若干个与非门电路,经过集成电路工艺制作在同一芯片上。 74LS00组件含有 两个输入端的与 非门四个。

逻辑门电路使用中的几个问题 (1)对于各种集成电路,使用时一定要在推荐的工作条件范围内,否则将导致性能下降或损坏器件。 (2)输入端悬空 TTL电路多余的输入端悬空表示输入为高电平; CMOS电路多余的输入端不允许悬空,否则电路将不能正常工作。

V CC & & A A B B (b) (a) A ≥1 ≥1 A B B (b) (a) 三、多余输入端的处理 (1)对于与非门及与门,多余输入端应接高电平,比如直接接电源正端,也可以与有用的输入端并联使用 (2)对于或非门及或门,多余输入端应接低电平,比如直接接地;也可以与有用的输入端并联使用。

作业: A选择题:13.1.1~13.4.9(不用交) B基本题:13.1.4、13.1.5、

13.3逻辑代数 13.3.1 逻辑代数的基本定律 一、基本运算规则 A+0=A A+1=1 A · 1=A A · 0 =0

A+BC=(A+B)(A+C) 二、基本代数规律 A+B=B+A 交换律 A• B=B • A A+(B+C)=(A+B)+C=(A+C)+B 结合律 A• (B • C)=(A • B) • C 分配律: A(B+C)=AB+AC

反演规则:逻辑表达式Y,如果将表达式中的所有“·”换成“+”,“+”换成“·”,反演规则:逻辑表达式Y,如果将表达式中的所有“·”换成“+”,“+”换成“·”, “0”换成“1”,“1”换成“0”, 原变量换成反变量,反变量换成原变量, 所得表达式为Y A+AB=A+B A · B ·C ···· =A+B+C+···· A+B+C+···· = A · B · C···· 吸收律: A+AB=A A(A+B)=A 反演律:

Y=BC+A A Y 1 B & C > 1 13.3.2 逻辑函数的表示方法与转换 1. 逻辑代数式 2.逻辑图 3.真值表 4.卡诺图

真值表 设A、B、C为输入变量,Y为输出变量。 逻辑代数式

13.3.3 逻辑函数的化简 一、逻辑函数化简的意义:逻辑表达式越简单,实现它的 电路越简单,电路工作越稳定可靠。 二、逻辑函数化简的目的:通常是得到最简与或表达式。 三、最简“与或式”标准:与项个数最少,各与项中变量数 最少。

利用公式A+A=1,将两项合并为一项,并消去一个变量。利用公式A+A=1,将两项合并为一项,并消去一个变量。 例:证明A+AB+BC=A+B A+AB+BC 1.利用逻辑代数公式化简 1、并项法 2、吸收法 =A+B+BC =A+B(1+C) =A+B

4、加项法 利用公式A+A=A 3、配项法 例 :证明AB+AC+BC=AB+AC AB+AC+BC=AB+AC+(A+A)BC =AB+AC+ABC+ABC =AB+ABC+AC+ABC =AB(1+C)+AC(1+B) =AB+AC

例:证明:若 Y=AB+AB 则 Y=AB+A B Y=(A+B)•(A+B) =AA+AB+A B+BB =AB+A B 5.运用反演规则

2 逻辑函数的卡诺图化简法 (1)最小项:在n个变量逻辑函数中,若m为包含n个因子的乘积项,而且这n个变量均以原变量或反变量的形式在m中出现一次,则称m为该组变量的最小项。 n个变量,有2n个最小项 逻辑相邻的最小项:两个最小项只有一个因子互为反变量 (2)最小项常用符号mi表示

例1:Y=ABC+BC=ABC+BC(A+A) =ABC+ABC+ABC (3)最小项表达式 任何一个逻辑函数都可以表示成若干个最小项的 和,即最小项表达式,它是一个标准“与—或”表达式, 而且这种形式是唯一的。 =m6+ m7+m3 最小项表达式 =( m3 , m6, m7)

B 0 1 A 0 1 卡诺图 :一种函数表示法,按一定规律画的方块图。 定义:将n变量的全部最小项各用一个小方块表示,并使具有逻辑相邻性的最小项在几何位置上也相邻。 0 0 1 1

相邻项举例: 3项的相邻项有:1,2,7 (2)三变量卡诺图: C 3

(3)四变量卡诺图: 0项的相邻项有:1,2,4,8 0 卡诺图构成的重要原则:几何相邻性:即两个几何位置 相邻的单元其输入变量的取值只能有一位不同。

用卡诺图表示逻辑函数 将函数所含全部最小项用1填入,其余填0。 1、函数是以真值表给出 例

BC =A(B+B)+B(A+A) A 00 01 11 10 0 1 B 1 0 Y=ABC+ABC+ABC A 0 1 2、以最小项表达式给出: 3、以一般形式给出: Y=A+B 0 0 0 0 0 1 0 1 1 1 B 1 1 两个相邻单元取值同为1,可以将这两个最小项合并成一项,并消去一个变量。

四. 用卡诺图化简 BC 10 11 00 01 A 0 1 两个相邻单元取值同为1,可以将这两个最小项合并成一项,并消去一个变量。

BC BC Y=ABC+ABC+ABC+ABC A A 00 01 11 10 00 01 11 10 =AC(B+B)+AC(B+B) 0 1 0 1 =AC+AC Y=ABC+ABC+ABC+ABC Y=A 如果是四个几何相邻单元取值同为1, 则可以合并,并消去两个变量。 1 1 1 1 =C 1 1 1 1

BC A 00 01 11 10 0 1 CD AB 00 01 11 10 00 01 11 10 Y= D 如果是八个相邻单元取值同为1, 则可以合并,并消去三个变量。 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 Y= 1

CD CD AB AB 00 01 11 10 00 01 11 10 00 01 11 10 00 01 11 10 Y= BD 1 1 1 1 1 1 1 1

CD CD BCD AB 00 01 11 10 00 01 11 10 BD BC Y=A+CD+BC+BD+BCD 例 :某逻辑函数的表达式是: Y=(AB.C.D) =( m0 , m2 , m3 , m5 , m6 , m8 , m9 , m10 , m11 , m12 , m13 , m14 , m15) 试化简 =(0.2.3.5.6.8.9.10.11. 12.13.14.15) 1 0 1 1 0 1 0 1 A 1 1 1 1 1 1 1 1

用卡诺图化简遵循的原则: (1)相临最小项的个数是2N个,并组成矩形,可以合并。 ( 2)每个矩形组应包含尽可能多的最小项; (3)矩形组的数目应尽可能少; (4)各最小项可以重复使用,即同一个单元可以被圈在不同的矩形组内; (5)所有等于1的单元都必须被圈过; (6)每一矩形组至少有一个未被圈过的最小项