Datapath and Control: MultiCycle Implementation

Datapath and Control: MultiCycle Implementation. Performance of Single Cycle Machines. Assume following operation times: Memory units : 200 ps ALU and adders : 100 ps Register File (read or write): 50 ps Mux, control unit, PC access, sign extension unit, wires : 0 ps.

Datapath and Control: MultiCycle Implementation

E N D

Presentation Transcript

Performance of Single Cycle Machines • Assume following operation times: • Memory units : 200 ps • ALU and adders : 100 ps • Register File (read or write): 50 ps • Mux, control unit, PC access, sign extension unit, wires : 0 ps Clock cycle must cover longest instruction cycle period = 600ps (inefficient!)

Clocking: single-cycle vs. multicycle Single-cycle Implementation clock waste waste beq $t0,$t1,L add $t0,$t1,$t2

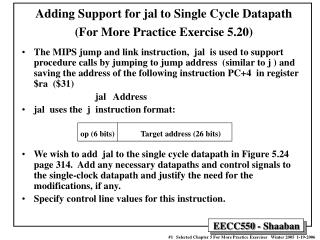

Multicycle Implementation • Instruction execution divided into steps • Each step will take one clock cycle (not each instruction) [CPI > 1] • shorter clock cycle: cycle time constrained by longest step, not longest instruction • simpler instructions take fewer cycles higher overall performance

Clocking: single-cycle vs. multicycle Single-cycle Implementation clock waste waste beq $t0,$t1,L add $t0,$t1,$t2 Multicycle Implementation clock add $t0,$t1,$t2 beq $t0,$t1,L • Multicycle Implementation: less waste=higher performance

How fast can we run the clock? • Depends on how much we want done per clock cycle • Can do: several “inexpensive” datapath operations per clock • simple gates (AND, OR, …) • single datapath registers (PC) • sign extender, left shifter, multiplexor • PLUS: exactly one “expensive” datapath operation per clock • ALU operation • Register File access (2 reads, or 1 write) • Memory access (read or write)

Multicycle Instruction Execution 1: fetch instruction, PC=PC+4 2: decode, fetch registers, branch target 3: execute/compute data address/branch 4: access memory/complete R-type 5: store memory content to register

MIPS-lite Multicycle Version Multicycle Datapath (overview) PC Instruction Register ReadReg1 Address Memory A Readdata 1 ReadReg2 A L U Instruction or Data ALU- Out Registers B Readdata 2 WriteReg Data MemoryData Register Data • One ALU (no extra adders) • One Memory (no separate Imem, Dmem) • New Temporary Registers

Multicycle Implementation • Datapath changes • one memory: both instructions and data (because can access on separate steps) • one ALU (eliminate extra adders) • extra “invisible” registers to capture intermediate (per-step) datapath results

Sgn Ext- end Multicycle Datapath: Add Multiplexors PC Address ReadReg1 M u x 25:21 Mem Readdata1 zero A L U A ALU- Out ReadReg2 M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs WriteData MDR M u x Note inputs to multiplexors << 2

Sgn Ext- end Multicycle Datapath: Add Multiplexors PC Address ReadReg1 M u x 25:21 Mem Readdata1 zero A L U A ALU- Out ReadReg2 M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs WriteData MDR M u x Note inputs to multiplexors << 2

Sgn Ext- end ALU Control Datapath + Control Points IRWrite RegWrite PCWrite MemRead PCSrc MemWrite ALUSrcA RegDst IorD PCWrite- Cond PC M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs 4 WriteData MDR M u x << 2 2 2 (funct) 5:0 ALUSrcB MemtoReg ALUOp

IRWrite RegWrite PCWrite MemRead PCSrc=0 MemWrite ALUSrcA=0 RegDst=x IorD=0 PCWrite- Cond Sgn Ext- end ALU Control 2 ALUSrcB=01 MemtoReg=x ALUOp=00 Cycle 1 Datapath: IR=Mem[PC]; PC=PC+4 PC M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 IR 0 1M 2 u 3 x Regs 4 WriteData MDR M u x (funct) 5:0 << 2 IR=Mem[PC]; PC=PC+4 2

IRWrite RegWrite PCWrite MemRead PCSrc=x MemWrite ALUSrcA=0 RegDst=x IorD=x PCWrite- Cond Sgn Ext- end ALU Control 2 ALUSrcB=11 MemtoReg=x ALUOp=00 Cycle 2: A=Reg[IR25:21]; B=Reg[IR20:16]; ALUOut= PC + sgn-ext(IR15:0) << 2 PC M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 IR 0 1M 2 u 3 x Regs 4 WriteData MDR M u x (funct) 5:0 A=Reg[IR25:21];B=Reg[IR20:16]; << 2 ALUOut= PC + sgn-ext(IR15:0) << 2 2 2

IRWrite RegWrite PCWrite MemRead PCSrc=x MemWrite ALUSrcA=1 RegDst=x IorD=x PCWrite- Cond Sgn Ext- end ALU Control 2 ALUSrcB=00 MemtoReg=x ALUOp=10 Cycle 3: R-format: ALUOut = A op B PC M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs 4 WriteData MDR M u x (funct) 5:0 << 2 ALUOut=A op B 2

IRWrite RegWrite PCWrite MemRead PCSrc=x MemWrite ALUSrcA=x RegDst=1 IorD=x PCWrite- Cond Sgn Ext- end ALU Control 2 ALUSrcB=x MemtoReg=0 ALUOp=x Cycle 4 R-format: Reg[IR15:11] = ALUOut PC M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs 4 WriteData MDR M u x (funct) 5:0 << 2 Reg[IR15:11] = ALUOut 2

IRWrite RegWrite PCWrite MemRead PCSrc=01 MemWrite ALUSrcA=1 RegDst=x IorD=x PCWrite- Cond Sgn Ext- end ALU Control 2 ALUSrcB=00 MemtoReg=x ALUOp=01 Cycle 3 beq: if (A==B) PC =ALUOut PC M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs 4 WriteData MDR M u x (funct) 5:0 << 2 if (A==B) PC =ALUOut 2

Sgn Ext- end ALU Control Cycle 3 lw/sw: ALUOut = A + sgn-ext(IR15:0) IRWrite RegWrite PCWrite MemRead PCSrc=x MemWrite ALUSrcA=1 RegDst=x IorD=x PC PCWrite- Cond M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs 4 WriteData MDR M u x (funct) 5:0 << 2 ALUOut = A + sgn-ext(IR15:0) 2 2 ALUSrcB=10 MemtoReg=x ALUOp=00

Sgn Ext- end ALU Control Cycle 4 lw:MDR = Mem[ALUout] IRWrite RegWrite PCWrite MemRead PCSrc=x MemWrite ALUSrcA=x RegDst=x IorD=1 PCWrite- Cond PC M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs 4 WriteData MDR M u x (funct) 5:0 << 2 MDR = Mem[ALUout] 2 2 ALUSrcB=x MemtoReg=x ALUOp=x

Sgn Ext- end ALU Control Cycle 5 lw: Reg[IR15:11] = MDR IRWrite RegWrite PCWrite MemRead PCSrc=x MemWrite ALUSrcA=x RegDst=0 IorD=x PCWrite- Cond PC M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs 4 WriteData MDR M u x (funct) 5:0 << 2 Reg[IR15:11] = MDR 2 2 ALUSrcB=x MemtoReg=1 ALUOp=x

Sgn Ext- end ALU Control Cycle 4 (sw): Mem[ALUOut] = B IRWrite RegWrite PCWrite MemRead PCSrc MemWrite ALUSrcA RegDst IorD=1 PCWrite- Cond PC M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs 4 WriteData MDR M u x (funct) 5:0 << 2 Mem[ALUOut] = B 2 2 ALUSrc MemtoReg ALUOp

Sgn Ext- end ALU Control Datapath + Control Points IRWrite RegWrite PCWrite MemRead PCSrc MemWrite ALUSrcA RegDst IorD PCWrite- Cond PC M u x ReadReg1 Address M u x 25:21 z Readdata1 Mem A L U A ReadReg2 ALU- Out M u x 20:16 Read Data Readdata2 B WriteReg M u x 15:0 Write Data 4 15:11 0 1M 2 u 3 x IR Regs 4 WriteData MDR M u x << 2 2 2 (funct) 5:0 ALUSrcB MemtoReg ALUOp

FSM for Main Control Unit • All write control signals not asserted explicitly are deasserted • All Multiplexer controls not specified explicitly are don’t care • asserted if name only • otherwise exact value 0 1