Methods for checking simulation correctness

Discover 3 methods for checking simulation correctness: Predict and check, Check as you go, Trace and check later. Understand how each method works, its advantages, disadvantages, and where they are typically utilized in processor, chip, and system verification.

Methods for checking simulation correctness

E N D

Presentation Transcript

Methods for checking simulation correctness How do you know if your testcase passed or failed?

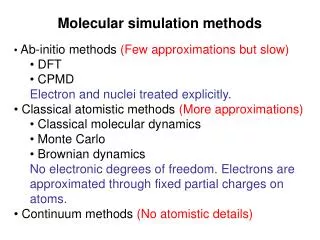

3 checking methods • Predict and check • Check as you go • Trace and check later

Predict and check • How does it work? • Create the stimulus • Run the stimulus against an independent reference model • Save the predicted results • Run the stimulus on the simulation model • Compare the simulation results against the predicted results • Where is it used? • Processor verification • Chip verification

Predict and check - cont'd ... m 00000100 830445cd6673da21 m 00000108 34539877c7c82243 m 00000110 cd565479802ad999 ... i ld r4, (100) i ld r8, (110) i add r4, r8, r3 i add r3, r4, r8 i add r3, r3, r8 ... m 00000100 830445cd98098001 m 00000108 34539877c7c82243 ...

Predict and check - cont'd Disadvantages Advantages • Does not require run time interaction with the model • Reference model tends to be highly reusable • Quickly up and running and producing bugs • Bugs must propagate to a result • Bugs can be overwritten • Cascade affect can make it difficult to isolate the source of the problem • Results have to be predictable from the testcase alone • Input may have to be restricted to guarantee predictable results

Check as you go • How does it work? • Create an environment to stimulate, observe and predict the behavior of the simulation model • As the simulation is running the environment should compare the expected behavior to the observed behavior • Stop the testcase when the expected and observed behavior is different • Where is it used? • unit verification • chip verification • subsystem verification

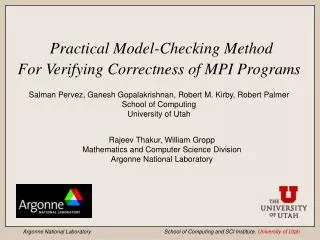

Global transaction monitor ("Scoreboard") Driver A IM A Unit monitor Driver B IM B IM C Driver C Check as you go - cont'd DUV (IM = Interface Monitor)

Check as you go - cont'd Advantages Disadvantages • Highly effective at finding all types of bugs • Stops the test as soon as the error is detected • Error messages can be very specific and are usually directly related to the problem • Environment can choose what to do next based upon observed events • Environment code is greater than the VHDL • Environment may be created to match the implementation instead of the design intent • Takes time to make the environment effective • Requires run time iteraction with the model • Code is very design specific and not reusable

Trace and check later • How does it work? • Tracers are created to observe and record the activity of specific interfaces • During the simulation of the testcase the trace information is gathered and saved • After the simulation is complete, the tracers are analyzed for any rule violations • Where is it used? • system verification • protocol verification

Core Core L2 Cache L2 Cache L1 Cache L1 Cache System Bus Memory Controller I/O Behavior I/O Hub I/O Bus Trace and check later - cont'd

Trace and check later - cont'd Disadvantages Advantages • Don't spend simulation time checking results • Stimulus generation is not constrained • Allows correlation between distant parts of the design under verification • Tracers and checkers reusable for standard interfaces • Bugs must propagate to an observed interface to be seen • Testcase will run to completion before any error checking is started (wasted cycles) • Requires run time interaction with the model

Memory Controller Data Response Timeout P1 P4 P5 P3 P6 P2 Respond Shared Read addr 100 Switch Node Switch Other Nodes I/O

![READ [PDF] Simulation Methods for Polymers](https://cdn7.slideserve.com/12344038/slide1-dt.jpg)