聚積狀態

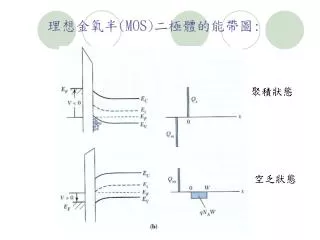

理想金氧半 (MOS) 二極體的能帶圖 :. 聚積狀態. 空乏狀態. 理想金氧半 (MOS) 二極體的能帶圖 :. 反轉 (inversion) 電荷分佈圖. 電場分佈圖. 電位分佈圖. SiO 2 -Si MOS 二極體. 電特性最接近理想 MOS 二極體。 與理想二極體最大差異: a. 金屬電極與半導體之 功函數差 q ms 不為零 ; b. 氧化層中或介面處有電荷存在。 所以熱平衡時的半導體區之能帶圖有彎曲,不為 平帶 情形 ( flat-band condition ) 。

聚積狀態

E N D

Presentation Transcript

理想金氧半(MOS)二極體的能帶圖: 聚積狀態 空乏狀態

理想金氧半(MOS)二極體的能帶圖: 反轉(inversion)電荷分佈圖 電場分佈圖 電位分佈圖

SiO2-Si MOS二極體 • 電特性最接近理想MOS二極體。 • 與理想二極體最大差異:a.金屬電極與半導體之功函數差qms不為零;b.氧化層中或介面處有電荷存在。 • 所以熱平衡時的半導體區之能帶圖有彎曲,不為平帶情形(flat-band condition )。 ms與使半導體恢復平帶狀況之電壓(平帶電壓flat-band voltage)為所關心之量。

事實上,因為m、 有能量差,故形成MOS結構時,氧化層就會跨有一個電位差Vox0,半導體能帶也會有彎曲es0。 表示 氧化層中或介面處有電荷存在。 功函數差(Work function difference ) 熱平衡狀態下 =0.9V e’m:修正的金屬功函數功函數 e’:修正半導體的電子親和力 s0:表面電位

由費米能階至真空能階之能量為: eVox0+ eI + em’ es0-efp 由費米能階至真空能階之能量為: eI + e’ + Eg/2 - (es0-efp)

功函數差ms(續) • 將金屬區和半導體區的費米能階至真空能階之能量相比較: 整理可得: 定義為功函數差ms

功函數差ms(續) p型基板的功函數差 以p+複晶矽(假設EF=Ev)為閘極:

功函數差ms(續) 以n+複晶矽(假設EF=Ec)為閘極,p型基板:

功函數差ms(續) n型基板的功函數差

平帶電壓(Flat-band voltage) • 定義:使半導體區之能帶無彎曲所施加的閘極電壓。 • 加閘極電壓,跨於氧化層及半導體的表面電位會改變: 即半導體層內無電荷存在 即ms

Vox ox 平帶電壓VFB(續) • 當VG = VFB時,s = 0,故可得: • 氧化層所跨電位可以下分析得知: • 故可得平帶電壓公式: 平衡狀態 平帶狀態 平帶狀態下,假設氧化層電荷QO存在與半導體之界面處(即x0 = d),則可得:

氧化層電荷: • 可區分為四種電荷: 1.介面捕獲電荷(Qit) 2.固定氧化物電荷(Qf) 3.氧化層陷住電荷(Qot) 4.可動離子電荷(Qm)

~介面陷住電荷Qit~ (interface trapped charge) 產生原因: 起因於Si-SiO2介面的不連續性及介面上的未飽和鍵。通常Qit的大小與介面化學成分有關。 改善方法: 於矽上以熱成長二氧化矽的MOS二極體使用低溫(約450℃)氫退火來中和大部分的介面陷住電荷,或選擇低阻陷的晶片。

~固定氧化層電荷Qf~ (fixed oxide charge) 產生原因: 當氧化停止時,一些離子化的矽就留在介面處(約30Å處)。這些離子及矽表面上的不完全矽鍵結產生了正固定氧化層電荷Qf。 改善方法: 可藉由氧化製程的適當調整,或是回火(Annealing)來降低其影響力或是選擇較佳的晶格方向。

~氧化層陷住電荷Qot~(oxide trapped charge) 產生原因: 主要是因為MOS操作時所產生的電子電洞被氧化層內的雜質或未飽和鍵所捕捉而陷入。 改善方法: 可利用低溫回火消除掉。

~可移動離子電荷Qm~ (mobile ionic charge) 產生原因: 通常是鈉、鉀離子等鹼金屬雜質,在高溫和高正、負偏壓操作下可於氧化層內來回移動,並使得電容-電壓特性沿著電壓軸產生平移。 改善方法: 藉由在矽氧化製成進行時,於反應氣體進行時加入適量HCl,其中的Cl離子會中和SiO2層內的鹼金屬離子。

氧化層電荷對CV圖的影響 • 其中平帶電壓狀態介於聚積狀態與空乏狀態之間: • 由平帶電壓公式可知: Qo為正時,平帶電壓會比ms小 Qo為負時,平帶電壓會比ms大

氧化層電荷對CV圖的影響(續) • 由平帶電壓的分析可知,當氧化層電荷為正時,CV圖會往左平移,且電荷越多,平移量越多;當氧化層電荷為負時,CV圖會往右平移。 Qo包括:固定氧化層電荷Qf、氧化層陷住電荷Qot以及移動性離子電荷Qm。

界面電荷對CV圖的影響 • 表面週期性終止,有懸鍵產生,在禁制能帶會形成界面態階。 • 電荷可在半導體與界面態階之間流動,隨著偏壓之改變,界面態階與費米能階的相關位置不同,界面的淨電荷也會改變。 一般而言,在EFi上方的稱為受體態階,在EFi下方的稱為施體體態階。 施體態階:因費米能階在施體態階之上(填滿)時,為電中性;費米能階在施體態階之下(空的)時,為帶正電。 受體態階:因費米能階在受體態階之下(空的)時,為電中性;費米能階在施體態階之上(填滿)時,為帶負電。

界面電荷對CV圖的影響(續) • 以p型半導體為例: 聚積狀態下(偏壓為負),受體態階都在費米能階之上,故為中性;但部分施體態階在費米能階之上,故為帶正電。 即聚積狀態下,界面淨電荷為正。 偏壓轉為正,當EF正好等於EFi時,受體態階都在費米能階之上,故為中性;施體態階都在費米能階之上,故也為中性。 即偏壓由負轉正時,正好有一個狀態(中間能隙),界面淨電荷為零。

界面電荷對CV圖的影響(續) • 以p型半導體為例: 反轉狀態下(偏壓為更正),施體態階都在費米能階之下,故為中性;但部分受體態階在費米能階之下,故為帶負電。 即反轉狀態下,界面淨電荷為負。 綜合以上所述,閘極所加之偏壓由負變為正時,界面態階的淨電荷由正變到零再到負,故CV圖與理想結果比較,應該是部分右偏,部分左偏。

界面電荷對CV圖的影響(續) 界面電荷為正,故往左偏移 界面電荷為負,故往右偏移 和理想CV圖比較圖形變得更平滑

氧化層電荷與界面電荷影響之比較 氧化層電荷效應:圖形形狀不變,但平移。 界面電荷效應:圖形形狀改變,變得更平滑。

臨限電壓(Threshold voltage) • 產生強反轉所需加的閘極偏壓。 • 已知 故p型半導體產生強反轉( s = 2fp )所需的臨限電壓為:

臨限電壓(續) • 由上式可知:半導體材料、金屬材料(ms);氧化層材料(ox、tox) ;氧化層電荷(Qss’) ;摻雜濃度(QSD’、fp)均會影響臨限電壓。 • 臨限電壓是MOSFET的重要參數,表示電晶體導通的開始點(on),故應適當選擇以上之製程條件,使得所製作之金氧半電晶體之臨限電壓落在電路設計的電壓範圍內。

臨限電壓(續) • 隨著氧化層電荷與半導體摻雜濃度的不同,臨限電壓有的為正有的為負。 • VTN < 0:摻雜濃度較低時可得。表示尚未接偏壓時就有反轉電子,為導通狀態,負的臨限電壓才能使之off,稱為空乏模式。 • VTN > 0:摻雜濃度較高時可得。表示尚未接偏壓時為off,正的臨限電壓才能使之產生反轉電子,變為導通狀態,稱為增強模式。

臨限電壓(續) 對n型半導體基板而言,臨限電壓為: 以正的氧化層電荷而言,臨限電壓皆為負。表示尚未接偏壓時為off,負的臨限電壓才能使之產生反轉電洞,變為導通狀態,故不論摻雜濃度為多少,皆屬增強模式。

源極 閘極 汲極 L:通道長度 Z:通道寬度 d:氧化層厚度 rj:接面深度 基本的 MOSFET結構 加適當的閘極電壓使得閘極下方產生反轉層,形成通道,連接源極與汲極區。源極為載子的來源,經過通道流向汲極。 當基板為p型時,載子為電子,故電流由汲極流向源極;當基板為n型時,載子為電洞,故電流由源極流向汲極。

基本的MOSFET元件 • N通道增強模式 • N通道空乏模式 • P通道增強模式 • P通道空乏模式 基板為p型半導體,汲極與源極為n型摻雜。 基板為n型半導體,汲極與源極為p型摻雜。

N通道增強模式(Enhamcement mode) N通道增強模式:在零閘極電壓,氧化層下沒有電子反轉層,需加正閘極電壓才會有反轉層。 沒接通 電子由基底進入

N通道空乏模式(Depletion mode) • N通道空乏模式:在零閘極電壓,氧化層下已有電子反轉層存在。 接通 電子由基底進入

P通道增強模式 • P通道增強模式:在零閘極電壓,氧化層下沒有電洞反轉層,需加負閘極偏壓才會有反轉層。 沒接通 電子由基底流出

P通道空乏模式 • P通道空乏模式:在零閘極電壓,氧化層下已有電洞反轉層存在。 接通 電子由基底流出

工作原理 • VG < VT,源極到汲極間好似二個背對背的pn接面,加一汲極電壓,只有微弱的逆向漏電流。 • VG > VT,半導體表面產生反轉電子,只要加一點汲極電壓,可使電子由源極流向汲極,產生通道電流ID。 • 理想狀況下,閘極電壓只控制反轉電子的多寡,不會使電子通過氧化層至閘極端。 很小

產生反轉層 能帶圖維持水平

通道電導(Channel conductance) • 當VG >VT,VDS比較小時,ID與VDS成正比,好似電阻(故稱為線性區),可表示為: 線性區 通道電導: 反轉電子遷移率 Qn’為單位面積反轉電子數,當VG越大, Qn’越大,故gd越大。 VG可調變通道電導,進而決定通道電流。

線性區 加VDS使得EFn與EFp分開,半導體表面附近的能帶圖彎曲更大,故空乏區寬度越大。

小的汲極電壓使得能帶圖變成好似斜坡,電子很容易由S到D,產生電流。小的汲極電壓使得能帶圖變成好似斜坡,電子很容易由S到D,產生電流。

飽和區(Saturation region) • 當VDS漸增,靠近汲極附近的氧化層所跨的電壓減少,產生反轉電荷的能帶彎曲減少,故反轉電子減少,ID-VDS圖的斜率漸減。 • 當汲極電壓增加至使跨於汲極端氧化層電壓恰等於VT,此時反轉電子密度為零(稱為夾止),故ID-VDS圖的斜率變為零,即電流維持不變,達到飽和。 • 此時

電場 飽和區(續) • 當汲極電壓大於VDS(sat)反轉電荷為零的點往源極移動,此時電子注入空間電荷區,在藉由電場掃至汲極。 • 當VDS > VDS(sat),p點的電壓仍為VDS(sat),故ID維持不變。