FPGA Multi-core

FPGA Multi-core. The Project. Definition Asymmetric FPGA-loaded hardware accelerators for FPGA-enhanced CPU systems with Linux. Performed by: Avi Werner William Backshi Instructor: Evgeny Fiksman Cooperated with: IBM Dror Livne (head of SW Dpt, start-up). The Process.

FPGA Multi-core

E N D

Presentation Transcript

FPGA Multi-core

The Project Definition Asymmetric FPGA-loaded hardware accelerators for FPGA-enhanced CPU systems with Linux Performed by: Avi Werner William Backshi Instructor: Evgeny Fiksman Cooperated with: IBM Dror Livne (head of SW Dpt, start-up).

The Process • Studying the environment • Build fully functional cross-compilation toolchain for PPC • Implementation of one of the board+CPU+OS demos on FPGA • Introduce additional hardware into FPGA, test liveness. • Multi-core • Study existing buses; build FSB for the Accelerator core • Compile and test simple SW function for the Accelerator core • Insert CPU cache for Accelerator core • Insert test simple SW function to Accelerator cache, test functionality • Design Accelerators interface, memory and controllers • Design SW stub for the Accelerators to work in passive mode • Add several Accelerators, test existing functionality • Write OS support driver that allows sending code to Accelerators for execution • Write a test bench • FPGA dynamic loading • Test FPGA dynamic loading with Xilinx software • Test dynamic loading of a simple Accelerator • Write OS support driver for FPGA-on-the-fly functions • Test loading custom precompiled VHDL code (“hardware DLL”) on-the-fly

The Process • Studying the environment • Build fully functional cross-compilation toolchain for PPC • Implementation of one of the board+CPU+OS demos on FPGA • Introduce additional hardware into FPGA, test liveness. Duration: up to 1 month Status: almost complete

The Process • Multi-core • Study existing buses; build FSB for the Accelerator core • Compile and test simple SW function for the Accelerator core • Insert CPU cache for Accelerator core • Insert test simple SW function to Accelerator cache, test functionality • Design Accelerators interface, memory and controllers • Design SW stub for the Accelerators to work in passive mode • Add several Accelerators, test existing functionality • Write OS support driver that allows sending code to Accelerators for execution • Write a test bench Duration: up to 6 months

The Process • FPGA dynamic loading • Test FPGA dynamic loading with Xilinx software • Test dynamic loading of a simple Accelerator • Write OS support driver for FPGA-on-the-fly functions • Test loading custom precompiled VHDL code (“hardware DLL”) on-the-fly Duration: up to 3 months (Given success of previous parts’ schedule)

Project progress • Theoretical research • Found and read articles on HW accelerators, both of the faculty staff and external (CELL – IBM, etc) • Met with most of MATRICS group, checking their interest in our platform and possible demands • Met with Systems Dpt. Members in IBM (Muli Ben-Yehuda) for a concept review. • System architecture has undergone significant changes. • Practical achievements • Cross-compiler toolchain (GCC 4.1)Stack overflow protection of PPC-64 (reported in the GCC by BugZilla) presented a significant workload to avoid. • Compiled kernel for PPC-405 with ML310 support (no PCI support). • Booted ML310 from CF with Xilinx pre-loaded Linux. • Remaining • Boot ML310 with our kernel. • Introduce additional hardware into FPGA, test liveness.

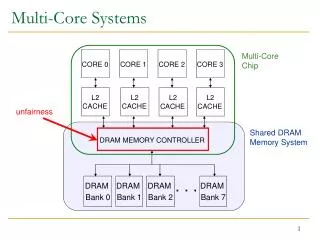

Project progress • Platform • ML310 with PPC405 • Accelerators • Not chosen yet – thus no detailed schemes available at the moment. • Controllers • Accelerator-dependent, will be defined after accelerator selection and basic functionality tests.

HW Block Schematics MMU DDR MEM Accelerator Arbiter MEM PPC Accelerator Accelerator Accelerator Memory controller

System Block Schematics Linux (Debian) DDR MEM Driver Virtual communication Layer (SW) MMU Accelerated Software platform FPGA Accelerator Arbiter Shared MEM PPC 405 Accelerator Accelerator Accelerator Memory controller