Understanding Array Types and Subprograms in VHDL

Explore the attributes of arrays and array types, learn about predefined and user-defined array types, and delve into subprograms in VHDL for FPGA and ASIC design. Discover functions, procedures, and package usage.

Understanding Array Types and Subprograms in VHDL

E N D

Presentation Transcript

ECE 448 Lecture 14 Subprograms Attributes of Arrays & Array Types ECE 448 – FPGA and ASIC Design with VHDL

Unconstrained Array Types ECE 448 – FPGA and ASIC Design with VHDL

Predefined Unconstrained Array Types Predefined bit_vector array of bits string array of characters Defined in the ieee.std_logic_1164 package: std_logic_vector array of std_logic_vectors ECE 448 – FPGA and ASIC Design with VHDL

Predefined Unconstrained Array Types subtype byte is bit_vector(7 downto 0); …. variable channel_busy : bit_vector(1 to 4); …. constant ready_message :string := “ready”; …. signal memory_bus: std_logic_vector (31 downto 0); ECE 448 – FPGA and ASIC Design with VHDL

User-defined Unconstrained Array Types type sample is array (natural range <>) of integer; …. variable long_sample is sample(0 to 255); …. constant look_up_table_1: sample := (127, -45, 63, 23, 76); …. ECE 448 – FPGA and ASIC Design with VHDL

Attributes of Arrays and Array Types ECE 448 – FPGA and ASIC Design with VHDL

Array Attributes A’left(N) left bound of index range of dimension N of A A’right(N) right bound of index range of dimension N of A A’low(N) lower bound of index range of dimension N of A A’high(N) upper bound of index range of dimension N of A A’range(N) index range of dimension N of A A’reverse_range(N) index range of dimension N of A A’length(N) length of index range of dimension N of A A’ascending(N)true if index range of dimension N of A is an ascending range, false otherwise ECE 448 – FPGA and ASIC Design with VHDL

Array Attributes - Examples type A is array (1 to 4, 31 downto 0); A’left(1) = 1 A’right(2) = 0 A’low(1) = 1 A’high(2) = 31 A’range(1) = 1 to 4 A’length(2) = 32 A’ascending(2) = false ECE 448 – FPGA and ASIC Design with VHDL

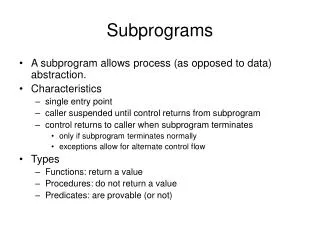

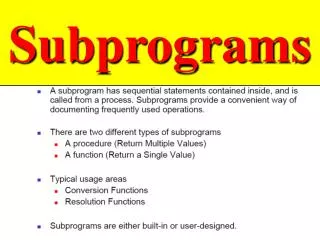

Subprograms ECE 448 – FPGA and ASIC Design with VHDL

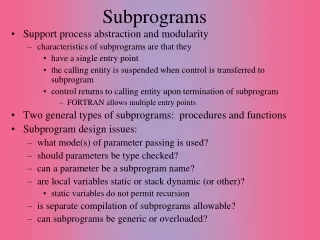

Subprograms • Include functions and procedures • Commonly used pieces of code • Can be placed in a library, and then reused and shared among various projects • Abstract operations that are repeatedly performed • Type conversions • Use only sequential statements, the same as processes ECE 448 – FPGA and ASIC Design with VHDL

Typical locations of subprograms PACKAGE PACKAGE BODY LIBRARY global ENTITY FUNCTION / PROCEDURE local for all architectures of a given entity ARCHITECTURE Declarative part local for a given architecture ECE 448 – FPGA and ASIC Design with VHDL

Functions ECE 448 – FPGA and ASIC Design with VHDL

Functions – basic features Functions • always return a single value as a result • are called using formal and actual parametersthe same way as components • never modify parameters passed to them • parameters can only be constants (including generics) and signals (including ports); variables are not allowed; the default is a CONSTANT • when passing parameters, no range specification should be included (for example no RANGE for INTEGERS, or TO/DOWNTO for STD_LOGIC_VECTOR) • are always used in some expression, and not called on their own ECE 448 – FPGA and ASIC Design with VHDL

Function syntax FUNCTION function_name (<parameter_list>) RETURN data_type IS [declarations] BEGIN (sequential statements) END function_name; ECE 448 – FPGA and ASIC Design with VHDL

Function parameters - example FUNCTION f1 (a, b: INTEGER; SIGNAL c: STD_LOGIC_VECTOR) RETURN BOOLEAN IS BEGIN (sequantial statements) END f1; ECE 448 – FPGA and ASIC Design with VHDL

Function calls - examples x <= conv_integer(a); IF x > maximum(a, b) THEN .... WHILE minimum(a, b) LOOP ....... ECE 448 – FPGA and ASIC Design with VHDL

Function – example (1) library IEEE; use IEEE.std_logic_1164.all; ENTITY powerOfFour IS PORT( X : IN INTEGER; Y : OUT INTEGER; ); END powerOfFour; ECE 448 – FPGA and ASIC Design with VHDL

Function – example (2) ARCHITECTURE behavioral OF powerOfFour IS FUNCTION Pow ( SIGNAL N:INTEGER; Exp : INTEGER) RETURNINTEGERIS VARIABLE Result : INTEGER := 1; BEGIN FOR i IN 1 TO Exp LOOP Result := Result * N; END LOOP; RETURN( Result ); END Pow; BEGIN Y <= Pow(X, 4); END behavioral; ECE 448 – FPGA and ASIC Design with VHDL

Package containing a function (1) LIBRARY IEEE; USE IEEE.std_logic_1164.all; PACKAGE specialFunctions IS FUNCTION Pow( SIGNAL N: INTEGER; Exp : INTEGER) RETURNINTEGER; END specialFunctions ECE 448 – FPGA and ASIC Design with VHDL

Package containing a function (2) PACKAGE BODY specialFunctions IS FUNCTION Pow(SIGNAL N: INTEGER; Exp : INTEGER) RETURNINTEGERIS VARIABLE Result : INTEGER := 1; BEGIN FOR i IN 1 TO Exp LOOP Result := Result * N; END LOOP; RETURN( Result ); END Pow; END specialFunctions ECE 448 – FPGA and ASIC Design with VHDL

Type conversion function (1) LIBRARY ieee; USE ieee.std_logic_1164.all; ------------------------------------------------------------------------------------------------- PACKAGE my_package IS FUNCTION conv_integer (SIGNAL vector: STD_LOGIC_VECTOR) RETURN INTEGER; END my_package; ------------------------------------------------------------------------------------------------- ECE 448 – FPGA and ASIC Design with VHDL

Type conversion function (2) PACKAGE BODY my_package IS FUNCTION conv_integer (SIGNAL vector: STD_LOGIC_VECTOR) RETURN INTEGER; VARIABLE result: INTEGER RANGE 0 TO 2**vector’LENGTH - 1; VARIABLE carry: STD_LOGIC; BEGIN IF(vector(vector’HIGH)=‘1’ THEN result:=1; ELSE result := 0; FOR i IN (vector’HIGH-1) DOWNTO (vector’LOW) LOOP result := result*2; IF (vector(i) = ‘1’ THEN result := result+1; END IF; RETURN result; END conv_integer; END my_package; ECE 448 – FPGA and ASIC Design with VHDL

Type conversion function (3) LIBRARY ieee; USE ieee.std_logic_1164.all; USE work.my_package.all; ------------------------------------------------------------------------------------------------- ENTITY conv_int2 IS PORT ( a: IN STD_LOGIC_VECTOR (0 TO 3); y: OUT INTEGER RANGE 0 TO 15); END conv_int2; ------------------------------------------------------------------------------------------------- ARCHITECTURE my_arch OF conv_int2 IS BEGIN y <= conv_integer(a); END my_arch; ECE 448 – FPGA and ASIC Design with VHDL

Procedures ECE 448 – FPGA and ASIC Design with VHDL

Procedures – basic features Procedures • do not return a value • are called using formal and actual parametersthe same way as components • may modify parameters passed to them • each parameter must have a mode: IN, OUT, INOUT • parameters can be constants (including generics), signals (including ports), and variables;the default for inputs (mode in) is a constant, the default for outputs (modes out and inout) is a variable • when passing parameters, range specification should be included (for example RANGE for INTEGERS, and TO/DOWNTO for STD_LOGIC_VECTOR) • Procedure calls are statements on their own ECE 448 – FPGA and ASIC Design with VHDL

Procedure syntax PROCEDURE procedure_name (<parameter_list>) IS [declarations] BEGIN (sequential statements) END function_name; ECE 448 – FPGA and ASIC Design with VHDL

Procedure parameters - example PROCEDURE my_procedure ( a: IN BIT; SIGNAL b, c: IN BIT; SIGNAL x: OUT BIT_VECTOR(7 DOWNTO 0); SIGNAL y: INOUT INTEGER RANGE 0 TO 99) IS BEGIN (sequantial statements) END my_procedure; ECE 448 – FPGA and ASIC Design with VHDL

Procedure calls - examples compute_min_max(in1, in2, in3, out1, out2); divide(dividend, divisor, quotient, remainder); IF (a > b) THEN compute_min_max(in1, in2, in3, out1, out2); ....... ECE 448 – FPGA and ASIC Design with VHDL

Procedure – example (1) LIBRARYieee; USEieee.std_logic_1164.all; ENTITYmin_maxIS GENERIC (limit: INTEGER := 255); PORT ( ena : IN BIT; inp1, inp2:ININTEGER RANGE 0 TO limit; min_out, max_out:OUTINTEGER RANGE 0 TO limit); ); ENDmin_max; ECE 448 – FPGA and ASIC Design with VHDL

Procedure – example (2) ARCHITECTUREmy_architectureOF min_maxIS PROCEDUREsort (SIGNAL in1, in2: IN INTEGER RANGE 0 TO limit; SIGNAL min, max: OUT INTEGER RANGE 0 TO limit) IS BEGIN IF (in1 > in2) THEN max <= in1; min <= in2; ELSE max <= in2; min <= in1; END IF; END sort; BEGIN PROCESS (ena) BEGIN IF(ena=‘1’) THEN sort (inp1, inp2, min_out, max_out); END IF; END PROCESS; END my_architecture; ECE 448 – FPGA and ASIC Design with VHDL

Operators ECE 448 – FPGA and ASIC Design with VHDL

Operator as a function (1) LIBRARY ieee; USE ieee.std_logic_1164.al; ------------------------------------------------------------------------------------------------- PACKAGE my_package IS FUNCTION "+" (a, b: STD_LOGIC_VECTOR) RETURN STD_LOGIC_VECTOR; END my_package; ------------------------------------------------------------------------------------------------- ECE 448 – FPGA and ASIC Design with VHDL

Operator as a function (2) PACKAGE BODY my_package IS FUNCTION "+" (a, b: STD_LOGIC_VECTOR) RETURN STD_LOGIC_VECTOR; VARIABLE result: STD_LOGIC_VECTOR; VARIABLE carry: STD_LOGIC; BEGIN carry := ‘0’; FOR i IN a’REVERSE_RANGE LOOP result(i) := a(i) XOR b(i) XOR carry; carry := (a(i) AND b(i)) OR (a(i) AND carry) OR (b(i) AND carry)); END LOOP; RETURN result; END "+" ; END my_package; ECE 448 – FPGA and ASIC Design with VHDL

Operator Overloading ECE 448 – FPGA and ASIC Design with VHDL

Operator overloading • Operator overloading allows different argument types for a given operation (function) • The VHDL tools resolve which of these functions to select based on the types of the inputs • This selection is transparent to the user as long as the function has been defined for the given argument types. ECE 448 – FPGA and ASIC Design with VHDL

Different declarations for the same operator - Example Declarations in the package ieee.std_logic_unsigned: function “+” ( L: std_logic_vector; R:std_logic_vector) return std_logic_vector; function “+” ( L: std_logic_vector; R: integer) return std_logic_vector; function “+” ( L: std_logic_vector; R:std_logic) return std_logic_vector; ECE 448 – FPGA and ASIC Design with VHDL

Different declarations for the same operator - Example signal count: std_logic_vector(7 downto 0); You can use: count <= count + “0000_0001”; or count <= count + 1; or count <= count + ‘1’; ECE 448 – FPGA and ASIC Design with VHDL