CSI 312- Computer Organization

600 likes | 622 Views

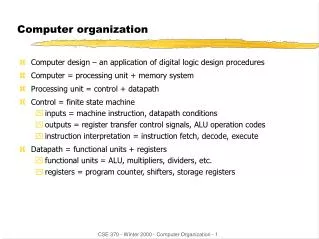

CSI 312- Computer Organization. ORACLE Arithmetic Unit Image Source: Oak Ridge National Laboratory. Lecture 6 - Logic & Arithmetic 2011 Homework: p: 229: 3.1, 3.2, 3.3, 3.4, 3.5, 3.6 p: 231: 3.27. Roadmap for the Term: Major Topics. Computer Systems Overview Technology Trends

CSI 312- Computer Organization

E N D

Presentation Transcript

CSI 312- Computer Organization ORACLE Arithmetic Unit Image Source: Oak Ridge National Laboratory Lecture 6 - Logic & Arithmetic2011 Homework: p: 229: 3.1, 3.2, 3.3, 3.4, 3.5, 3.6 p: 231: 3.27

Roadmap for the Term: Major Topics • Computer Systems Overview • Technology Trends • Instruction Sets (and Software) • Logic and Arithmetic 3 • Performance • Processor Implementation • Memory Systems • Input/Output Lecture 6 - Logic & Arithmetic

Arithmetic & Logic Unit • Perform the calculations • Everything else in the computer is there to serve this unit • Handles integers • May handle floating point numbers • May be separate (math co-processor)

Outline - Logic & Arithmetic • Review: Numbers & Arithmetic 3 • Positional Number Systems • Signed Number Representation • Review: Addition & Subtraction • ALU Design Lecture 6 - Logic & Arithmetic

Review: Positional Notation of Numbers • Example: Binary (base 2) numbers • Base = 2 • Digits = {0,1} Note “bit” == “Binary digit” • N = 1001two = 1X20 + 0X21 + 0X22 + 1X23 = 1ten + 8ten = 9ten • Example: Hexadecimal (base 16) numbers • Base = 16 • Digits = {0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F} • N = 1A3Fhex = 15X160 + 3X161 + 10X162 + 1X163 = 15ten + 48ten + 2560ten + 4096ten = 6719ten = 0001101000111111two Lecture 6 - Logic & Arithmetic

Range of Unsigned Binary Numbers Lecture 6 - Logic & Arithmetic

Review: Unsigned vs. Signed Numbers • Basic binary - allows representation of non-negative numbers only In C, Java, etc:unsigned int x;Useful for unsigned quantities like addresses • Most of us need negative numbers, too! In C, Java, etc:int x;How can we do this? … Use a signed representation Lecture 6 - Logic & Arithmetic

Sign/Magnitude Two’s Complement - the one almost everyone uses One’s Complement Biased - used for exponent sign in Floating Point Signed Number Representations Lecture 6 - Logic & Arithmetic

1 0 0 1 1 0 0 1 Magnitude Sign Sign/Magnitude Representation • Approach: Use binary number and added sign bit • Problems: • Two values of zero • Difficult to implement in hardware - consider addition • Must first check signs of operands • Then compute value • Then compute sign of result = -25 Lecture 6 - Logic & Arithmetic

Two’s Complement Representation • Goal: make the hardware easy to design • Approach: explicitly represent result of “borrow” in subtract • Borrow results in “leading 1’s” • Weight leftmost “sign bit” with -2n-1 • Use sign bit to represent “last borrow” N = 1111tc = 1X20 + 1X21 + 1X22 + 1X-23 = 7ten + -8ten = -1ten N = 1001tc = 1X20 + 0X21 + 0X22 + 1X-23 = 1ten + -8ten = -7ten N = 0101tc = 1X20 + 0X21 + 1X22 + 0X-23 = 1ten + 4ten = 5ten • All negative numbers have a “1” in the sign bit • Single representation of zero Lecture 6 - Logic & Arithmetic

Range of Two’s Complement Numbers Lecture 6 - Logic & Arithmetic

Negating Two’s Complement Numbers • Important shortcut • Invert the individual bits • Add 1 • Result: two’s complement representation of negated number! • Examples (with 4 bits): - (0111) = 1000+1 = 1001 -7 - (1100) = 0011+1 = 0100 +4 - (1111) = 0000+1 = 0001 +1 Lecture 6 - Logic & Arithmetic

Other Signed Binary Representations • One’s Complement • Use one’s complement (inverted bits) to represent negated numbers +1 = 0001 -1 = Invert(0001) = 1110 • Problem: two values of zero (0000, 1111) Lecture 6 - Logic & Arithmetic

Orignal byte: -6 11111010 Result word: -6 111111111111111111111111 11111010 Orignal byte: 45 00101011 Result word: 45 000000000000000000000000 00101011 Sign Extension • To convert a “narrower” signed number to a “wider” one: • Copy the bits of the narrower number into the lower bits • Copy the sign bit from the narrower number into all of the remaining bits of the result • Example: Converting signed 8-bit byte to 32-bit word: Lecture 6 - Logic & Arithmetic

Orignal byte: 45 00101011 zeros Result word: 45 000000000000000000000000 00101011 zeros Orignal byte: 193 11000001 Result word: 193 000000000000000000000000 11000001 Zero-Padding - for unsigned numbers • To convert a “narrower” unsigned number to a “wider” one • Copy the bits of the narrower number into the lower bits • Copy “zeros” into upper bits of wider number Lecture 6 - Logic & Arithmetic

Sign Extension in MIPS • Load-byte (lb) instruction • Loads an 8-bit signed number from memory • Performs sign extension before placing in 32-bit register • Load-byte unsigned (lbu) • Loads an 8-bit unsigned number (e.g., ASCII character) from memory • No sign extension - places byte with leading “0’s” in 32-bit register Lecture 6 - Logic & Arithmetic

Sign Extension in MIPS I-Format Instructions • I-Format Instructions have 16-bit immediate field • MIPS operations are defined on 32-bit registers • Sign extension performed on immediate operands “when it makes sense” • Sign extension used for addi, beq, bne, ... • Zero-padding used for andi, ori, ... Lecture 6 - Logic & Arithmetic

Outline - Logic & Arithmetic • Review: Numbers & Arithmetic • Positional Number Systems • Signed Number Representation • Review: Addition & Subtraction 3 • Carry Lookahead: Making Addition Fast • ALU Design • Shifters • Summary Lecture 6 - Logic & Arithmetic

Ai Bi Ci Ci+1 Si 0 0 0 0 0 0 0 0 1 1 Ai Bi 0 0 1 0 1 Ci Ci+1 1 0 1 1 0 Si 0 1 0 0 1 1 1 0 1 0 1 1 1 0 0 1 1 1 1 1 Review: Binary Addition • Key building block: Full Adder Result of Xor: 1 if 2 bits are different 0 if 2 bits are the same Lecture 6 - Logic & Arithmetic

Binary Arithmetic • Add up to 3 bits at a time per place value • A and B • “carry in” • Output 2 bits at a time • sum bit for that place value • “carry out” bit (becomes carry-in of next bit) • Can be done using a function with 3 inputs, 2 outputs carry-in bits 1 1 1 0 0 A bits 1 1 1 0 B bits + 0 1 1 1 sum bits 0 1 0 1 carry-out bits 1 1 1 1 0 B A FA carry out carry in sum

A3 B3 A2 B2 A1 B1 A0 B0 C3 C2 C1 C0 0 C4 C3 C2 C1 S3 S2 S1 S0 Multiple-Bit Adders • String together Full Adders to form a Ripple Adder Lecture 6 - Logic & Arithmetic

A3 B3 A2 B2 A1 B1 A0 B0 C3 C2 C1 C0 C4 C3 C2 C1 S3 S2 S1 S0 How to Subtract with an Adder • Recall • Definition of subtraction: A-B = A + (-B) • Two’s Complement Negation Shortcut • -B = bit_invert(B)+1 1 Lecture 6 - Logic & Arithmetic

A3 B3 A2 B2 A1 B1 A0 B0 C3 C2 C1 C0 C4 C3 C2 C1 S3 S2 S1 S0 Designing an Adder/Subtractor • Recall • Definition of subtraction: A-B = A + (-B) • Two’s Complement Negation Shortcut • -B = bit_invert(B)+1 Control Add/Sub 0 to add 1 to subtract Result of Xor: 1 if 2 bits are different 0 if 2 bits are the same Lecture 6 - Logic & Arithmetic

Operation Operand A Operand B Result A + B ≥ 0 ≥ 0 < 0 A + B < 0 < 0 ≥ 0 A - B ≥ 0 < 0 < 0 A - B < 0 ≥ 0 ≥ 0 Overflow in addition & subtraction • Overflow - occurs when not enough bits are available to represent the result • Example: unsigned 32-bit result ≥ 232 • Example: signed 32-bit result < -231 or ≥ 231 • Detecting overflow - look for different signs in operands vs. result: Lecture 6 - Logic & Arithmetic

What to do when overflow occurs? • In some languages (e.g., C, Java) - nothing (“responsibility left to the programmer”) • In other languages (e.g. Ada, Fortran) - “notify programmer” through runtime exception • How MIPS handles overflow: • add, sub, addi - runtime exception on overflow • addu, subu, addiu - no runtime exception on overflow Lecture 6 - Logic & Arithmetic

Outline - Logic & Arithmetic • Review: Numbers & Arithmetic • Positional Number Systems • Signed Number Representation • Review: Addition & Subtraction • Carry Lookahead: Making Addition Fast • ALU Design 3 • Shifters • Summary Lecture 6 - Logic & Arithmetic

A F(A,B) ALU B Operation Select Arithmetic-Logic Units • Combinational logic element that performs multiple functions: • Arithmetic: add, subtract • Logical: AND, OR Lecture 6 - Logic & Arithmetic

Constructing an ALU - First Cut • Construct in bit slices, like the ripple adder • Add gates, multiplexer for logic functions, subtract Lecture 6 - Logic & Arithmetic

ALU Operation ALU control input Function 000 AND A 001 OR Zero 010 add Result ALU 110 subtract Overflow B 111 set on less than CarryOut Final Result: ALU Function Lecture 6 - Logic & Arithmetic

Outline - Multiplication and Division • Multiplication • Review: Shift & Add Multiplication 3 • Review: Booth’s Algorithm • Combinational Multiplication • MIPS Multiplication Instructions • Division • Summary Lecture 8 - Mult. & Division

Partial Products Multiplication • Basic algorithm analogous to decimal multiplication • Break multiplier into digits • Multiply one digit at a time; shift multiplicand to form partial products • Create product as sum of partial products • n bit multiplicand X m bit multiplier = (n+m) bit product Multiplicand 0110 (6) Multiplier X 0011 (3) 0110 0110 0000 0000 Product 00010010 (18) Lecture 8 - Mult. & Division

Multiplier Hardware • Sequential • Combinational Lecture 8 - Mult. & Division

Multiplicand shifts left Multiplier shifts right Sample LSB of multiplier to decide whether to add Multiplicand (64 bits) Product (64 bits) Multiplier (32 bits) Shift Left Write Shift Right LSB 64-bit ALU Control Sequential Multiplier - First Version Lecture 8 - Mult. & Division

START 1. TestMPY0 Multiplier0=1 Multiplier0=0 1a. Add MCND to PRODPlace result in PROD 2. Shift MCND left 1 bit 2. Shift MPY right 1 bit 32ndRepitition? DONE Algorithm - 1st Cut Multiplier Lecture 8 - Mult. & Division

Multiplicand Multiplicand Multiplicand Multiplicand Multiplier Product (64 bits) Write LSB 64-bit ALU Control Animation - 1st Cut Multiplier • Multiplicand shifts left • Multiplier shifts right • Sample LSB of multiplier to decide whether to add Multiplicand Lecture 8 - Mult. & Division

Multiplicand (32 bits) Multiplier (32 bits) Shift Right LSB 32-bit ALU Control Shift Right Product(64 bits) Write Sequential Multiplier - 2nd Version • Observation: we’re only adding 32 bits at a time • Clever idea: Why not... • Hold the multiplicand still and… • Shift the product right! LHPROD (32 bits) RHPROD(32 bits) Lecture 8 - Mult. & Division

START 1. TestMPY0 Multiplier0=1 Multiplier0=0 1a. Add MCND to left half of PRODPlace result in left half of PROD 2. Shift PRODright 1 bit 2. Shift MPY right 1 bit 32ndRepitition? No: <32 Repititions Yes: 32 Repititions DONE Algorithm - 2nd Version Multiplier Lecture 8 - Mult. & Division

Multiplicand (32 bits) 32-bit ALU Control Shift Right Product(64 bits) Write LSB Sequential Multiplier - 3nd Version • Observation: we can store the multiplier and product in the same register! • As multiplier shifts out…. • Product shifts in MP/RHPROD(32 bits) LHPROD (32 bits) MPY (initial)(32 bits) Lecture 8 - Mult. & Division

START 0. LOAD MPY in right half of PROD 1. TestPROD0 Product0=1 Product0=0 1a. Add MCND to left half of PRODPlace result in left half of PROD 2. Shift PRODright 1 bit 32ndRepitition? No: <32 Repititions Yes: 32 Repititions DONE Algorithm - 3rd Version Multiplier Lecture 8 - Mult. & Division

Outline - Multiplication and Division • Multiplication • Review: Shift & Add Multiplication • Review: Booth’s Algorithm 3 • MIPS Multiplication Instructions • Division • Summary Lecture 8 - Mult. & Division

Signed Multiplication with Booth’s Algorithm • Originally proposed to reduce addition steps • Bonus: works for two’s complement numbers • Multiply negative numbers • Uses shifting, addition, and subtraction Lecture 8 - Mult. & Division

Booth’s Algorithm • Observation: if we can both add and subtract, there are multiple ways to create a product • Example: multiply 2ten by 6ten (0010two X 0110two) • Product = (2 X 2) + (2 X 4) OR • Product = (2 X -2) + (2 X 8) Regular Algorithm Booth’s Algorithm 0010 X 0110 + 0000 shift + 0010 shift + add + 0010 shift + add + 0000 shift 00001100 0010 X 0110 0000 shift - 0010 shift + subtract 0000 shift + 0010 shift + add 00001100 Lecture 8 - Mult. & Division

Booth’s Algorithm Continued • Question: • How do we know when to subtract? • When do we know when to add? • Answer: look for “runs of 1s” in multiplier • Example: 001110011 • Working from Right to Left, any “run of 1’s” is equal to: - value of first digit that’s one +value of first digit that’s zero • Example : 001110011 • First run: -1 + 4 = 3 • Second run: -16 + 128 = 112 • Total: 112 + 3 = 115 Lecture 8 - Mult. & Division

0 1 1 0 0 1 1 1 0 0 End Of Run Middle Of Run Beginning Of Run Bit ai Bit ai-1 Explanation 1 0 Begin Run of 1’s 1 1 Middle of Run of 1’s 0 1 End of Run 0 0 Middle of Run of 0’s Implementing Booth’s Algorithm • Scan multiplier bits from right to left • Recognize the beginning and in of a run looking at only 2 bits at a time • “Current” bit ai • Bit to right of “current” bit ai-1 Lecture 8 - Mult. & Division

Multiplicand (32 bits) ADD/SUB 32-bit ALU Control Shift Left Product(64 bits) LHPROD (32 bits) MP/RHPROD(32 bits) Write Bits 1:0 2 Implementing Booth’s Algorithm • Key idea: test 2 bits of multiplier at once • 10 - subtract (beginning of run of 1’s) • 01 - add (end of run of 1’s) • 00, 11 - do nothing (middle of run of 0’s or 1’s) Lecture 8 - Mult. & Division

Outline - Multiplication and Division • Multiplication • Review: Shift & Add Multiplication • Review: Booth’s Algorithm • MIPS Multiplication Instructions 3 • Division • Summary Lecture 8 - Mult. & Division

Multiply Instructions in MIPS • MIPS adds new registers for product result: • Hi - upper 32 bits of product • Lo - lower 32 bits of product • MIPS multiply instructions • mult $s0, $s1 • multu $s0, $s1 • Accessing Hi, Lo registers • mfhi $s1 • mflo $s1 Lecture 8 - Mult. & Division

Outline - Multiplication and Division • Multiplication • Review: Shift & Add Multiplication • Review: Booth’s Algorithm • Combinational Multiplication • MIPS Multiplication Instructions • Division • Division Algorithms 3 • MIPS Division Instructions • Summary Lecture 8 - Mult. & Division

Division Overview • Grammar school algorithm: long division • Subtract shifted divisor from dividend when it “fits” • Quotient bit: 1 or 0 • Question: how can hardware tell “when it fits?” 1 0 0 1 Quotient Divisor 1000 1001010 Dividend -1000 1010 -1000 10 Remainder Dividend = Quotient X Divisor + Remainder Lecture 8 - Mult. & Division