CPU power consumption

CPU power consumption. CPU power consumption. Most modern CPUs are designed with power consumption in mind to some degree Power vs. energy: Power P = I avg X V cc (watt), 1w = 1J/s The rate at which energy is consumed Energy 1 Joule = 1W X 1s Heat-Limited application (HLA):

CPU power consumption

E N D

Presentation Transcript

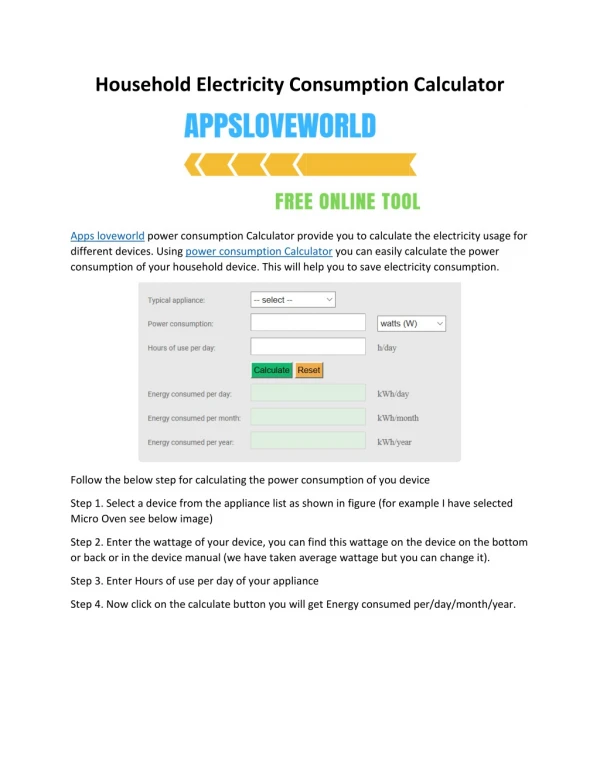

CPU power consumption • Most modern CPUs are designed with power consumption in mind to some degree • Power vs. energy: • Power • P = Iavg X Vcc (watt), 1w = 1J/s • The rate at which energy is consumed • Energy • 1 Joule = 1W X 1s • Heat-Limited application (HLA): • cost of power supply • cost of cooling • heat depends on power consumption • 600 MHz Alpha: 109.0 W @ 2.30V Vdd • Energy-Limited application (ELA): • battery life depends on energy consumption (mobile system) • cooling

Notebook Power Breakdown • IBM ThinkPad R40 • 1.3 GHz Pentium M

CPU Power Breakdown by unit Breakdown of Power for Modern High Performance Processor Pentium Pro Breakdown of Power

Power reduction techniques • Transistor Level • static power consumption • dynamic power consumption • leakage current • Circuit Level • Voltage scaling • Clock gating • System Level • Power saving modes • Cache organization • Software Based • Instruction level power analysis

CMOS power consumption • Voltage drops: power consumption proportional to V2: • Ps=CLVdd2fs • Toggling (switching): more activity means more power • Leakage: basic circuit characteristics; can be eliminated by disconnecting power (below 0.13 micron)

CPU power-saving strategies • Reduce power supply voltage • noise margin • leakage current • Run at lower clock frequency • Performance • Disable functionunits with control signals when not in use • Disconnect parts from power supply when not in use

Application: PowerPC 603 energy features • Provides doze, nap, sleep modes • Dynamic power management features: • Uses static logic • Can shut down unused execution units • Cache organized into subarrays to minimize amount of active circuitry

PowerPC 603 activity • Percentage of time units are idle for SPEC integer/floating-point: unit Specint92 Specfp92 D cache 29% 28% I cache 29% 17% load/store 35% 17% fixed-point 38% 76% floating-point 99% 30% system register 89% 97%

Power-down costs • Going into a power-down mode costs: • time • energy • Must determine if going into mode is worthwhile • Can model CPU power states with power state machine

Power vs. time running a real application • Pentium processor

Application: StrongARM SA-1100 power saving • Processor takes two supplies: • VDD is main 3.3V supply • VDDX is 1.5V • Three power modes: • Run: normal operation • Idle: stops CPU clock, with logic still powered • Sleep: shuts off most of chip activity;

SA-1100 power state machine Prun = 400 mW run 10 ms 160 ms 90 ms 10 ms 90 ms idle sleep Pidle = 50 mW Psleep = 0.16 mW

Intel PXA27x Power Management • Power Modes • Turbo mode • Run mode – normal full-function mode • Idle mode – stopping the CPU clock • Deep-idle mode – back to 13-MHz core frequency • Standby mode • Sleep mode – keeps I/O powered • Deep-sleep mode – I/O powered down

DFM and DVM (2) • DFM • The core clock can be configured dynamically by SW • DVM • The voltage manager provides voltage management through use of an I2C unit • Coupling • A frequency change can be coupled with a voltage change • A voltage change can be coupled with a frequency change

DFM and DVM (3) • Programmable Operating Frequencies

Workload Characterization for Intel DFM and DVM • CPU bound • Memory bound • I/O bound • CPU and Memory bound • CPU bound job

Workload Characterization for Intel DFM and DVM Memory bound job CPU and Memory bound job Window Media Video

Power management styles • Static power management: does not depend on CPU activity • Example: user-activated power-down mode • Dynamic power management: based on CPU activity • Example: disabling off function units

Power optimization • Power management: determining how system resources are scheduled/used to control power consumption • Static : does not depend on CPU activity • Example: user-activated power-down mode • Dynamic : based on CPU activity • Example: disabling off function units • OS can manage for power just as it manages for time. • OS reduces power by shutting down units. • May have partial shutdown modes.

Power management and performance • Power management and performance are often at odds. • Entering power-down mode consumes • energy • time • Leaving power-down mode consumes • energy • time

Simple power management policies • Request-driven: power up once request is received. Adds delay to response. • Predictive shutdown: try to predict how long you have before next request. • May start up in advance of request in anticipation of a new request. • If you predict wrong, you will incur additional delay while starting up.

Probabilistic shutdown • Assume service requests are probabilistic. • Optimize expected values: • power consumption • response time • Simple probabilistic: shut down after time Ton, turn back on after waiting for Toff.

Advanced Configuration and Power Interface • Conceived by Intel, Microsoft, and Toshiba (the promoters) • An “interface” specification • ACPI/OSPM replaces APM, MPS, and PnP BIOS Spec • APM : advanced power management (1992) • to reduce power consumption below the 60 to 80 watts requirement of DOS-based systems • BIOS-driven power management • Allow OS-directed Power Management (OSPM) • power management specification • system design specification • application program power management specification

ACPI, cont’d • Defines • Hardware registers - implemented in chipset silicon • BIOS interfaces • Configuration tables • Interpreted executable function interface (Control Methods) • Motherboard device enumeration and configuration • System and device power states • ACPI Thermal Model

Advanced Configuration and Power Interface • ACPI: open standard for power management services. applications device drivers OS kernel power management ACPI BIOS Hardware platform

ACPI global power states • G3: mechanical off • G2(S5): soft off • G1: sleeping state • S1: low wake-up latency with no loss of context • S2: low latency with loss of CPU/cache state • S3: low latency with loss of all state except memory • S4: lowest-power state with all devices off • G0: working state

Software Power Minimization • SW constitutes a major component of systems • Instruction level power analysis • Instruction base costs • Effect of circuit state • Other inter-instruction effects • Pipeline stalls • Cache misses “Reducing power in high-performance microprocessors,” V. Tiwari et al. “Instruction level power analysis and optimization of software,” V. Tiwari et al.

Instruction base costs • 486DX2: 300-500 mA • SPARClite: 200-300 mA • DSP : 20-60 mA

Effect of circuit state • Case of the 486DX2 • 5-30 mA while most instructions in the range of 300-420 mA • Case of a smaller, more basic processor (DSP)

Other Inter-instruction effects • Case of the 486 DX2 • Pipeline stall cycle • 250 mA • Cache miss cycle • 216 mA

Overall Instruction level power model Ep =Si(Bi x Ni) +Si,j(Oi,j x Ni,j) + SkEk • Impact of internal power management • OR, SHIFT, ADD, or MULTIPLY do not show much of the cost variation • Guarded evaluation • Turn off the power of the unused modules dynamically • Low power Pentium, PowerPC 603, etc.

Software Energy Optimization Techniques • Reducing Memory Accesses • 486 DX : • Register operand: 300 mA • Memory read: 400 mA

Software Energy Optimization Techniques, cont’d • Energy cost driven code generation • Traditional cost criteria • Either the size or the running time • Instruction Reordering for Low power • Limited impact in 486DX and the SPARClite • Beneficial for the DSP (Why?) • Processor specific optimizations