TLC 的设计

TLC 的设计 设计在 FR (Farmroad 缩写为 FR (BR)) 与 HW (Highway 缩写为 HW (MR)) 十字交叉口的 TLC (TLC--Traffic Light Controller) 自然语言描述: 在 FR 与 HW 的十字交叉口 ( 见图 1) 靠 FR and HW 的两边各设一个汽车检测器,用以检查 FR HW 上是否有汽车过往? 检测出有汽车 (Car_on_FR -- C_O_F) 作为系统的一个输入信号。

TLC 的设计

E N D

Presentation Transcript

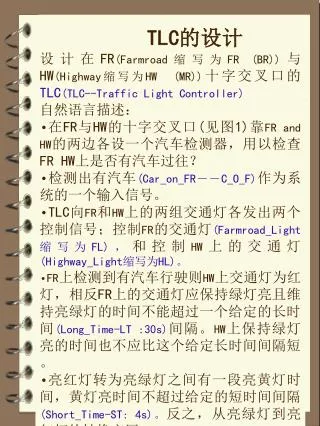

TLC的设计 • 设计在FR(Farmroad缩写为FR (BR))与HW(Highway缩写为HW (MR))十字交叉口的TLC(TLC--Traffic Light Controller) • 自然语言描述: • 在FR与HW的十字交叉口(见图1)靠FR and HW的两边各设一个汽车检测器,用以检查FR HW上是否有汽车过往? • 检测出有汽车(Car_on_FR--C_O_F)作为系统的一个输入信号。 • TLC向FR和HW上的两组交通灯各发出两个控制信号;控制FR的交通灯(Farmroad_Light缩写为FL),和控制HW上的交通灯(Highway_Light缩写为HL)。 • FR上检测到有汽车行驶则HW上交通灯为红灯,相反FR上的交通灯应保持绿灯亮且维持亮绿灯的时间不能超过一个给定的长时间(Long_Time-LT :30s)间隔。HW上保持绿灯亮的时间也不应比这个给定长时间间隔短。 • 亮红灯转为亮绿灯之间有一段亮黄灯时间,黄灯亮时间不超过给定的短时间间隔(Short_Time-ST: 4s)。反之,从亮绿灯到亮红灯的转换亦同。

FL • 乡间 • 高速HL 公路 • 公路 • 图 HW和FR交叉路口的交通灯 • 上述设计规范要完成三方面的设计描述: • 定义顶层的接口(I/O); • 描述底层的行为功能; • 设计验证方案(即设计仿真的激励与输出仿真结果)。

把设计规范从自然语言转换为机器接受的硬件描述语言是设计描述。可用4个有限状态来描述交通灯的控制行为,故TLC的设计是一个有限状态机。它有4个状态:把设计规范从自然语言转换为机器接受的硬件描述语言是设计描述。可用4个有限状态来描述交通灯的控制行为,故TLC的设计是一个有限状态机。它有4个状态: 1)初始状态a;HW亮绿色交通灯时,乡间道路的红色交通灯亮。 2)第二个状态b;HW变为黄色交通灯亮的等待切换状态。 3)第三个状态c ;HW红色交通灯亮时,乡间道路的绿色交通灯亮。 4)第四个状态d; FR变为黄色交通灯亮的等待切换状态。 须指出,HW上灯为绿色时相反在乡间道路上是红色。 a HW 绿灯亮 car_on_Farmroad=1 and Timed_out_short4s=1 Timed_out_short4s=1 d FR 黄灯亮 b HW 黄灯亮 交通控制灯的 状态转移图 car_on_short=0 or Timed_out_long30s=1 Timed_out_short4s=1 d FR 绿灯亮

表1 交通控制灯的状态转移表 • 当前 转移条件 下一 输出状态 • 状态 状态 高速公路 乡间公路 • 亮灯颜色 亮灯颜色 • a SB=1 ; MB=1 • 和 • s=30s OR SB=1, b 绿 红 • b S=2s c 黄 红 • c SB=0; MB=1 • OR • S=30s d红 绿 • d S=2s a红 黄 • 对4个状态,9个信号(3个输入,6个输出) 需建立两种数据类型的设计对象; • 一种是系统的可枚举数据类型,即: • type state is (a,b, c, d); • singnal state :state_type;

归纳一下: • 这是个4个状态的有限状态机的设计; • 它有9种信号端口; • 为设计定义了数据类型(可枚举数据类型说明的状态变量;用BIT类型说明的乡间公路上汽车有无的检测和灯亮的颜色。); • 还定义了4种节点信号(即BG绿灯亮的最长持续时间30s和黄灯亮的最短保持时间4s,CLS 清零,EN en=0保持功能)。

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; entity jtd is port (clk,sm,sb:in bit; MR,MY,MG,BR,BY,BG:out bit); end jtd; ARCHITECTURE a_f OF jtd IS type state_type is (a,b,c,d); signal state : state_type; begin cnt: process ( clk ) variable s : integer range 0 to 29; variable clr,en :bit; begin if clk'event and clk='1' then if clr ='0' then s:=0; elsif en ='0' then s:=s; else s:=s+1; end if;

case state is when a=>MR<='0';MY<='0'; MG<='1'; BR<='1';BY<='0'; BG<='0'; If sb='1' and sm='1' then If s >=29 then state <=b; clr:='0'; en:='0'; else state<=a;clr:='1';en:='1'; end if; elsif sb='1' AND sm ='0' then State<=b; clr:='0';en:='0'; else state<=a;clr:='1';en:='1'; end if; when b=>MR<='0';MY<='1';MG<='0'; BR<='1';BY<='0';BG<='0'; If s=3 then state<=c; clr:='0'; en:='0'; else state<=b;clr:='1';en:='1'; end if;

when c=>MR<='1';MY<='0'; MG<='0'; BR<='0';BY<='0'; BG<='1'; If (sb='1') then If s >=29 then state<=d; clr:='0'; en:='0'; else state<=c;clr:='1';en:='1'; end if; else state<=d;clr:='1';en:='1'; end if; when d=>MR<='1';MY<='0';MG<='0'; BR<='0';BY<='1';BG<='0'; If s=3 then state<=a; clr:='0'; en:='0'; else state<=d;clr:='1';en:='1'; end if; When others=> state<=a;clr:='0';en:='0'; END CASE; End if; END PROCESS cnt; END a_f;

用新的数据(便于波形仿真MG=6s,BY= 2s)改写TLC的电路描述: begin if clk'event and clk='1' then if clr ='0' then s:=0; elsif en ='0' then s:=s; else s:=s+1; end if; case state is when a=>MR<='0';MY<='0'; MG<='1'; BR<='1';BY<='0'; BG<='0'; If sb='1' and sm='1' then If s >=5 then state <=b; clr:='0'; en:='0'; else state<=a;clr:='1';en:='1'; end if; elsif sb='1' AND sm ='0' then State<=b; clr:='0';en:='0'; else state<=a;clr:='1';en:='1'; end if; when b=>MR<='0';MY<='1';MG<='0'; BR<='1';BY<='0';BG<='0'; If s=2 then state<=c; clr:='0'; en:='0'; else state<=b;clr:='1';en:='1'; end if; when c=>MR<='1';MY<='0'; MG<='0'; BR<='0';BY<='0'; BG<='1'; If (sb='1') then If s >=5 then state<=d; clr:='0'; en:='0'; else state<=c;clr:='1';en:='1'; end if; else state<=d;clr:='1';en:='1'; end if; when d=>MR<='1';MY<='0';MG<='0'; BR<='0';BY<='1';BG<='0'; If s=2 then state<=a; clr:='0'; en:='0'; else state<=d;clr:='1';en:='1'; end if; When others=> state<=a;clr:='0';en:='0'; END CASE; End if; END PROCESS cnt; END a_f;

开机延时3s (MR=1,BR=1)后,转入正常控制 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; entity jtd2 is port (clk,sm,sb:in bit; MR,MY,MG,BR,BY,BG:out bit); end jtd2; ARCHITECTURE a_f OF jtd2 IS type state_type is (o,a,b,c,d); signal state : state_type; begin cnt: process ( clk ) variable s : integer range 0 to 29; variable clr,en :bit; begin if clk'event and clk='1' then if clr ='0' then s:=0; elsif en ='0' then s:=s; else s:=s+1; end if; case state is When o=>MR<='1';MY<='0'; MG<='0'; BR<='1';BY<='0'; BG<='0'; if s=3 then state<=a ;clr:='0';en:='0'; else state<=o;clr:='1';en:='1'; end if; when a=>MR<='0';MY<='0'; MG<='1'; BR<='1';BY<='0'; BG<='0'; If sb='1' and sm='1' then If s >=5 then state <=b; clr:='0'; en:='0'; else state<=a;clr:='1';en:='1'; end if; elsif sb='1' AND sm ='0' then State<=b; clr:='0';en:='0'; else state<=a;clr:='1';en:='1'; end if; when b=>MR<='0';MY<='1';MG<='0'; BR<='1';BY<='0';BG<='0'; If s=2 then state<=c; clr:='0'; en:='0'; else state<=b;clr:='1';en:='1'; end if; when c=>MR<='1';MY<='0'; MG<='0'; BR<='0';BY<='0'; BG<='1'; If (sb='1') then If s >=5 then state<=d; clr:='0'; en:='0'; else state<=c;clr:='1';en:='1'; end if; else state<=d;clr:='1';en:='1'; end if; when d=>MR<='1';MY<='0';MG<='0'; BR<='0';BY<='1';BG<='0'; If s=2 then state<=a; clr:='0'; en:='0'; else state<=d;clr:='1';en:='1'; end if; END CASE; End if; END PROCESS cnt; END a_f;

如发生紧急情况,则按下一个按钮, 使主、次干道红灯亮,松开按钮则 被打断的状态继续进行。

对TLC实体的structure_1结构体描述如下: ARCHITECTURE structure_1 OF TLC IS SIGNAL present_state : state := Highway_light_Green; SIGNAL Timed _out_long, Timed_out_short : data_type := `0`; SIGNAL start_Timer : data_type := `0`; COMPONENT Timer_section GENERIC (long_Time, short_Time : time); PORT (start : IN data_type ; TL,TS : OUT data_type); END COMPONENT; BEGIN PROCESS BEGIN CASE present_state IS WHEN Highway_Light_Green => IF car_on_Farmroad AND Timed_out_long =‘1’ THEN state_Timer <=TRANSPORT NOT state_Timer; present_state <= TRANSPORT Highway_Light_Yellow; END IF; WHEN Highway_Light_Yellow => IF Timed_out_short =‘1’ THEN state_Timer <=TRANSPORT NOT state_Timer; present_state <= TRANSPORT Farmroad_Light_Green; END IF;

WHEN Farmroad_Light_Green => IF NOT car_on_Farmroad OR Timed_out_long =‘1’ THEN start_Timer <=TRANSPORT NOT start_Timer; present_state<=TRANSPORTFarmroad_Light_Yellow; END IF; WHEN Farmroad_Light_Yellow => IF Timed_out_short =‘1’ THEN start_Timer <=TRANSPORT NOT start_Timer; present_state <= TRANSPORT Highway_Light_Green; END IF; END CASE; WAIT ON car_on_Farmroad, Timed_out_long, Timed_on_short; END PROCESS; --Highway_light_set: with Present_state select Highway_light<= Green WHEN Highway_light_Green, Yellow WHEN Highway_light_Yellow, Red WHEN Farmroad_light_Green| Farmroa_light_Yellow;

--Farmroad_light_set: with Present_state select Farmroad_light<= Green WHEN Farmroad_light_Green, Yellow WHEN Farmroad_light_Yellow, Red WHEN Highway_light_Green|Highway _Light_Yellow; --Timer_struct : Timer_section GENERIC MAP ( long_Time ,short_Time); PORT MAP (start_Time, Timed_out_long, Timed_out_short); END structuer_1; 为Timer实体的结构体structure_1,做了struct1的配置: USE Work.all; CONFIGURATION struct1 OF TLC_TEST IS FOR Test FOR controller : TLC USE ENTITY Work.TLC(structure_1); FOR structure_1; FOR Timer_struct : Timer_section USE ENTITY Work.Timer(behavior); END FOR; END FOR; END FOR; END FOR; END struct1;

控制器元件的设计细化:在顶层TLC实体下,分出实体(TL_controller) 和Timer实体。实体(TL_controller)的接口:Car_on_Farmroad、(HL)与 (FL), Timer实体接口:Start_timer、TL和TS 。综合起来,该控制器有三个输入(Car_on_Farmroad简写为C,两个超时输入记以TL和TS)和三个输出(一个启动计时器为ST,两个灯控制为HL和FL)。 9.2.8.1 控制器实体的VHDL描述为 USE Work.Traffic_package.all; USE Work.design_package.all; ENTITY TL_controller IS PORT ( C ,TL,TS : IN data_type ; HL,FL : OUT color_bits ; ST : OUT data_type); END TL_controller ; 现在用bit表示,以便提取具体实现的电路结构。 ARCHITECTURE behavior OF TL_controller IS SIGNAL controller_state : state_bits := Highway_light_Green; BEGIN --controller_process PROCESS Vriable last_ST : DATA_TYPE := ‘0’; BEGIN

CASE controller_state IS WHEN HG_state => IF C=‘1’ AND TL =‘1’ THEN last_ST := NOT last_ST; ST <= TRANSPORT last_ST; controller_state <= TRANSPORT HY_state; END IF; WHEN HY_state => IF TS =‘1’ THEN last_ST := NOT last_ST; ST <= TRANSPORT last_ST; controller_state <= TRANSPORT FG_state; END IF; WHEN FG_state => IF C=‘0’ AND TL =‘1’ THEN last_ST := NOT last_ST; ST <= TRANSPORT last_ST; controller_state <= TRANSPORT FY_state; END IF; WHEN FY_state => IF TS =‘1’ THEN last_ST := NOT last_ST; ST <= TRANSPORT last_ST; controller_state <= TRANSPORT HG_state; END IF; END CASE;

WAIT ON C, TL, TS; END PROCESS; --Highway_light: with controller_state select HL<= Green_light WHEN HG_state, Yellow_light WHEN HY_state, Red_light WHEN FG_state FY_state; --Farmroad_light: with controller_state select FL<= Green_Light WHEN FG_state, Yellow_Light WHEN FY_state, Red_Light WHEN HG_state | HY_state; END behavior; 用底层两个结构体描述顶层TLC的structure_2结构体。 USE Work.design.package.all; ARCHITECTURE structure_2 OF TLC IS SIGNAL Timed _out_long, Timed_out_short : data_type := ‘0’; SIGNAL start_Timer : data_type := ‘0’; COMPONENT Timer_section GENERIC (long_Time, short_Time : time); PORT ( start : IN data_type ; TL,TS : OUT data_type); END COMPONENT;

COMPONENT Controller_section PORT (C,TL,TS : IN data_type ; HL,FL : OUT color_bits ST : OUT data_type); END COMPONENT; BEGIN --Traffic_Light : controller_section PORT MAP( bit_to_boolean ( car_on_framroad ), Timed_out_long, Timer_out_short, bits_to_color(HL) => Highway_Ligh, bits_to_color(FL) => Framroad_Ligh, ST => state_Timer ); --Timer_struct : Timer_section GENERIC MAP ( long_Time short_Time); PORT MAP (start_Time Timed_out_long, Timed_out_short); END structuer_2; 这是一种结构化的结构体,在结构体说明中用了对Timer和Controller的元件说明,在结构体语句中用元件具体装配语句把它们连接起来。

用配置语句出新的元件清单和连接关系。 USE Work.all; CONFIGURATION struct2 OF TLC_TEST IS FOR Test FOR controller : TLC USE ENTITY TLC(structure_2); FOR structure_2; USE Work.all; FOR Traffic_Light : controller_section USE ENTITY Work.TL_ controller(behavior); END FOR FOR Timer_struct : Timer_section USE ENTITY Work.Timer(behavior); END FOR; END FOR; END FOR; END FOR; END struct2; 用PLA实现具体电路,将电路分解成积之和的形式,并应将上述描述转换成 (Bit)表示方式: 输入 当前状态 下次状态 输出 C TL TS Y(0) Y(1) Y(0) Y(1) ST HL(0) HL(1) FL(0) Fl(1) 0 X X 0 0 0 0 0 0 0 1 0 X 0 X 0 0 0 0 0 0 0 1 0 1 1 X 0 0 0 1 1 0 0 1 0 X X 0 0 1 0 1 0 0 1 1 0 X X 1 0 1 1 1 1 0 1 1 0 1 0 X 1 1 1 1 0 1 0 0 0 0 X X 1 1 1 0 1 0 0 0 0 X 1 X 1 1 1 0 1 1 0 0 0 X X 0 1 0 1 0 0 1 0 0 1 X X 1 1 0 0 0 1 1 0 0 0

将TC.controller的状态和灯的颜色用二位矢量说明:将TC.controller的状态和灯的颜色用二位矢量说明: 状 态 y(0) y(1) 颜 色 HG(高速公路上绿灯亮) 0 0 GL(亮绿灯) HY(高速公路上黄灯亮) 0 1 YL(亮黄灯) FG(乡间公路上绿灯亮) 1 1 不 亮 FY(乡间公路上黄灯亮) 1 0 RL(亮红灯) 用积之和形式描述结构体Behavior_2 of TL_Controller: ARCHITECTURE behavior_2 OF TL_controller IS SIGNAL controller_state : state := Highway_light_Green; SIGNAL Y : state_bits := B“00”; BEGIN Y <= STATE_TO_BITS (controller_state); PROCESS VAriable sumofproducts : bit_vector(0 to 6) ; BEGIN controller_state <= bits_to_state(Y); IF C= ‘0’ AND Y(0) = ‘0’ AND Y(1) = ‘0’ THEN sumofproducts := B“0000010”; ELSIF TL= ‘0’ AND Y(0) = ‘0’ AND Y(1) = ‘0’ THEN sumofproducts := B“0000010” ; ELSIF C= ‘1’ AND TL = ‘1’ AND Y(0) = ‘0’ AND Y(1) = ‘0’THEN sumofproducts := B“0110010” ; ELSIF TS= ‘0’ AND Y(0) = ‘0’ AND Y(1) = ‘1’ THEN sumofproducts := B“0100110” ;

ELSIF TS= ‘1’ AND Y(0) = ‘0’ AND Y(1) = ‘1’ THEN sumofproducts := B“1110110” ; ELSIF C= ‘1’ AND TL = ‘0’ AND Y(0) = ‘1’ AND Y(1) = ‘1’THEN sumofproducts := B“1101000” ; ELSIF C= ‘0’ AND Y(0) = ‘1’ AND Y(1) = ‘1’ THEN sumofproducts := B“1010000” ; ELSIF TL= ‘1’ AND Y(0) = ‘1’ AND Y(1) = ‘1’ THEN sumofproducts := B“1011000” ; ELSIF TS= ‘0’ AND Y(0) = ‘1’ AND Y(1) = ‘0’ THEN sumofproducts := B“1001001” ; ELSIF TS= ‘1’ AND Y(0) = ‘1’ AND Y(1) = ‘0’ THEN sumofproducts := B“0011001” ; END IF; controller_state := TRANSPORT bits_to_state(state_bits (sumofproducts(0 to 1))); ST <= TRANSPORT sumofproducts(2); HL<= TRANSPORT Color_bits sumofproducts(3 to 4); FL <= TRANSPORT Color_bits sumofproducts(5 to 6); WAIT ON C, TL, TS, Y(0), Y(1) ; END PROCESS; END behavior_2;

用(behavior_2) 做测试配置struc3,再次验证其正确性。 USE Work.all; CONFIGURATION struct3 OF TLC_TEST IS FOR Test FOR controller : TLC USE ENTITY TLC(structure_2); FOR structure_2; USE Work.all; FOR Traffic_Light : controller_section USE ENTITY Work.TL_ controller(behavior_2); END FOR FOR Timer_struct : Timer_section USE ENTITY Work.Timer(behavior); END FOR; END FOR; END FOR; END FOR; END struct3; VHDL描述将状态转换表转换为PLA表的积之和:建立有5个输入和7个输出的PLA实体。先重新建立端口的映射关系,再开发PLA行为模型。 端口的映射关系如下 C in0 new_tsate,0 out0 TL in1 new_tsate,1 out1 TS in2 new_tsate,2 out2 Y(0) in3 new_tsate,3 out3 Y(1) in4 new_tsate,4 out4 new_tsate,5 out5 new_tsate,6 out6

状态的映射关系如下 “0000010” new_state := 0 “0000010” new_state := 1 “0110010” new_state := 2 “0100110” new_state := 3 “1110110” new_state := 4 “1101000” new_state := 5 “1010000” new_state := 6 “1011000” new_state := 7 “1001001” new_state := 8 “0011001” new_state := 9 写出控制器PLA形式的实体和结构体如下: ENTITY PLA IS PORT (in0,in1,in2,in3,in4 : IN BIT; out0,out1,out2,out3,out4,out5,out6 : OUT BIT); END PLA; ARCHITECTURE behavior 1 OF PLA IS TYPE PLA_Matrix IS ARRAY (INTEGER RANGE 0 TO 9, INTEGER RANGE 0TO 6) OF BIT; CANSTANT PLA_outputs : PLA_Matrix := ( (‘0’, ‘0’, ‘0’, ‘0’, ‘0’, ‘1’, ‘0’); (‘0’, ‘0’, ‘0’, ‘0’, ‘0’, ‘1’, ‘0’); (‘0’, ‘1’, ‘1’, ‘0’, ‘0’, ‘1’, ‘0’); (‘0’, ‘1’, ‘0’, ‘0’, ‘1’, ‘1’, ‘0’); (‘1’, ‘1’, ‘1’, ‘0’, ‘1’, ‘1’, ‘0’); (‘1’, ‘1’, ‘0’, ‘1’, ‘0’, ‘0’, ‘0’); (‘1’, ‘0’, ‘1’, ‘0’, ‘0’, ‘0’, ‘0’); (‘1’, ‘0’, ‘1’, ‘1’, ‘0’, ‘0’, ‘0’); (‘1’, ‘0’, ‘0’, ‘1’, ‘0’, ‘0’, ‘1’); (‘0’, ‘0’, ‘1’, ‘1’, ‘0’, ‘0’, ‘1’));

BEGIN PROCESS VARIABLE new_state : INTEGER; BEGIN IF in0= ‘0’ AND in3 = ‘0’ AND in4 = ‘0’ THEN new_state := 0; ELSIF in1= ‘0’ AND in3 = ‘0’ AND in4 = ‘0’ THEN new_state := 1 ; ELSIF in0= ‘1’ AND in1 = ‘1’ AND in3 = ‘0’ AND in4 = ‘0’ THEN new_state := 2 ; ELSIF in2= ‘0’ AND in3 = ‘0’ AND in4 = ‘1’ THEN new_state := 3 ; ELSIF in2= ‘1’ AND in3 = ‘0’ AND in4 = ‘1’ THEN new_state :=4 ; ELSIF in0= ‘1’ AND in1 = ‘0’ AND in3 = ‘1’ AND in4 = ‘1’ THEN new_state := 5 ; ELSIF in0= ‘0’ AND in1 = ‘0’ AND in3 = ‘1’ AND in4 = ‘1’ THEN new_state := 6 ; ELSIF in1= ‘1’ AND in3 = ‘1’ AND in4 = ‘1’ THEN new_state := 7 ; ELSIF in2= ‘0’ AND in3 = ‘1’ AND in4 = ‘0’ THEN new_state := 8 ; ELSIF in2= ‘1’ AND in3 = ‘1’ AND in4 = ‘1’ THEN new_state := 9 ;

ELSE ASSERT (FALSE) REPORT “error in PLA” SEVERITY error; END IF; --建立一个输出描述 out0 <= PLA_outputs(new_state,0); out1 <= PLA_outputs(new_state,1); out2 <= PLA_outputs(new_state,2); out3 <= PLA_outputs(new_state,3); out4 <= PLA_outputs(new_state,4); out5 <= PLA_outputs(new_state,5); out6 <= PLA_outputs(new_state,6); WAIT ON in0,in1,in2,in3,in4; END PROCESS; END behavior1; PLA表方式的控制器行为结构体(behavior1)模型的元件,可以作为交通灯控制器的一个具体装配元件。为此,生成控制器实体的结构化结构体(structure)。ARCHITECURE structure OF TL_controller IS SIGNAL controller_state : state := Highway_Light_Green; SIGNAL Yin : state_bits := B“00”; SIGNAL Yout : state_bits := B“00”; COMPONENT PLA_section PORT (in0,in1,in2,in3,in4 : IN BIT; out0,out1,out2,out3,out4,out5,out6 : OUT BIT); END COMPONENT ;

BEGIN Yin <= state_to_bits (controller_state); controller_state <= bits_to_state( Yout) ; -- Imp1 : PLA_section PORT MAP ( C,TL,TS,Yin(0),Yin(1) , Yout(0),Yout(1), ST,HL(0),HL(1),FL(0),FL(1)); END structure ; 配置语句struct4 描述如下: USE Work.all; CONFIGURATION struct4 OF TLC_TEST IS FOR Test FOR controller : TLC USE ENTITY TLC(structure_2); FOR structure_2; USE Work.all; FOR Traffic_Light : controller_section USE ENTITY Work.TL_ controller(structure); FOR structuer FOR Imp1 : PLA_section USE ENTITY work.PLA (behavior1) ; END FOR; END FOR; END FOR; FOR Timer_struct : Timer_section USE ENTITY Work.Timer(behavior); END FOR; END FOR; END FOR; END FOR; END struct3;

定时器的设计细化,设计两个可控计数长度的予置计数器产生定时超出信号(TL)和(TS)。用PLA元件做设计,写出Timer下层的两个计数器实体(实体TOL和实体TOS)。定时器的设计细化,设计两个可控计数长度的予置计数器产生定时超出信号(TL)和(TS)。用PLA元件做设计,写出Timer下层的两个计数器实体(实体TOL和实体TOS)。 用pla表的TOL计数器实体的一段VHDL描述 ENTUTY TOL IS GENERIC (binaryL : std_logic_vector(3 DOWNTO 0)); PORT (ST, EN,clk: IN std_logic; binary : IN std_logic_vector(3 DOWNTO 0); TL : OUT std_logic); END TOL; ARCHITECTURE behaviorL OF TOL IS SIGNAL next_count,mux_Z: std_logic_vector(3 DOWNTO 0); CONSTANT trans_table: std_logic_2d (0 TO 15,7DOWNTO 0):=(--Table format is :binary_nextent “00000001”, “00010010”, “00100011”, “00110100”, “01000101”, “01010110”, “01100111”, “01111000”, “10001001”, “10011010”, “10101011”, “10111100” “11001101” “11011110” “11101111” “11110000”);

BEGIN pla_table(binary,next_count,trans_table); GENERIC MAP ( binaryL); IF (ST = ‘0’) THEN mux_Z <= “0000”; ELSE mux_Z <=next_count WHEN(EN=‘1’) ELSE binary; END IF; TOL<=‘1’ WHEN (EN=‘1’ and NEXT_COUNT=“0000”) ELSE ‘0’; dffc_v(mux_Z ,ST,clk,binary); END behaviorL; 用pla表的TOS计数器实体的一段VHDL描述 ENTUTY TOS IS GENERIC (binaryS : std_logic_vector(3 DOWNTO 0)); PORT (ST, EN,clk: IN std_logic; binary : IN std_logic_vector(3 DOWNTO 0); TL: OUT std_logic); END TOS; ARCHITECTURE behavior OF TOS IS SIGNAL next_count,mux_Z: std_logic_vector(3 DOWNTO 0); CONSTANT trans_table: std_logic_2d (0 TO 15, 7 DOWNTO 0):=(

“00000001”, “00010010”, “00100011”, “00110100”, “01000101”, “01010110”, “01100111”, “01111000”, “10001001”, “10011010”, “10101011”, “10111100” “11001101” “11011110” “11101111” “11110000”); BEGIN pla_table(binary,next_count,trans_table); GENERIC MAP ( binaryL); IF (ST = ‘0’) THEN mux_Z <= “0000”; ELSE mux_Z <=next_count WHEN(EN=‘1’) ELSE binary; END IF; TOS<=‘1’ WHEN (EN=‘1’ and NEXT_COUNT=“0000”) ELSE ‘0’; dffc_v(mux_Z ,ST,clk,binary); END behavior;

定时器构造一个结构化的结构体(structureT) ARCHITECURE structureT OF Timer IS COMPONENT binary_count4 GENERIC (binaryX : std_logic_vector(3 DOWNTO 0)); PORT (Cler, load,clk: IN std_logic; Din :IN std_logic_vector(3 DOWNTO 0); Cout: OUT std_logic); END COMPONENT ; BEGIN --TOL_section : GENERIC MAP(binaryL); PORT MAP(ST, EN,clk,binary ,TL); GENERIC MAP ( binaryS); PORT MAP (ST, EN,clk,binary ,TS); END structureT ;

TLC的完整配置(struct_TLC) USE Work.all; CONFIGURATION struct_TLC OF TLC_TEST IS FOR Test FOR controller : TLC USE ENTITY TLC(structure_2); FOR structure_2; USE Work.all; FOR Traffic_Light : controller_section USE ENTITY Work.TL_ controller(structure); FOR structuer FOR Imp1 : PLA_section USE ENTITY work.PLA (behavior1) ; END FOR; END FOR; END FOR; FOR Timer_struct : Timer_section USE ENTITY Work.Timer(structureT); END FOR; END FOR; END FOR; END FOR; END struct3;