Serialization

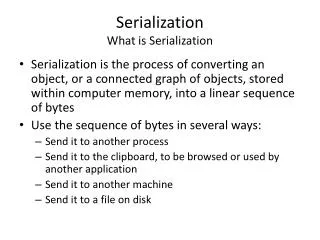

Serialization. Complete set of serialization conveys the same information as the precedence graph itself, i.e., s < t is implied by the precedence graph if and only if s < t is in every serialization

Serialization

E N D

Presentation Transcript

Serialization • Complete set of serialization conveys the same information as the precedence graph itself, i.e., s < t is implied by the precedence graph if and only if s < t is in every serialization • Thus introducing new precedence constraints (e.g., those imposed by the data path topology design) can be characterized by enumerating the serializations ruled out by the new constraints

A <-- f f A <-- g g r(x) B <-- P2 p2 x A <-- X B <-- h h B <-- P1 p1 Optimizing Data Path Topology • Let us include a register load operation in our notation • A <-- B means load output of B into A • We have mutual exclusion constraints between A <-- B and C <-- D unless B and D are identical • So our new precedence graph is given by as shown in figure • Why we need to load h in B first before we load f in A? • Since B must get h before A gets value of f, we have a new constraint h < g that we did not have before • In other words h and g cannot be performed concurrently • If h and g are slow, then we may be slowing down a lot

O U T P U T S Next State Logic Output Logic I N P U T S B A BLE ALE x xd f g p h gd pd hd fd Put it all together: Control State machine • The data path in multifunctional unit is controlled by a state machine like shown below • All control signals like xd, fd, gd, hd, pd, ALE and BLE are generated as outputs • Inputs to state machine are clock and start, stop kind of signals • For every computation, state machine starts and generate control signals, for one step at a time

O U T P U T S Next State Logic Output Logic I N P U T S B A BLE ALE x xd f g p h gd pd hd fd Computing with Data Path and Control • Suppose we want to compute p(f(x), h(x)) • The control will look like as follows with one cycle per function xd fd gd hd pd ALE BLE 1 0 0 0 0 1 0 0 0 0 1 0 0 1 0 1 0 0 0 1 0 0 0 0 0 1 0 1