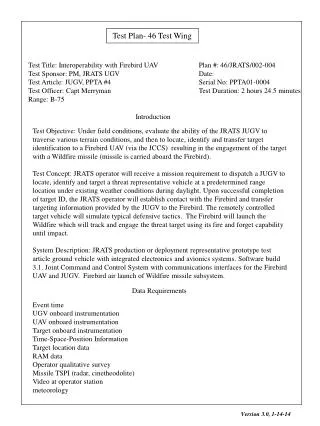

Main Memory: Addressing, Swapping, & Allocation Techniques

E N D

Presentation Transcript

CS 346 – Chapter 8 • Main memory • Addressing • Swapping • Allocation and fragmentation • Paging • Segmentation • Commitment • Please finish chapter 8

Addresses • CPU/instructions can only access registers and main memory locations • Stuff on disk must be loaded into main memory • Each process given range of legal memory addresses • Base and limit registers • Accessible only to OS • Every address request compared against these limits • When is address of an object determined? • Compile time: hard-coded by programmer • Load time: compiler generates a relative address • Execute time: if address may vary during execution because the process moves. (most flexible)

Addresses (2) • Logical vs. physical address • Logical (aka virtual): The address as known to the CPU and source code • Physical = the real location in RAM • How could logical and physical address differ? In case of execution-time binding. i.e. if the process location could move during execution • Relocation register • Specifies what constant offset to add to logical address to obtain physical address • CPU / program never needs to worry about the “real” address, or that addresses of things may change. It can pretend its address start at 0.

Swapping • A process may need to go back to disk before finishing. • Why? • Consequence of scheduling (context switch) • Maintain a queue of processes waiting to be loaded from disk • Actual transfer time is relatively huge • When loading a program initially, we might not want to load the whole thing • Another question – what to do if we’re swapped out while waiting for I/O. • Don’t swap if waiting for input; or • Put input into buffer. Empty buffer next time process back in memory.

Allocation • Simplest technique is to define fixed-size partitions • Some partitions dedicated to OS; rest for user processes • Variable-size partitions also possible, but must maintain starting address of each • Holes to fill • How to dynamically fill hole with a process: • First fit: find the first hole big enough for process • Best fit: find smallest one big enough • Worst fit: fit into largest hole, in order to create largest possible remaining hole • Internal & external fragmentation

Paging • Allows for noncontiguous process memory space • Physical memory consists of “frames” • Logical memory consists of “pages” • Page size = frame size • Every address referenced by CPU can be resolved: • Page number • Offset • how to do it? Turns out page/frame size is power of 2. Determines # bits in address. • Look up page number in the page table to find correct frame

Example • Suppose RAM = 256 MB, page/frame size is 4 KB, and our logical addresses are 32 bits. • How many bits for the page offset? • How many bits for the logical/virtual page number? • How many bits for the physical page number? • Note that the page offsets (logical & physical) will match. • A program’s data begins at 0x1001 0000, and text begins at 0x0040 0000. If they are each 1 page, what is the highest logical address of each page? • What physical page do they map to? • How large is the page table?

Page table • HW representation • Several registers • Store in RAM, with pointer as a register • TLB (“translation look-aside buffer”) Functions as a “page table cache”: Should store info about most commonly occurring pages. • How does a memory access work? • First, inspect address to see if datum should be in cache. • If not, inspect address to see if TLB knows physical address • If no TLB tag match, look up logical/virtual page number in the page table (thus requiring another memory access) • Finally, in the worst case, we have to go out to disk.

Protection, etc. • HW must ensure that accesses to TLB or page table are legitimate • No one should be able to access frame belonging to another process • Valid bit: does the process have permission to access this frame? • e.g. might no longer belong to this process • Protection bit: is this physical page frame read-only? • Paging supports shared memory. Example? • Paging can cause internal fragmentation. How? • Sometimes we can make page table more concise by storing just the bounds of the pages instead of each one.

Page table design • How to deal with huge number of pages • Hierarchical or 2-level page table • In other words, we “page” the page table. • Split up the address into 3 parts. “outer page”, “inner page” and then the offset. • The outer page number tells you where to find the appropriate part of the (inner) page table. See Figure 8.15. • Not practical for 64-bit addressing! Why not? • Hashed page table • Look up virtual page number in a hash table. • The contents of the cell might be a linked list: search for match. • Inverted page table • A table that stores only the physical pages, and then tells you which logical page map to each. Any disadvantage?

Segmentation • Alternative to paging • More intuitive way to lay out main memory… • Segments do not have to be contiguous in memory • Process has segment table: For each segment, stores the base address and size • As before, a process has a “logical address space” • But now: it consists of segments, each having a name and size. • How does a program(mer) specify an address in a segmented scheme? • What kinds of segments might we want to create for a program? • HW may support both paging and segmentation • So, OS may exploit either or both addressing techniques. • To ignore segmentation, just use 1 segment for entire process.

Pentium example • To convert logical to physical address • Handle the segmentation first… • Segmentation unit takes the logical address, and converts this to a linear address (why?) • Paging unit takes the linear address and converts this to a physical address (somewhat familiar process) • A segment may be up to 4 GB, so offset is 32 bits • Logical address has 2 parts: segment number plus offset • Look up segment number into “descriptor table”. Entries in this table give the upper bits of the 32-bit linear address. • Pentium uses 2-level paging • Outer and inner page numbers are 10 bits each. What information does this tell you?