WP9.4 SiTra integration into common DAQ

90 likes | 239 Views

WP9.4 SiTra integration into common DAQ. AIDA WP9.4 meeting. WP9.4 (silicon tracking) status. Within WP9.4 task, there is only one deliverable (due M39, April 2014) Status of baseline deliverable: Re-use old SiLC sensors done. APV25-based front-end done . Conventional mechanics done .

WP9.4 SiTra integration into common DAQ

E N D

Presentation Transcript

WP9.4 SiTra integration into common DAQ Thomas Bergauer AIDA WP9.4 meeting

WP9.4 (silicon tracking) status • Within WP9.4 task, there is only one deliverable (due M39, April 2014) • Statusof baseline deliverable: • Re-use old SiLC sensors done. • APV25-based front-end done. • Conventional mechanics done. • readout system hardware done. • Offline software done • Online (DAQ) software (re-implementation ongoing) • Integration with common DAQ missing Thomas Bergauer

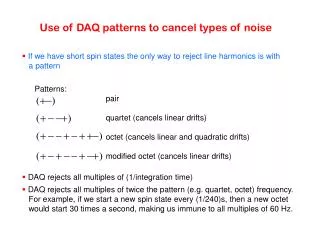

Data Acquisition System VME boards ~2mcoppercable Junctionbox ~10mcopper cable APV25chips • Status: • DAQ system based on APV25 readout chip (developed for CMS) • Three versions: • APVDAQ: lab-system for 4 APVs/boards; 1kHz using 1 card • SiTra DAQ: 16 APVs/board; 3kHz (Zero Suppressed) • Belle II System: 48APVs/board; up to 20kHz Front-endhybrids Rad-hardvoltageregulators Analog level translation,data sparsification andhit time reconstruction Thomas Bergauer

DAQ Details • Compatibility with (old) EUDET TLU box exists • Has been used in previous testbeams with EUDET telescope (since 2009) • offline merging of data streams • Uses “smart” mode, i.e. saves trigger number with each event • Needs external trigger (Scintillator) Thomas Bergauer

Readout System Components Repeater Box Level translation, buffering FADC+PROC (9U VME) Digitization, zero-suppression, hit time reconstruction Thomas Bergauer

Readout Chip: APV25 • Developed for CMS (LHC) by Imperial College London and Rutherford Appleton Lab • 70.000 chips installed • 0.25 µm CMOS process (>100 MRad tolerant) • 128 channels • 192 cell analog pipeline enables 160xTclock latency • 20-80 MHz clock frequency (40MHz nom.) using peak mode • 50 ns shaping time low occupancy • Noise: 250 e + 36 e/pF must minimize capacitive load!!! • Multi-peak mode (read out several samples along shaping curve) Thomas Bergauer

APV25 – Hit Time Reconstruction • Possibility of recording multiple samples (x) along shaped waveform (feature of APV25) • Reconstruction of peak time (and amplitude)by waveform fit • Offline now • LUT in Hardwarefor Belle II • Is used toremove off-timebackground hits Measurement Thomas Bergauer

Status DAQ software • DAQ online software was ported recently from old LabWindows/CVI system to Linux/ROOT-based system • Basic functionality available • implementation of sophisticated run modes ongoing (ADC delay scan, calibration scan,…) to be done by the end of the year • Offers modular system • Dummy EUDAQ producer exists, interface to new software seems to be possible Thomas Bergauer

Summary • WP9.4 deliverable (hardware) will be available in summer this year • Sensors, FE electronics, mechanics, DAQ Hardware (mid-size System) • DAQ Software re-implementation ongoing • Basic functionality available • Modular design • TLU integration (stores trigger number) • Interface to EUDAQ possible via EUDAQProducer Thomas Bergauer