Georgia Tech Digital Back-end µHRG interface

380 likes | 745 Views

Georgia Tech Digital Back-end µHRG interface. Curtis Mayberry School of Electrical and Computer Engineering Georgia Institute of Technology. January 13 th , 2014. Contact: Curtisma@gatech.edu www.ece.gatech.edu/research/integrated-mems/. Topics. System Design Digital Processing ADC

Georgia Tech Digital Back-end µHRG interface

E N D

Presentation Transcript

Georgia Tech Digital Back-endµHRG interface Curtis Mayberry School of Electrical and Computer Engineering Georgia Institute of Technology January 13th, 2014 Contact: Curtisma@gatech.edu www.ece.gatech.edu/research/integrated-mems/

Topics • System Design • Digital Processing • ADC • DAC • Power Supply • AFE Interface • Feed Through Cancellation Tuning • Review Measures Topics

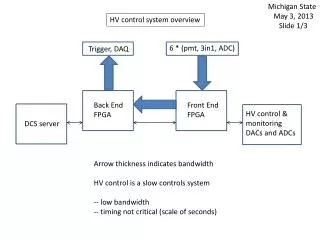

System Overview • Analog Front End (Red Board) • Device Pad • Pickoff Channels (Node and Antinode) • Forcer Channels (node and Antinode) • Feed-through Cancellation (x4) • Quadrature Amplifiers (50v) • Digital Back End (GT BE) • 24 bit ADC (8 Channels) and LPF ADC Drivers • 16 bit DAC (8 Channels) and Reconstruction LPF • Feed Through Cancellation Tuning Digital Potentiometers • Digital Signal Processor (TI Tiva C Launchpad) • 80 MHz MCU Development Board System Design

System Diagram System Design

Microcontroller: TI Tiva C Series • 80 MHz 32bit MCU (internal PLL to adjust) • 4xSPI Serial communication • Single Precision Floating point • 128 kB Flash • Up to 43 GPIOs • Tiva C Launchpad • Microcontroller Part Number: TM4C123GH6PMI • On-board ICDI • USB programmer and debugger • 40 Pin Header to connect to back-end • On-board RGB LED and 2 Switches • USB Powered Digital Processing

Alternative Signal Processor: FPGA • Spartan 6 XC6SLX9 FPGA • 84 digital IO pins • 8 analog inputs • 8 general purpose LEDs • 1 reset button • 1 LED to show when the FPGA is correctly configured • On board voltage regulation that can handle 4.8V - 12V • A microcontroller (ATmega16U4) used for configuring the FPGA, USB communications, and reading the analog pins • On board flash memory to store the FPGA configuration file Digital Processing

Connection: Launchpad • Board designed to mate on top of Tiva C series Launchpad • Uses female 0.1” Low profile Headers by Samtec to mate with the Launchpad • Can use ribbon cable and header strip to reposition Launchpad Interface

Connection: Launchpad Ports Interface

Launchpad Interface Pinout Interface

ADC: High Resolution • TI ADS1278 • 24 bit, up to 111 dB SNR (52kSPS) • 8 Channel, simultaneous sample • Up to 144 kSPS (w/ 106 SNR) • SPI or Frame-Sync Serial Interface • No registers: all settings set by pins (GPIO) • Power Supplies • Analog VDD: 5v • Digital Core: 1.8v • IO VDD: 3.3v • Initialization • Settings set digitally by GPIOs • Jumpers: Clock input selection and power down selection ADC

ADC Sampling Frequency and Resolution • Is a 144 kSPS sampling frequency fast enough? • Over-sampling Rate • High-resolution mode: 128 • All other modes: 64 • 39 dB or 45 dB (HR) of image Rejectioin • Is 24-bits of resolution good enough? • More than high enough resolution ADC

ADC Schematic: Main Fully Differential ADC Drivers (4ch) Single Ended ADC Drivers (4ch) ADC Shutdown Jumpers Clock Input Selection Jumper Common Mode Buffer ADC

Fully Differential ADC Driver • OPA1632 • Fully differential Audio Op-amp • sets common mode for ADC input • LOW NOISE: 1.3nV/√Hz • Gain Bandwidth: 180MHz • Jumper Option: ground Vin- for single-ended to differential conversion • ADC input channels 1-4 • Ch.1: Node Pickoff • Ch. 2: Antinode Pickoff • Ch. 3: Ain 3 • Ch.4: RTD • Supply: ±8v • Symmetric and Balanced Layout Schematic Layout ADC

AC Simulation Results AC Response @ fmax = 10 kHz Gain = 1 (-6 dB for each differential output) Phase = -3.76o Corner Frequency: 195.96 kHz Gain Peaking: 1.07 dB ADC

Transient Simulation Results Outputs Input ADC

ADC Common Mode Voltage Buffer • Buffers 2.5v Common Mode Voltage from ADC • Op-amp • OPA350 • Low Noise: 5nV/√Hz • Unity-gain stable • Single Supply: 5v Schematic Layout ADC

Voltage Reference • ADR4525 • 2.5v • Output Noise (0.1Hz to 10 Hz): <1μVpp • Initial Output Voltage Error: 0.02% • Input Voltage Range: 3v-15v • (Running off of regulated 5v Rail) • Output current:±10mA • TCVOUT: 2ppm/oc • Solder Heat Shift: ±0.02% • Long Term Drift: 25ppm/1000hrs @60oc Reference Schematic Trace to ADC Length: 17.08 mm Width: 0.35/0.254mm Reference Layout ADC

ADC Layout Channel Shutdown Jumpers CLK Selection Jumper ADS1278 ADC CH1 Fully Diff ADC Driver CH2 Fully Diff ADC Driver Single-Ended ADC Drivers Channels 5-8 CH3 Fully Diff ADC Driver Fully Differential ADC Drivers (4ch) CH4 Fully Diff ADC Driver ADC

DAC: High Resolution • ADI AD5754 • 16-bit • 4 Channel • Serial clock: up to 30 MHz • Programmable Bipolar/unipolar output • +5 V, +10 V, +10.8 V, ±5 V, ±10 V, ±10.8 V ( only 5v, ±5 V w/ Vs= ±8 V) • INL error: ±16 LSB maximum, • DNL error: ±1 LSB maximum • Integrated output and reference buffers DAC

DAC Reconstruction Filter • 2nd Order Sallen-Key Filter: Fc = 15kHz • 1st Order RC: Fc = 15.915 kHz • Amplitude and Phase: • 10kHz: -92o • 160kHz: -258o • Op-amp Selection • OPA 4140: • 4 channels/package • Noise: 5.1 nV/Hz • Input Bias Current: 0.5pA • Id: 2.0 mA • Vdd max: ± 18 V • SOIC-14 DAC

DAC Resolution, sampling rate, and DR • Resolution • 16-bit • 153 μV • Sampling Rate • Max serial clock frequency = 30 MHz • 24 bit word • Max Sampling Rate ≈ 30MHz/(30cycles/sample) = 1 MSPS • DR (due to quantization) = (6.02dB/bit)*16bits = 96 dB • Alias Rejection: 61.2 dB (assuming 150 kSPS) DAC

DAC Main Schematic Output Format Jumper Quadrature Grounding Options Reconstruction Filters DAC: AD5754 Daisychained DAC

DAC Layout Reconstruction Filters Quadrature Grounding Options Output Format Jumper DAC: AD5754 Daisychained DAC

Connection: External and AFE (“Red” Daughterboard) Interface • SMA connectors for power and data connections • Only 7 connectors total (3 SMA Supplies + 4 USB) Interface

Digital Potentiometers: Feed-through Cancellation Tuning • Digital Potentiometers used to control feedthrough cancellation gains • 4 channels total • 10kΩ maximum resistance per channel • Parallel and series resistors allow adjustment of resistance • Interface: 1 SPI channel, 2 CS • Screw terminals to connect to AFE Feed Through Cancellation Tuning

Power Supplies: 1.8v, 3.3v, and 5v • Regulated 1.8v, 3.3v, and 5v supplies • TPS767D318 • Dual Supply: 3.3v and 1.8v LDO • Output Current: 1.0A per regulator • 2% Tolerance • Power –on reset • unused – maybe I should add this to the reset sources? • Need 3.3v for digital logic • Need 1.8v for ADC core • TPS78650 • 5.0v LDO • 2% Tolerance • Vin: up to 10v (8v used) Power Supply

Layout and Schematic Checks • Schematic • ERC: Electrical Rules Check: No Major Problems • Layout • DRC: Design Rules Check No Errors • LVS: Layout vs. Schematic: No differences Review

DFM Review Review

Complete Main Schematic Review

3D Visualization Top Bottom Review Missing 3D Models: 90 degree SMA Connectors, jumper headers