Advanced CMS DAQ Design and Memory Management in Frontend Chips for Data Processing

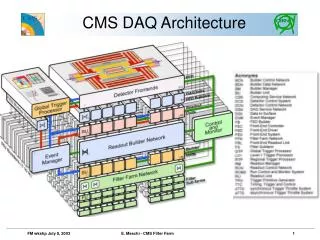

The CMS DAQ system integrates multiple identical parallel DAQ systems, enabling efficient data handling and trigger decisions. At the core, memory pipelines in frontend chips temporarily store incoming data until a trigger pulse indicates which memory cells to read. The system utilizes SLink64 for data transmission and includes features such as test pattern generation and verification. With robust networking solutions and a focus on performance metrics, this architecture achieves high bandwidth and low latency, supporting next-generation data acquisition in particle physics experiments.

Advanced CMS DAQ Design and Memory Management in Frontend Chips for Data Processing

E N D

Presentation Transcript

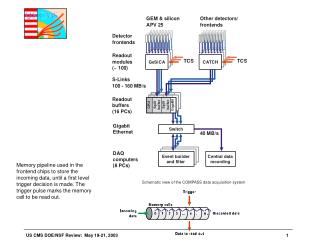

Memory pipeline used in the frontend chips to store the incoming data, until a first level trigger decision is made. The trigger pulse marks the memory cell to be read out.

CMS DAQ Design • Basic principle: • CMS DAQ is a number of functionally identical, parallel, small DAQ systems • A 64x64 system is feasible today

CMS DAQ Design • Basic principle: • CMS DAQ is a number of functionally identical, parallel, small DAQ systems • A 64x64 system is feasible today

Data to Surface: SLink64/FRL • SLink64: From FED to FRL • Test pattern generator in sender card • Test pattern verification in FRL • FRL (Frontend Readout Link) • Multiple firmware versions • Spy functionality • Event generator allows testing DAQ system without operational FEDs

Event Builder:All Commodity Backbone • Commodity Computers + commidity networking (Myrinet/GigabitEthernet) • Myricom’s LANaiX: PCI-X, multiple links, • LANai1XP: since 1 April 2003/LANai2XP: available Oct 2003 Myricom Switches: currently based on Xbar16 Xbar32 under development First products expected 2Q 2004 • Measured bandwidth with two LANai1XP NICs serving as PCI-X DMA engines: • “Grand Champion”: 710 MB/s per bus • Intel “Pluma”: 426 MB/s per bus • i.e. 1.4 GB/s aggregate dual bus “Grand Champion” chipset by Serverworks

Working point GB Ethernet TCP EVB 8x8 • XDAQ 8x8 EVB using gigabit ethernet • Each BU builds 128 evts • Fixed fragment sizes • For fragment size > 4 kB: • Thru /node ~100 MB/s • ie 80% utilization • (Specification is 200 MB/s)

Working point Myricom EVB 8x8 • Full XDAQ 8x8 EVB using Myricom (LanAI9) • software overhead (e.g. EVM included) • Each builder unit builds 128 evts • Log-normal fragment size distribution • At working point(16 kB): • Thu/node = 210 MB/s • (Specification is 200 MB/s)

FU2-8 TIER 0 CSN FU1/ BU0 FDN/ FCN SM Filter Farm Test Stand Dual 2.4 GHz Xeon with 2 GB memory, 40 GB disks and dual on-board GE. Ran empty FU application: load BU output to a max at ~100 MB/s (1 FU/node), ~95 MB/s (2 FU/node) HLT application (small event sample) CPU usage tests ongoing

Building names… Surface DAQ building Underground Area