General

General. Lecturer: Philip Leong (phwl) Tutor: Brian Li (mhli) WWW: http://www.cse.cuhk.edu.hk/~phwl/ceg3470/ceg3470.html Lecture notes will be posted here. They will be updated as we go so look out for changes!

General

E N D

Presentation Transcript

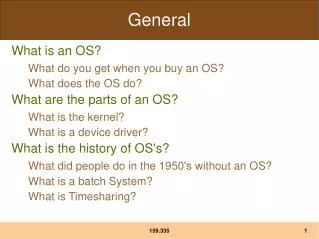

General • Lecturer: Philip Leong (phwl) • Tutor: Brian Li (mhli) • WWW: • http://www.cse.cuhk.edu.hk/~phwl/ceg3470/ceg3470.html • Lecture notes will be posted here. They will be updated as we go so look out for changes! • Tutorial questions will also be posted here. You must hand in solutions every week starting week 2.

Text and References • Text • J.M. Rabaey, “Digital Integrated Circuits”, Prentice 2002. • References • Hodges and Jackson, “Analysis and Design of Digital Integrated Circuits in Deep Submicron Technology”, McGraw-Hill, 3rd Edition 2003 • * Horowitz and Hill, “The Art of Electronics”, Cambridge Uni Press 1989 (* I think every Engineer and Scientist should own this book)

Assessment • Grading Scheme • 50% final exam • 20% assignment • 20% midterm • 10% tutorials

Assumed knowledge • ERG2020 (Digital Systems) • combinatorial and sequential circuits • noise immunity, power supply decoupling, fanin, fanout • ELE1110 (Circuit theory) • diode, MOS, BJT models • large and small signal analyssi • circuit theory

Objectives • Analysis of digital logic gates (CMOS) • TF, noise margin, loading, propagation delay, fanout, power etc • hand calculations, MATLAB models, SPICE • Introduction to CMOS VLSI design • fabrication • design and layout • tradeoffs (low power, speed, cost etc)

Introduction Computers & VLSI Analysis of Digital Logic Gates Devices (revision) Inverters Combinatorial logic Sequential logic CMOS VLSI Manufacturing Low power design Interconnect Timing Arithmetic Design methodologies Lecture schedule (subject to change)