Cache performance

Cache performance. Introduction Primary componentsCache hitsHit ratioCache missesAverage memory access time. Why we use cache memory in a computer?. The primary reason: to improve system performance by reducing the time needed to access memory. . Cache hits. DefinitionEvery time the C

Cache performance

E N D

Presentation Transcript

1. Cache performance CS 147

Prof. Lee

Hai Lin Wu

2. Cache performance Introduction

Primary components

Cache hits

Hit ratio

Cache misses

Average memory access time

3. Why we use cache memory in a computer? The primary reason:

to improve system performance by reducing the time needed to access memory.

4. Cache hits Definition

Every time the CPU accesses memory, it checks the cache. If the requested data is in the cache, the CPU accesses the data in the cache, rather than physical memory; this is a cache hit.

5. A simple example Every time CPU access memory it checks cache first.

CPU

check accesses data

(not in cache)

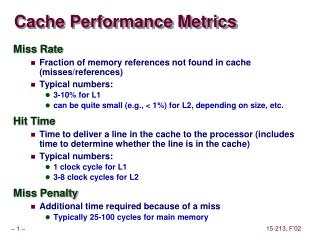

6. Cache misses Definition:

If the data is not in the cache, the CPU accesses the data from main memory(and usually writes the data into the cache as well). This is a cache miss.

7. Hit ratio Definition:

The hit ratio is the percentage of memory accesses that are served from the cache.

Hit Ratio = #of hits / total Strings

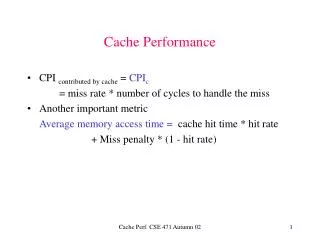

8. Average Memory access time

Symbol:

TM

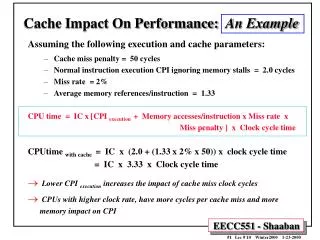

9. Formula for TM

TM = hTc + (1 � h) Tp

*Tc � cache access time

*Tp � physical memory access time

*h -- hit ratio

(Note: Tc and Tp are always given)

10. Relationship between Hit ratios and Average memory access times Table:

So, increase the hit ratio reduce the average memory access time.

11. Calculating the H and TM We will learn how to calculate the H and TM with two different type of cache

* associative cache (FIFO)

* two-way set-associative cache(LRU)

Besides, there is a direct mapped cache

12. Example of associative cache (FIFO)

13. Example cont. Given: Tc = 10ns Tp = 60ns

From the previous table we get:

hits = 7 inputs = 18

** h(hit ratio) = hits/ inputs

= 7/18 = 0.389

** TM = h Tc + (1 � h) Tp

= 0.89*10 + (1 - 0.389) 60

= 40.56 ns

14. Two-way associative set- associative cache(LRU) Hit ratio h = 0.389

TM = 40.56 ns

15. A simple example for LRU Since the example from book is kind of hard to understand, we can see the following simple example.

16. Simple example of LRU 3 frame

10 inputs:

1, 2, 3, 0, 2, 3, 1, 3, 0, 4

17. Construct a table Table

18. Direct mapped cache The hit ratio h = 0.167

The TM = 50.67 ns

19. The End!!

20. BUT� You have to remember How to set up the table for FIFO and LRU

How to calculate

Hit Ratio

Average memory access time

Gook luck on finals!!