Modelos de Computadores Paralelos

310 likes | 577 Views

Modelos de Computadores Paralelos. Ivan Saraiva Silva Sistemas de Processamento Paralelo. Seqüencial, Vetorial, Paralelo. Paral. Funcional. Scalar. Prefetch. Pipeline. Seqüencial. Vetor Explicito. Super posição. Unidades. Mem . p/ Mem. Reg. p/ Reg. SIMD. MIMD. Array Processor.

Modelos de Computadores Paralelos

E N D

Presentation Transcript

Modelos de Computadores Paralelos Ivan Saraiva Silva Sistemas de Processamento Paralelo

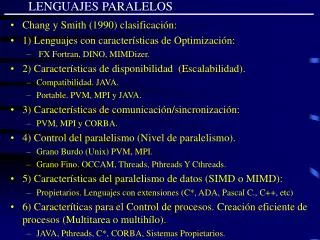

Seqüencial, Vetorial, Paralelo Paral. Funcional Scalar Prefetch Pipeline Seqüencial Vetor Explicito Super posição Unidades Mem. p/ Mem Reg. p/ Reg SIMD MIMD Array Processor Multi- Processadores Associative Processor Multi computadores

SIMD SISD DS PE1 ML IS IS DS CO . . . . . . PO ME IS DS CO I/O DS PE2 ML IS S M CO1 PO1 DS I/O . . . . . . MIMD I/O DS CO1 PO1 IS Classificação de Flynn

Relógio e CPI • Sejam • O período do relógio da máquina • = 1/ a freqüência de operação • Ic o tamanho do programa em nº de instruções • CPI o nº de ciclos por instrução • CPI é um parâmetro importante para medir o desempenho de uma arquitetura • Normalmente calcula um CPI médio

Fator de Desempenho • Define-se o tempo de CPU (T) necessário para executar um programa como T = Ic.CPI. • Porem apenas decodificação e execução é realizada na CPU • T = Ic.(p + m.k).

Fator de Desempenho • conjunto de instruções afeta o Ic o número de ciclos na CPU (p) • A tecnologia dos compiladores afeta Ic, p e m • A implementação da CPU afeta o fator p. • A hierarquia de memória afeta a latência da memória k.

Taxa de MIPS • MIPS – Milhões de Instruções por segundo • Se C é o número de ciclos para execução de um programa • T = Ic.CPI. = C. = C/ = (Ic.CPI)/ • Tem-se ainda que: • Ic.CPI = C CPI = C/Ic, então: MIPS = Ic/(T.106) = /(CPI.106) = .Ic/(CPI.106)

Throughput - Vazão • Throughput indica a vazão de um sistema (Ws) • Indica quantos “programas” o sistemas é capaz de executar por unidade de tempo (prog/seg) • A vazão da CPU é dado por: Wp = /(Ic.CPI) = (MIPS.106)/Ic • Ws < Wp

Multiprocessadores e Multicomputadores • Estes modelos se distinguem pelo uso da memória • Memória comum compartilhada • Memória não compartilhada, distribuída • Multiprocessadores de memória compartilhada • Multicomputadores de memória distribuída

Multiprocessadores • Compartilhamento de memória • Os modelos dependem da localização e do acesso a memória • UMA: Uniform memory access • NUMA: Nonuniform Memory Access • COMO: Cache Only Memory Access

Uniform Memory Access • Memória física é uniformemente compartilhada por todos os processadores • O acesso por qualquer processador a qualquer posição de memória é feito em tempo uniforme • Pode haver cache privado • Diz-se “fortemente acoplado” devido ao alto grau de compartilhamento

Uniform Memory Access • Sistemas podem ser “simétricos” ou “assimétricos” • Simétricos: Processadores tem igual capacidade de rodas o Kernel do OS e fazer I/O • Assimétricos: Processadores mestres executam o OS e fazem I/O, processadores “associados” podem fizer I/O supervisionado

Uniform Memory Access P1 P2 P3 Pn .... Sub-sistema de comunicação (crossbar, barramento, rede multi-estágio) .... I/O MC1 MC2 MC3

L1: Do 10 I = 1, N L2: A(I)= B(I) + C(I) L3: 10 CONTINUE L4: SUM = 0 L5: Do 20 J = 1, N L6: SUM = SUM + A(J) L7: 2O CONTINUE Suponha que L2, L4 e L6 levam um ciclo Tempo de L1, L3, L5 e L7 são ignorados Dados carregados na memória, código na cache Ignorar outros overhead Desempenho Aproximado

L1: Do 10 I = 1, N L2: A(I)= B(I) + C(I) L3: 10 CONTINUE L4: SUM = 0 L5: Do 20 J = 1, N L6: SUM = SUM + A(J) L7: 2O CONTINUE Execução em 2N ciclos em seqüenciais N ciclos para o laço I N ciclos para o laço J Desempenho Aproximado Em um sistema Multiprocessado com M Processadores?

dividir o laço em M seções com L=M/N elementos Assumindo que a comunicação inter-processos leva k ciclos DALL k = 1, M DO 10 I= L(K-1)+1, KL A(I) = B(I) + C(I) 10 CONTINUE SUM(K) = 0 DO 20 J = 1, L SUM = SUM(K) + A(L(K-1) + J) CONTINUE ENDALL Desempenho Aproximado

2L ciclos para laços I e J M somas parciais são produzidas (k + 1)log2M ciclos são necessários para as somas Resultado produzido em: 2(N/M) + (k + 1)log2M Se N = 220 Seqüencial 2N = 221 ciclos MULTIPROCESSADO Se k = 200 e M = 256 213 + 1608 = 9800 ciclos Aceleração 214 Desempenho Aproximado

Nonuniform Memory Access • O tempo de acesso a posições de memória não é uniforme para todas as posições e todos os processadores • Normalmente a memória compartilhada, ou parte dela, é destruída entre os processadores como memória local

C O M U N I C A Ç Ã O ML1 P1 ML2 P2 ML3 P3 . . . . . . MLn Pn Nonuniform Memory Access

.... MGC MGC MGC Sub-Sistema de Comunicação Global P ML P ML C O M U N C O M U N P ML P ML . . . . . . .... . . . . . . P ML P ML Cluster 1 Cluster N Nonuniform Memory Access

Nonuniform Memory Access • Três padrões de acesso a memória são observados • Acesso a memória local Mais rápido • Acesso a memória global Intermediário • Acesso a memória remota Mais lento

Cache Only Memory Access • Trata-se de um caso especial do modelo NUMA, onde as memórias distribuídas são substituídas por cache local • Todas as caches formam o espaço de endereçamento global • O acesso a caches remotas pode ser assistido por diretórios distribuidos

Sub-sistema de comunicação D D D C C C P P P Cache Only Memory Access

Multicomputadores de memória distribuída • O sistema é composto por nós interconectados por uma rede de passagem de mensagem. • Cada nó é computador autônomo • Memórias locais são privadas e acessíveis apenas pelo processador local • NORMA – no-remote-memory-access

Multicomputadores de memória distribuída M M M M M P P P P P Rede com passagem de mensagem P P P P P M M M M M

Parallel Random-Access Machine - PRAM • Modelo teórico de computador • Usado para desenvolvimento de algoritmos e análise de escalabilidade e complexidade • Modelo que desconsidera o tempo de sincronização de de acesso a memória.

Parallel Random-Access Machine - PRAM Fortemente Sincronizado P1 Endereçamento Global Memória Compartilhada P2 P3 Centralizada ou Distribuída . . . Pn

Opera em ciclos sincronizados de: Leitura Computação Escrita Especifica como operações concorrentes são executadas Quatro modelos de acesso a memória Leitura Exclusiva (ER) Escrita Exclusiva (EW) Leitura Concorrente (CR) Escrita Concorrente (CW) Parallel Random-Access Machine - PRAM

Parallel Random-Access Machine - PRAM • CRCW-PRAM: Leituras e escritas concorrentes • Conflitos de escrita são resolvidos com uma política: • (Common) Todas as escritas escrevem o mesmo valor • (Arbitrary) Apenas um dos valores é escrito • (Minimum) O valor do processador de menor índeci permanece • (Priority) Os valores a serem escritos são combinados de alguma forma, soma ou máximo, por exemplo

Exercício • Considere a execução de um programa com 200.000 instruções em uma máquina operando a 40 MHz. • O programa é feito com quatro tipos de instrução (ao lado) • Calcule o CPI médio • Calcule a taxa de MIPS