80x86 Processor Architecture

80x86 Processor Architecture. Rabie A. Ramadan ra.ramadan@uoh.edu.sa http :// www.rabieramadan.org http :// www.rabieramadan.org /classes/2014-2015/micro/. Class Style. Do not think of the exam Just think of the class materials and how much you learn from it

80x86 Processor Architecture

E N D

Presentation Transcript

80x86 Processor Architecture Rabie A. Ramadan ra.ramadan@uoh.edu.sa http://www.rabieramadan.org http://www.rabieramadan.org/classes/2014-2015/micro/

Class Style • Do not think of the exam • Just think of the class materials and how much you learn from it • Feel free to stop me at any time • I do not care how much I teach in class as long as you understand what I am saying • There will be an interactive sessions in class • you solve some of the problems with my help

Your placement • How many rows do we have in class? • How many of you attending? • How many of you in the first row ? • How many of you in the second row? • Take a number based on the following chart. 3 2 1 5 4 7 6 9 8

Applications of Microprocessors • Inside almost everything of our life a microprocessor . • Robotino uses PC 104 board • AMD G-Series Single Core T16R processor • Up to 4GB • SDRAM 128 MB • Wireless LAN access point • Compact flash card (256 MB) with C++ API for controlling Robotino

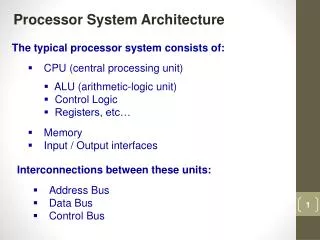

Agenda • The 8086 Registers • The 8086 Memory Addressing • The 8086 Memory Organization

The 8086 Registers • Data Registers: • The data group consists of the AX, BX, CX & DX registers. • Each one of these registers is 16-bit wide, but can be accessed as a byte or a word. Figure 1: Data Registers

The 8086 Registers • Pointer & Index Registers: • The registers in this group are all 16-bits wide. • They can not be accessed as a low or high byte. • They are used as memory pointers. • Register IP can not be accessed by the programmer and has only one function that is to point to the nextinstruction to be fetched by the CPU Keywords: - Stack - Execution cycle Figure 2: Pointer and index registers.

The 8086 Registers • Example 1: Referring to the next Fig 3, if SI=1000H, what is the contents of register AH after executing the instruction MOV AH, [SI]? Figure 3: Memory map of Example 1

The 8086 Registers • Example 1: Referring to the next Fig 3, if SI=1000H, what is the contents of register AH after executing the instruction MOV AH, [SI]? • AH = 26H Move the contents of memory referred to it by SI to the high byte of the Accumulator Figure 3: Memory map of Example 1

The 8086 Registers • Status & Control Flags: • It is a 16-bit register • Six of the flags are statusindicatorsreflecting the properties of the result of the last arithmetic or logicalinstruction. • The 8086 has several instructions that can be used to transfer program control based on the state of these flags, e.g. • JNZ (jump on not zero), • JZ (jump on zero).

The 8086 Registers • Three of the flags can be set or reset directly by the programmer: • TF(trap flag), single step flag • IF(interrupt flag), and • DF(direction flag).

The 8086 Registers • Example 2: If the register AL=7FH and the instruction ADD AL, 1 is executed, what will be the content of the AL register? What will be the values of the status flags?

The 8086 Registers • Example 2: If the register AL=7FH and the instruction ADD AL, 1 is executed, what will be the content of the AL register? What will be the values of the status flags?

The 8086 Registers • Segment Registers: • These registers are used by the CPU to determine the memory segment addresses. • The function of these registers will be explained when discussing the memory addressing. Figure 5: Segment registers.

The 8086 Memory Addressing • Memory Space: • The 8086 processor has 20-bit address bus. • This allows the processor to address ??220 or 1,048,576 different memory locations (1 MB). • Memory Addressing: • the memory space is divided into segments and • the CPU is limited to accessing program instructions and data only from these segments. Figure 6: The 8086 memory space.

The 8086 Memory Addressing • Memory Segments & Segment Registers: • Within the 1MB memory space, the 8086 defines four memory blocks each of size 64K • Code Segment:holds the program instruction codes • Data Segment: stores data for the program • Extra Segment:holds extra data (e.g. shared data). • Stack Segment: used to store interrupt and subroutine return addresses.

The 8086 Memory Addressing • The four segment registers (CS, DS, ES, and SS) are used to point to the beginning of each segment (i.e., location 0 or the base address) as shown in Fig 7. • The four segments need not be defined separately (i.e. they can overlap) as shown in Fig.8. Figure 7: The 8086 memory segments.

The 8086 Memory Addressing • Segments and Offsets : • A combination of a segment address and an offset address accesses a memory location. • All memory addresses must consist of a segment address plus an offset address.

The 8086 Memory Addressing • The segment address, located within one of the segment registers, • defines the beginning address of any 64K-byte memory segment. • The offsetaddress selects any location within the 64Kbyte memory segment. • All memory segments have a length of 64K bytes.

Figure 9: The 8086 memory-addressing, using a segment address plus an offset.

The 8086 Memory Addressing • Segments and Offsets : • Fig 9 shows how the segment plus offset addressing scheme selects a memory location. • This illustration shows a memory segment that begins at location 10000H and ends at location 1FFFFH (64K bytes in length).

The 8086 Memory Addressing • It also shows how an offset address, sometimes called a displacement, of F000H selects location 1F000H in the memory system. • Note that the offset or displacement is the distance above the start of the segment, as shown in Fig 9. • The segment register contains 1000H, yet it addresses a starting segment at location 10000H. From where you got the extra Zero?

The 8086 Memory Addressing • Segments and Offsets : • Note that Each segment registers is only 16 bits wide. • However, the CPU must generate a 20-bit memory address to access a location within the first 1M of memory. • It takes care of this by appending four 0’s (0H)to the low order bits of the segment register.

The 8086 Memory Addressing • This forms a 20-bit memory address, allowing it to access the start of a segment. • For example, when a segment register contains 1200H, it addresses a 64K-byte memory segment beginning at location 12000H. • Likewise, if a segment register contains 1201H, it addresses a memory segment beginning at location 12010H. • Because of the internally appended 0H, memory segments can begin only at a 16-byte boundary (called a paragraph) in the memory system

The 8086 Memory Addressing • Segments and Offsets : • Once the beginning address is known, the endingaddress is found by adding FFFFH (64K). • For example, if a segment register contains 3000H, the first address of the segment is 30000H, and the last address is or 3FFFFH.

The 8086 Memory Addressing • The following table shows several examples of segment register contents and the starting and ending addresses of the memory segments selected by each segment address.

The 8086 Memory Addressing • Segments and Offsets : • The offset address, which is a part of the address, is added to the start of the segment to address a memory location within the memory segment. • For example, if the segment address is 1000H and the offset address is 2000H, the microprocessor addresses memory location 12000H. • The offset address is always added to the starting address of the segment to locate the data. • The segment and offset address is sometimes written as 1000:2000 for a segment address of 1000H with an offset of 2000H.

The 8086 Memory Addressing • Default Segment and Offset Registers: • The 8086 has a set of rules that apply to segments whenever memory is addressed. • These rules, define the segment register and offset register combination. • For example, the codesegmentregister (CS) is always used with the instructionpointer (IP) to address the next instruction in a program.

The 8086 Memory Addressing • The code segment register defines the start of the codesegment and the instructionpointer locates the nextinstruction within the code segment. • This combination (CS:IP) locates the next instruction executed by the CPU. • For example, if CS=1400H and IP=1200H , the microprocessor fetches its next instruction from memory location or 15200H.

The 8086 Memory Addressing • Default Segment and Offset Registers: • Another default combinations is the stack. • Stack data are referenced through the stacksegment register (SS) at the memory location addressed by either the stackpointer (SP) or the pointer (BP). • These combinations are referred to as SS:SP or SS:BP. • For example, SS=2000H and BP=3000H , the CPU addresses memory location 23000H for the stack segment memory location.

The 8086 Memory Addressing • Other defaults of segment and offset combinations are shown in the following table.

The 8086 Memory Addressing • Logical and Physical Addresses: • Addresses within a segment can range from address 0 to address FFFFH. • This corresponds to the 64K length of the segment. • An address within a segment is called an offset, or logical, address.

The 8086 Memory Addressing • For example, logical address0005H in a code segment (CS= B3FF0H) actually corresponds to the real addressB3FF0H + 5 = B3FF5H. • This "real" address is called the physical address. • The physical address is 20 bits long and corresponds to the actual binary code output by the CPU on the address bus lines • The logical address is an offset from location 0 of a given segment.

The 8086 Memory Addressing • Example 3: Calculate the beginning and ending addresses for the data segment, assuming register DS=E000H.

The 8086 Memory Addressing • Example 3: Calculate the beginning and ending addresses for the data segment, assuming register DS=E000H. • Starting Address = E0000H • Ending Address = E0000 + 0FFFF = EFFFFH

The 8086 Memory Addressing • Example 4: Calculate the physical address corresponding to logical address D470H in the extra segment. Repeat for logical address 2D90H in the stack segment. Assume the segment Definitions ES= 52B9H and SS= 5D27H. • Calculating the Physical Address of D470H • Physical Address = 52B90 + 0D470 = 60000H • Calculating the Physical Address of 2D90H • Physical Address = 5D270 + 2D90 = 60000H

The 8086 Memory Organization • The memory is organized as two banks (EvenBankandOddBank) • This allows the processor to access oneword(twobytes) through its 16-bit data bus. Figure 9: The 8086 memory banks.

Assignment to be delivered by next time before the lecture • To: ra.ramadan@uoh.edu.sa • Subject : Micro Assignment 1 • Attachment : word/pdf • Do not forgot your name. Q1: Calculate the beginning and ending addresses for the data segment, assuming register DS=E100H. Q2: what is the content of the interrupt bit when the following code is executed: main (){ int I =0; Math.Pow(5,2); }

Assignment to be delivered by next time before the lecture • Q3: If the register AL=77H and the instruction ADD AL, 1 is executed, what will be the content of the AL register? What will be the values of the status flags?

Assignment to be delivered by next time before the lecture • Q4: Write a survey about different methods to measure the performance of any processor. (2 pages max) ?