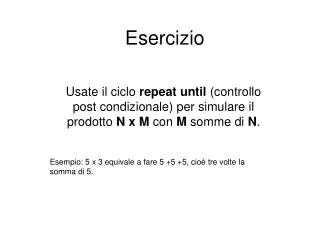

Esercizio

Esercizio.

Esercizio

E N D

Presentation Transcript

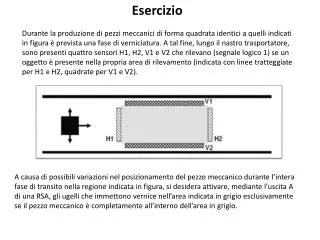

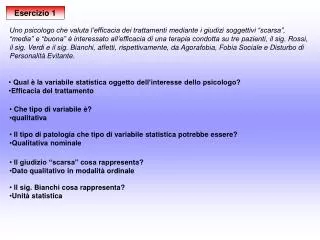

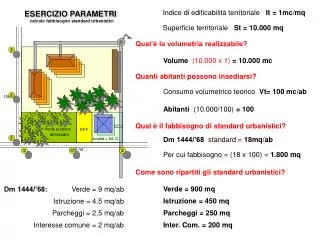

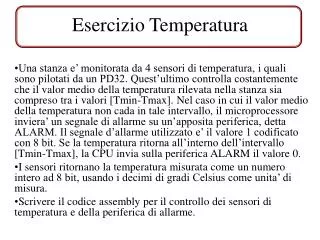

Esercizio Durante la produzione di pezzi meccanici di forma quadrata identici a quelli indicati in figura è prevista una fase di verniciatura. A tal fine, lungo il nastro trasportatore, sono presenti quattro sensori H1, H2, V1 e V2 che rilevano (segnale logico 1) se un oggetto è presente nella propria area di rilevamento (indicata con linee tratteggiate per H1 e H2, quadrate per V1 e V2). A causa di possibili variazioni nel posizionamento del pezzo meccanico durante l’intera fase di transito nella regione indicata in figura, si desidera attivare, mediante l’uscita A di una RSA, gli ugelli che immettono vernice nell’area indicata in grigio esclusivamente se il pezzo meccanico è completamente all’interno dell’area in grigio.

Come si può notare l’esercizio presenta una simmetria, tra i sensori e l’andamento della rete, che può essere sfruttata durante la fase di stesura del diagramma degli stati di Moore. Nello specifico è possibile raggruppare, a due a due, i sensori della rete in modo tale da semplificare in seguito la sintesi della tabella delle transizioni. N.B. questa semplificazione potrebbe portare ad eventuali malfunzionamenti in caso non vengano rispettate determinate condizioni che verranno valutate nelle slide seguenti.

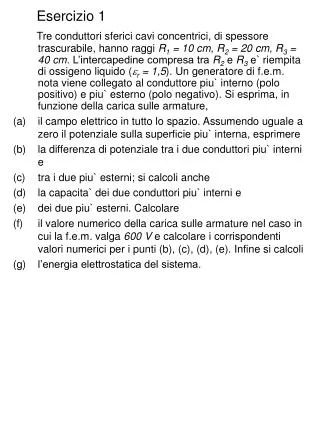

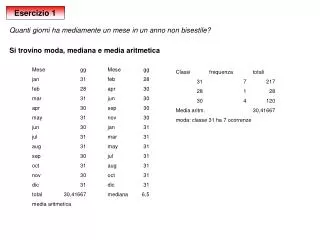

Dal diagramma degli stati si ricava la tabella degli stati su cui verrà effettuata la ricerca degli stati compatibili mediante la tabella triangolare delle implicazioni. x1 00 01 11 10 x2 A A - - B 0 B AC B C - E B 0 C C C F - D 1 D BD D A - G D 0 E - - E - F E B 0 F EG EG F C F G - 0 G BD EGBD - - G - - G D 0 A B C D E F

Dalla tabella triangolare delle implicazioni si ottengono i seguenti stati compatibili: ( [AE] , [BE] , [C] , [DG] , [FG] ) tra cui se ne scelgono in modo da rispettare la condizione di copertura e la condizione di chiusura. x1 00 01 11 10 x2 α α - - β 0 β γ ε β β 0 [A] -> α [BE] -> β [C] -> γ [D] -> δ [FG] -> ε γ γ ε - δ 1 δ α - ε δ 0 ε γ ε ε δ 0 N.B. le classi sono state scelte in modo da garantire, almeno, il funzionamento della rete in caso di posizionamento giusto dell’oggetto sul nastro trasportatore. (un’alternativa perfettamente funzionante è mostrata in seguito)

Sostituendo una codifica binaria univoca agli stati si ottiene la tabella degli stati. x1 x1 y3 y3 00 01 11 10 00 01 11 10 x2 x2 y2 y2 y1 y1 000 000 - - 001 0 100 011 100 100 010 0 001 011 100 001 001 0 101 - - - - - 011 011 100 - 010 1 111 - - - - - 011 000 - 100 010 0 110 - - - - - Evidenziate in rosso si possono notare le corse critiche date da un cambiamento contemporaneo di due o più variabili di stato per una configurazione di ingresso. Riuscire ad eliminare tali corse risulta importante dal momento che la contemporaneità in una rete reale è impossibile a causa dei ritardi intrinseci alla rete stessa.

In questo caso è possibile eliminare le corse critiche sfruttando opportunamente le condizioni di indifferenza: in giallo i cambiamenti apportati alle tabelle. x1 x1 y3 y3 00 01 11 10 00 01 11 10 x2 x2 y2 y2 y1 y1 000 000 100 - 001 0 100 101 100 100 110 0 001 011 000 001 001 0 101 111 - - - - 011 011 010 - 010 1 111 011 - - - - 011 000 100 110 010 0 110 - - 100 010 - Ora che non è più presente alcuna corsa critica che possa compromettere il funzionamento e la stabilità della rete, è possibile procedere con la sintesi delle retroazioni e della funzione d’uscita.

Anche durante la fase di sintesi tornano utili le condizioni di indifferenza, al fine di semplificare e diminuire il numero di implicanti di ogni funzione. x1 x1 y3 y3 00 01 11 10 00 01 11 10 x2 x2 y2 y2 y1 y1 000 000 100 - 001 0 100 101 100 100 110 0 001 011 000 001 001 0 101 111 - - - - 011 011 010 - 010 1 111 011 - - - - 011 000 100 110 010 0 110 - - 100 010 - Y3 = x2!y1 + y3!y2 Y2 = y2y1 + !x1!x2y1 + x1!y3y2 + x1!x2y3 Y1 = !x1!x2y1 + x1x2y1 + x1!x2!y3!y2 + !x1!x2y3 Z = y2y1

Simulazioni Nelle slide successive verranno eseguite alcune simulazioni, al fine di testare in funzionamento della rete con diverse sequenze di combinazioni. Sequenza: 00 – 10 – 11 – 01 – 00 – 10 – 00 A - B - E - F - C - D - A Come si può notare, la simulazione ha esito positivo: l’uscita assume valore ‘1’ solamente quando la rete si trova nello stato C.

Sequenza: 00 – 10 – 00 – 01 – 11 – 10 – 00 – 10 – 11 – 01 – 11 – 10 – 00 A - B - C - F - G - D - A - B - E - F - G - D - A Questa seconda simulazione evidenzia il problema pronosticato in precedenza. Benché la prima parte della sequenza d’ingresso si comporti come previsto, si hanno poi due malfunzionamenti: l’uscita presenta valore ‘1’ in corrispondenza degli stati A, dopo che si sono verificate determinate sequenze. All’atto pratico ciò si rifletterebbe in anomale emissioni di vernice da parte degli ugelli anche quando nessun pezzo si trova all’interno dell’area designata.

Problema La rete è stata progettata rispettando tutte le regole previste per la sintesi di una RSA, eppure il funzionamento non rispecchia la consegna, perché? Il motivo non risiede in una procedura sbagliata , bensì nel grafico tracciato inizialmente: per «semplificare» la sintesi è stato eseguito un raggruppamento degli ingressi che non permette ulteriori collassi; di conseguenza le classi di compatibilità trovate, anche rispettando le condizioni di chiusura e copertura, alterano il corretto andamento della rete che non è più in grado di distinguere alcuni stati. Soluzione La soluzione al problema che verrà proposta risiede in una sintesi in cui il raggruppamento viene omesso: come sarà verificato, la complessità della rete ne risentirà minimamente rispetto alla soluzione precedente, mentre il funzionamento richiesto dalla consegna sarà completamente rispettato.

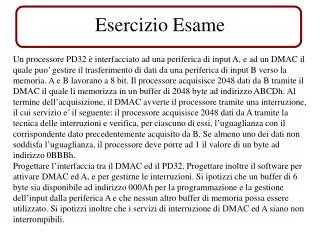

Riprendendo il diagramma degli stati trovato precedentemente e applicando direttamente una codifica binaria agli stati, si ottiene una nuova tabella degli stati. x1 y3 00 01 11 10 x2 y2 x1 y1 000 000 - - 001 0 00 01 11 10 x2 001 011 - 100 001 0 A A - - B 0 011 011 101 - 010 1 B C - E B 0 011 000 - 111 010 0 C C F - D 1 x1 D A - G D 0 y3 00 01 11 10 x2 y2 y1 E - F E B 0 100 - 101 100 001 0 F C F G - 0 101 011 101 111 - - G - - G D 0 111 - - 111 010 - 110 - - - - -

Anche in questo caso risultano esserci corse critiche che vanno eliminate. x1 x1 y3 y3 00 01 11 10 00 01 11 10 x2 x2 y2 y2 y1 y1 000 000 - - 001 0 000 000 - 100 001 0 001 011 - 100 001 0 001 011 - 000 001 0 011 011 101 - 010 1 011 011 111 - 010 1 011 000 - 111 010 0 011 000 - 110 010 0 x1 x1 y3 y3 00 01 11 10 00 01 11 10 x2 x2 y2 y2 y1 y1 100 - 101 100 001 0 100 - 101 100 000 0 101 011 101 111 - 0 101 001 101 111 - 0 111 - - 111 010 0 111 - 101 111 011 0 110 - - - - - 110 - - 111 - -

Infine sintetizziamo uscite e retroazioni sempre avvalendoci delle condizioni di indifferenza (dove possibile). x1 x1 y3 y3 00 01 11 10 00 01 11 10 x2 x2 y2 y2 y1 y1 000 000 - 100 001 0 100 - 101 100 000 0 001 011 - 000 001 0 101 001 101 111 - 0 011 011 111 - 010 1 111 - 101 111 011 0 011 000 - 110 010 0 110 - - 111 - - Y3 = !x1x2 + x1x2!y1 + x2y3 Y2 = !x1!y3y1 + x1y2 + x1y3y1 Y1 = !x1y1 + x1!x2!y3!y2 + !x1y3 + y3y2 + y3!y2!y1 Z = !y3y2y1

Simulazioni Behavioral Sequenza: 00 – 10 – 11 – 01 – 00 – 10 – 00 A - B - E - F - C - D - A Sequenza: 00 – 10 – 00 – 01 – 11 – 10 – 00 – 10 – 11 – 01 – 11 – 10 – 00 A - B - C - F - G - D - A - B - E - F - G - D - A

Simulazioni Post-Route Sequenza: 00 – 10 – 11 – 01 – 00 – 10 – 00 A - B - E - F - C - D - A Sequenza: 00 – 10 – 00 – 01 – 11 – 10 – 00 – 10 – 11 – 01 – 11 – 10 – 00 A - B - C - F - G - D - A - B - E - F - G - D - A

Osservazioni Con quest’ultima sintesi si sono risolti i problemi riscontrati nel primo caso: l’uscita ora assume valore ‘1’ solamente quando si trova nello stato C, qualsiasi siano state le configurazioni d’ingresso che si sono susseguite in precedenza. Come in tutte le reti, di qualsiasi natura, si può notare un piccolo ritardo, in questo caso di 10 ns, dell’uscita rispetto alle entrate nella simulazione post-route: ciò è causato dall’implementazione, simulata, dello schematico in un circuito reale afflitto da ritardi caratteristici della tecnologia impiegata.