Formal Property Qualification

Formal Property Qualification. 學生 : 秦勢翔 陳政揚 執導教授 : 曾王道. 對於仿真的數位電路來說缺乏詳盡的驗證是一個非常大的問題,精確的驗證使用數學上公式來證明此問題的正確性。. 簡介. 流程如下 此圖顯示一個驗證的程序,圖中的 Model Checking 為一個用來判斷結果是否正確的工具, Model 要有足夠的能力決定出設計是否正確. Original program code: a = b | c; Mutated program: a = b & c;. What is mutant??.

Formal Property Qualification

E N D

Presentation Transcript

Formal Property Qualification 學生: 秦勢翔 陳政揚 執導教授:曾王道

對於仿真的數位電路來說缺乏詳盡的驗證是一個非常大的問題,精確的驗證使用數學上公式來證明此問題的正確性。對於仿真的數位電路來說缺乏詳盡的驗證是一個非常大的問題,精確的驗證使用數學上公式來證明此問題的正確性。 簡介

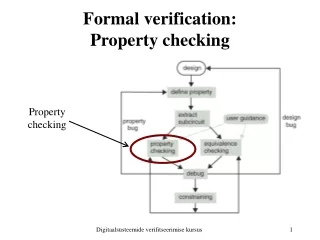

流程如下 此圖顯示一個驗證的程序,圖中的ModelChecking 為一個用來判斷結果是否正確的工具,Model 要有足夠的能力決定出設計是否正確

Original program code: • a = b | c; • Mutated program: • a = b & c; What is mutant??

我們把b|c 更改為 b&c 再去做檢驗,用來確定結果是否為正確,如果我們發現兩個結果為相同,則我稱此結果為“live”,若為不同則稱“killed”,我們的目的是保留所有”live”的結果,並不採用所有”killed”的性質。

我們的目標為找的一個合適的運算方法來判斷此mutation-based 問題的正確性。 Goal

問題描述(Problem Description) 給定兩電路資料M及P,一M的資料與所有P資料做比對,若此M資料與所有P資料皆為滿足,則輸出該M資料,若M資料與P資料有一不符,則不輸出該資料。 (2) 化簡M資料,去除不必要的判斷,增加判斷上的效率。

軟體功能及特性(Functions and Features) 結合一組M資料與一組P資料,合併為PM資料後使用比對程式MARCHDL,該程式為讀取PM資料並判斷中的P資料與M資料,若P資料與M資料為等價電路則輸出滿足結果,若反之,則輸出不滿足結果

貢獻及成果簡述 (Contributions and Results) 可以快速的比對資料,若未來遇到資料量大時,則可快速比對此化簡 是否正確,如此即可使電路圖大大降低製造成本增加產能,也可縮減不必 要的電路,並降低電路的延遲,也可降低功率,也可降低此電路的電路範 圍,促進電路的改革與發展。

Model checking& Input / Output • Input • Design M: written in DIMACS CNF format

Model checking& Input / Output • Input • Property P[1] : written in DIMACS CNF format

Model checking& Input / Output • Input • The concatenation of M and P[1]: (M, P[1]) • Given a (M, P[i]) pair, we denote the model checking as • SAT (M, P[i]) • If the solver returns TRUE • Msatisfies the property P[i] • Otherwise, returns FALSE • M violates P[i]

Model checking& Input / Output • Model checking • foreachP[i], ( 0 < i <= n ) • SAT (M, P[i]) = TRUE • One of the following program changes of the original M • a literal is always positive • a literal is always negative • a literal is negated compared with M

Model checking& Input / Output • Model checking • A Mutant M[2]: which uses program change rule (1)

Model checking& Input / Output • Model checking • A Mutant M[4]: which uses program change rule (3)

Model checking& Input / Output • Input • mutation_file

Model checking& Input / Output • Input • property_file

Model checking& Input / Output • Output • write a program to determine as many “live” mutants as possible • foreachM[k], ( 0 < k <= m) • CheckforeachP[i], ( 0 < i <= n ) • SAT (M[k], P[i]) == TRUE • Are there any approaches to reduce the complexity?

實驗結果 (Experimental Results) 1 工作平台及程式語言(Platform and Programming Language) 工作平台:Ubuntu 程式語言:C++ 2 測試檔輸出 (Test Output) 3.TIME : realuserreport live cada008 17.578s 6.09s 38

參考資料 (References) [1] Properties Incompleteness Evaluation by Functional Verification, Andrea Fedeli, Franco Fummi, and Graziano Pravadelli, IEEE Transactions on Computers, Apr. 2007. [2] Mutation 2000: Uniting the Orthogonal, Jeff Offutt and Roland H. Untch, Mutation 2000: Mutation Testing in the Twentieth and the Twenty First Centuries, pages 45-55, October 2000. [3] A Novel Mutation-Based Validation Paradigm for High-Level Hardware Descriptions, Jorge Campos and Hussain Al-Asaad, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Nov. 2008. [4] DIMACS CNF format: http://www.cs.ubc.ca/~hoos/SATLIB/benchm.html [5] Unified Formal and Dynamic Verification Closure: Can Mutations Bridge the Gap? Mickael Moreau, Olivier Haller, Mirella Negro Marcigaglia, Laurent Martin-Borret, SofieneMejri, DVCon 2009 [6] C++ PRIMER FOURTH EDITION, Stanly B.Lippman , JoseeLajoie , Barbara E.Moo