Understanding DCVSL Gates and Pulse Latches in CMOS Design

This guide covers essential topics in digital circuit design, focusing on the architecture and operational characteristics of DCVSL (Differential Cascode Voltage Swing Logic) gates. It explores the weaknesses that led to the development of CPTL (Complementary Pass-transistor Logic) and details its architecture. Additionally, the document discusses the differences between flip-flops and latches, the implications of input timing on delays, and defines critical parameters like setup time and hold time. It also delves into pulse latches, their advantages, and types of pulse generators, culminating with an introduction to CMOS domino logic and NORA technology.

Understanding DCVSL Gates and Pulse Latches in CMOS Design

E N D

Presentation Transcript

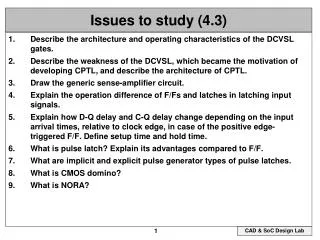

Issues to study (4.3) • Describe the architecture and operating characteristics of the DCVSL gates. • Describe the weakness of the DCVSL, which became the motivation of developing CPTL, and describe the architecture of CPTL. • Draw the generic sense-amplifier circuit. • Explain the operation difference of F/Fs and latches in latching input signals. • Explain how D-Q delay and C-Q delay change depending on the input arrival times, relative to clock edge, in case of the positive edge-triggered F/F. Define setup time and hold time. • What is pulse latch? Explain its advantages compared to F/F. • What are implicit and explicit pulse generator types of pulse latches. • What is CMOS domino? • What is NORA? CAD & SoC Design Lab

![[4.3]a Technical Scope](https://cdn1.slideserve.com/2164856/slide1-dt.jpg)